Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

301 - 320 / 415

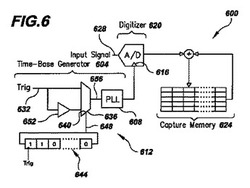

主にデジタルな時間基準発生器を使用する信号完全性測定のシステム及び方法

1以上の被テスト信号のサンプリングを制御するための、独自の時間基準発生技法を利用する信号完全性測定のシステム及び方法である。本開示に従い作成した時間基準発生器は、位相フィルタ及び変調回路を備えており、これらは、シグマデルタ変調器の出力の関数として、高速に変化する位相信号を発生させるものである。この位相フィルタは、該高速に変化する位相信号から所望でない高い周波数の位相成分をフィルタする。フィルタされた該信号は、1以上のサンプラをクロックするために使用され、それによって上記の被テスト信号のサンプリングの事例を生成する。次に、これらサンプリングの事例を、被テスト信号の種類に適した何らかの1以上の様々な技法を使用して分析する。 (もっと読む)

ヒステリシスコンパレータ

【課題】簡単な回路構成でヒステリシス機能およびオフセット機能付きのコンパレータを実現でき、MOSFETのL(ゲート長)またはW(ゲート幅)、あるいはその両方を変えることができるようにする。

【解決手段】入力段に差動増幅回路M1,M2,M3,M4を備えたコンパレータにおいて、前記差動増幅回路M1〜M4の一方の入力回路に用いられているMOSFET(M3またはM4)のゲート長あるいはゲート幅、または該ゲート長とゲート幅の両方を前記コンパレータの出力の状態により変更することによって、入力にヒステリシス特性を持たせる。

(もっと読む)

比較回路、および赤外線受信機

【課題】誤動作防止能力を有しつつ、休止期間の短い入力パルスの周期と同一の周期を有するパルスを出力する能力を向上することができる比較回路を提供する。

【解決手段】比較回路10は、入力パルス信号の切り替わりに応じて、充放電電流により容量105を交互に充放電する充放電回路100と、容量105の容量電圧(Csig)と、第1の閾値電圧(Vth1)、および第1の閾値電圧よりも大きい第2の閾値電圧(Vth2)とをそれぞれ比較することによって、比較結果に応じたパルス信号を生成し、該パルス信号を出力パルス信号のレベルを切り替える信号として出力信号生成回路550に出力するコンパレータ回路200と、上記生成されたパルス信号から、充放電回路100の充放電電流の電流値を調整する信号を生成して充放電回路100に出力することにより、充放電電流の電流値を調整する論理処理回路300とを備える。

(もっと読む)

電磁干渉を減少させる方法及びクロック管理回路、(コヒーレントな周波数クロックの生成及びノンコヒーレントな位相を用いるスペクトル管理)

【課題】クロック動作回路において電磁干渉を減少させる方法を提供する。

【解決手段】この方法では、クロック回路は、少なくとも第1クロック信号及び第2クロック信号を含む。この方法は、第1クロック信号の第1遷移部が、第2クロック信号の対応する第2遷移部と実質的に合っているときを検出する。この方法は更に、第1遷移部が第2遷移部と実質的に合っている場合、第2クロック信号を所定の時間量だけ遅延する。

(もっと読む)

パルス整形およびプログラマブル周波数シンセサイザを備えたSAWデバイスを利用するRFモデム

アナログおよびデジタルパルス変調を送信および受信するための、双方向直接シーケンススペクトル拡散半二重RFモデムが提供される。そのモデムは、送信器および受信器の拡散および逆拡散機能を行うためにSAWベースの相関器を組み込む。プログラマブル周波数シンセサイザは、局部発振器(LO)、IF質問パルスおよびクロック信号を含むモデムにおける種々の信号について周波数源を提供する。アップコンバータ/ダウンコンバータは、所望の周波数帯域への周波数変換を提供する。パルスゲーティングおよび質問パルス整形は、送信された拡散パルスのスペクトル側波帯を低減する。RFモデムは、アナログまたはデジタルパルス送信器および受信器として作動し、そしてOOK、PWM、PPMのようなデータ通信システムにおいて利用可能である。  (もっと読む)

(もっと読む)

PLL回路および記録情報再生装置

【課題】PD出力から微分値を求めると、平均値が“0”の周期関数の微分の平均値はやはり“0”となり、上下バランスが崩れた位相誤差検出特性が得られない。

【解決手段】加算器4203の加算結果ADDである位相誤差絶対値を絶対値比較器4205でしきい値Vthと比較し、当該位相誤差絶対値がしきい値Vthを超えた時点でのPHERR信号の極性と、現時点でのPHERR信号の極性とを不一致検出回路4208で比較する。そして、不一致のときにビットスリップが起きたと判断し、現時点でのPHERR信号の極性を極性反転回路4210で反転し、最終的なPD出力とすることで、上下バランスが崩れた位相誤差検出特性を実現する。

(もっと読む)

シリアル通信用ボーレートジェネレータ

【課題】シリアル通信システムにおいて、ボーレートを補正するノード内のCPUの負担を軽減するシリアル通信回路を提供する。

【解決手段】本発明によるボーレートジェネレータ12は、入力されるシンクフィールド42のビット数を入力順に計数するエッジカウンタ22と、エッジカウンタ22が所定のビット数を計数するまでの時間33を測定するシンクフィールド測定タイマ23と、測定時間33を用いて、シンクフィールド42における1/2ビット期間であるボーレート補正値34を生成するボーレート補正回路24とを具備し、ボーレート補正値34に基づき、シリアル通信のボーレートを決定する。

(もっと読む)

コンパレータ並びにA/D変換器

【課題】高速変換に適したフラッシュ型ADコンバータに使用することができるダイナミック・コンパレータを提供する。

【解決手段】ダイナミック・コンパレータは静止電流が全く流れず、低消費電力動作に最適な回路構成である。リニア領域で動作するNチャネル・トランジスタ1、2、3、4は抵抗値の大きさに応じたラッチ動作を行なうが、ラッチの時定数を微調整可能であるので、遅延時間のばらつき、素子(閾値電圧)のばらつきによるオフセットの影響によって劣化するビット・エラー・レートを改善することができる。

(もっと読む)

シリアル・パラレル変換用の半導体集積回路

【課題】

確実な高速転送を実現可能なシリアル・パラレル変換用の半導体集積回路を提供する。

【解決手段】

シリアル・パラレル変換部2と、シリアル・パラレル変換部2で変換されたパラレルデータDPnをラッチするラッチ回路3と、シリアル入力データDSnと共に送信された入力クロック信号CLKinを位相比較器5の一方の入力端子において受信し、入力クロック信号CLKinを逓倍した逓倍クロック信号CLKm1を電圧制御発振器8で生成して、シリアル・パラレル変換部2に出力し、分周器9で逓倍クロック信号CLKm1を分周して第1分周クロック信号CLKd1を生成するPLL回路4と、逓倍クロック信号CLKm1に同期して第1分周クロック信号CLKd1をラッチし、位相比較器5の他方の入力端子とラッチ回路3に第2分周クロック信号CLKd2として出力するフリップフロップ回路10を備える。

(もっと読む)

クロック供給回路

【課題】 ジッタの低減化が図られたクロック供給回路を提供。

【解決手段】 第1の周波数の第1のクロックで動作する第1の回路ブロック10と、第1のクロックを2逓倍して第2の周波数の第2のクロックを生成する逓倍回路30と、第2の周波数と同一の第3のクロックで動作する第2の回路ブロック20と、第2のクロックと第2の回路ブロック20を経由した第4のクロックの2つのクロックの周波数と位相が一致するようその周波数が制御された第5のクロックを生成するPLL回路40と、第5のクロックを遅延させる遅延回路60からの遅延クロックで動作するモニタ回路23と、第2のクロックとモニタ回路23を経由した第6のクロックとの位相の早遅に応じて第2の回路ブロック20の第1の周波数に同期したジッタを打ち消すようあらかじめジッタが印加された第3のクロックを生成して第2の回路ブロック20に供給するジッタキャンセル回路50とを備えた。

(もっと読む)

位相調整回路装置及びタイミング調整回路システム

【課題】 所定の入力信号または出力信号について製造バラツキや電源電圧や温度変化の影響を少なくし、適切なタイミングでの動作を実現する位相調整回路装置を提供する。

【解決手段】 2つの入力クロック信号の位相差に応じた電圧の位相差検出信号を出力する位相比較回路2と位相差検出信号Sfの電圧値に応じた周波数で発振する基準クロック信号C0を出力する電圧制御発振回路3を有する位相同期回路8、位相の異なる複数のクロック信号C6の1つを選択して位相調整用の参照クロック信号C3として出力する位相選択回路4、及び、第1入力クロック信号C1の信号レベルの変化タイミングを参照クロック信号C3の立ち上がりまたは立ち下がりタイミングに合わせる位相調整を行うフリップフロップ回路5を備え、位相調整後の第1入力クロック信号C4と基準クロック信号C0が外部回路を経由して得られる遅延クロック信号C2を位相比較回路2に入力する。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】半導体集積回路は、位相周波数比較回路とチャージポンプとループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する制御電圧をディジタルコードに変換し、このディジタルコードをこれら複数のCDR回路に分配する。

(もっと読む)

パルス信号発生器及びクロック信号発生器

【課題】発振の成長初期におけるパルス信号のスパイク状波形による悪影響を除去し得るパルス信号発生器及びクロック信号発生器を提供する。

【解決手段】クロック信号CLKの平均の直流電圧値Vdutyが所定の基準値VRを超えたことを検出してこのことを表す第1の状態信号Dinを形成する比較器17と、第1の状態信号Dinが立ち上がった後にブロックしていたクロック信号CLKを出力するDフリップフロップ回路18及びナンドゲート回路14からなる論理回路とを有する。

(もっと読む)

チャージポンプ回路及びこれを用いたPLL回路

【課題】PLL回路の応答特性を調整可能にし、更に、リファレンスリーク(キャリアリーク)を低減する。

【解決手段】位相比較器50内にパルス幅変更部70を設け、外部からセレクト信号SL1,SL2によりセレクタ73,76を切り替えることにより、アップ信号UP又はダウン信号DNのパルス幅を変更させ、チャージポンプ回路80の充電時間を調整することにより、PLL回路の反応特性を高める(不感帯を減少させる)。チャージポンプ回路80内にセレクト部90を設け、外部からセレクト信号SL1,SL2によりスイッチ91〜94を切り替えることにより、チャージ電流Icpによる出力電圧Vcpの持ち上がりによって起きるリファレンスリーク(キャリアリーク)を抑制し、これによってノイズ量を低減する。

(もっと読む)

信号一致検出回路

【課題】信号一致検出回路および該回路で実施する方法。

【解決手段】信号一致検出回路は、第1差動トランジスタ対と、第1差動トランジスタ対と結合する第2差動トランジスタ対と、第2差動トランジスタ対と並列に第1差動トランジスタ対と結合する第3差動トランジスタ対とを含む。回路はまた、第1、第2および第3差動トランジスタ対と結合する第1入力信号端子を含み、この端子は、第1、第2および第3差動トランジスタ対へ送られる第1入力信号を受け取る。回路は更に、第1、第2および第3差動トランジスタ対と結合する第2入力信号端子を含み、この端子は、第1、第2および第3差動トランジスタ対へ送られる第2入力信号を受け取る。回路は更に、第1差動トランジスタ対と結合する電流源を含み、動作時に第2および第3差動トランジスタ対の複数の電流が組み合わされ、組み合わされた電流が、第1入力信号と第2入力信号とが一致するか否かを示す。

(もっと読む)

データスライサ回路、復調段、受信システム、及びシフトキーイング符号化データを復調する方法

本発明は、2つの電圧値(V1、V0)の電圧信号(AF)入力を処理するためのデータスライサ(DS)回路であって、各値が情報の二進の1又は0ビットに対応する変調ベースバンド信号(S)の一特性に割り当てられた値を表すものであり、データスライサ(DS)が、電圧信号(AF)の立ち上がり遷移部分(RE)を検出するための第1の手段(RD1)、電圧信号(AF)の立ち下がり遷移部分(FE)を検出するための第1の手段(FD1)、及び電圧信号(AF)の立ち上がり遷移部分(RE)が検出された場合には二進の0を、電圧信号(AF)の立ち下がり遷移部分(FE)が検出された場合には二進の1を第1のシリアルデジタル信号出力(3)に供給し、又はその逆を行う手段(F1)からなるデータスライサ(DS)回路に関する。 (もっと読む)

コンパレータ

【課題】入力電圧を出力する回路の電流量の変化を抑制し、回路規模の小さいコンパレータを提供する。

【解決手段】コンパレータは、入力電圧及び基準電圧が印加され、入力電圧と、基準電圧と異なる参照電圧とを比較するコンパレータであって、制御電極に入力電圧が印加される第1トランジスタと、第1トランジスタと直列に接続され、入力電圧が参照電圧と同レベルの場合に基準電圧と同レベルとなる、入力電圧に応じた比較電圧を生成する比較電圧生成回路と、制御電極に比較電圧が印加される第2トランジスタ及び制御電極に基準電圧が印加される第3トランジスタにより構成され、比較電圧及び基準電圧の大小関係に応じて動作する差動回路と、差動回路の動作に応じて、入力電圧及び参照電圧の比較結果を出力する出力回路と、を備える。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】設計期間を短縮化でき、半導体集積回路内の電源ノイズおよび製品のEMI問題を軽減できること。

【解決手段】階層化されたブロック間のインターフェースを、クロックとデータを同時に送るソースシンクロナスタイプにする。受信側ブロック22の受信器24にメソクロナスタイプの同期化回路を構成するクロック位相検出器27と、VDL28を備え、ブロック間インターフェースのデータをセットアップ/ホールド違反なしに受信し、受信側ブロック22の内部回路に転送する。

(もっと読む)

データ受信用集積回路

【課題】入力信号が可能な限り小さい歪みを有する出力信号に変換される集積回路を提供する。

【解決手段】データ受信用集積回路は、データ信号(DQ)を、互いに並列に接続される第1および第2の各信号経路に供給される、互いに異なる各入力制御信号(Y、Yb)に変換する。第1の信号経路は、遅延回路(50)および増幅回路(310)を介して集積回路の出力接続部(A300)に接続される比較回路(210)を含む。第2の信号経路は、同様に、インバータ回路(40)および増幅回路(320)を介して集積回路の出力接続部(A300)に接続される比較回路(220)を含む。2つの各増幅回路(310、320)は、互いを駆動するエッジ判別器として機能し、出力接続部(A300)において、データ信号(DQ)と同じデューティサイクルを有する出力信号を歪みが無く生成することを可能にする。

(もっと読む)

クロック遅延補正回路

【課題】クロック分配回路のクロック遅延を補正するクロック遅延補正回路で固定遅延手段を除き、設計時における設計検証を容易にする。

【解決手段】クロック遅延補正回路10は、分配クロックCLKの周期を示す周期データを生成する周期データ生成手段11と、可変遅延時間を持ち分配クロックCLKを遅延して出力クロックCOUT1を生成する可変遅延回路121と、出力クロックCOUT1の位相と基準クロックCREF1の位相とを比較する位相比較回路122と、位相比較回路122の比較結果に従ってカウントUPするカウンタ123とを有し、カウンタ123のカウント値で可変遅延回路121の遅延時間を制御する。

(もっと読む)

301 - 320 / 415

[ Back to top ]