Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

381 - 400 / 415

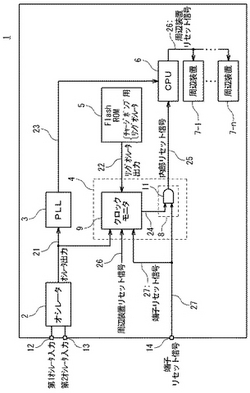

半導体装置

【課題】

オシレータから出力されるクロックに発振異常が発生した場合、その異常に対応してマイクロコンピュータの動作を適切に停止させる。

【解決手段】

発振器と、発振異常検出部とを具備する半導体装置を構成する。発振異常検出部は、その発振器から出力されるクロックを計測して得られたカウント値に基づいてその発振器の周波数を特定する。そして、その周波数が所定の周波数範囲外のときに、発振異常信号を生成する。

(もっと読む)

絶縁型電圧検出回路

【課題】回路構成が単純で、廉価な部品のみにより構成される、簡易的な絶縁型電圧検出回路を提供する。

【解決手段】レジスタ1に設定されたデータに比例したパルス幅の第1のPWM信号を出力するパルス幅変調回路2と、その出力を絶縁して第2のPWM信号として出力する第1の絶縁手段3と、第2のPWM信号をアナログ電圧信号aに変換する変換回路4と、アナログ電圧信号aと検出対象であるアナログ電圧信号bを比較し、2つの極性をもつ比較信号を出力する比較器5と、その比較信号を絶縁して2つの極性を有する第2の比較信号cとして出力する第2の絶縁手段6とを備え、第2の絶縁手段6から出力される第2の比較信号cの結果を所定の周期で検出し、アナログ電圧信号aと検出対象であるアナログ電圧信号bが等しくなるように、レジスタ1に設定するデータをCPU7により増減させるようにした絶縁型電圧検出回路。

(もっと読む)

トリガ信号生成回路および記録装置

【課題】トリガ信号を出力する条件を多様に設定し得るトリガ生成回路を提供する。

【解決手段】記録対象データDiの電気的パラメータが所定条件を満たしたときにトリガ検出信号Sdを出力する複数のトリガ検出器23a〜23hと、各トリガ検出器23a〜23hからそれぞれ出力された各トリガ検出信号Sdに対して論理処理を実行してトリガ信号Stを出力する論理処理回路24とを備えたトリガ信号生成回路11であって、入力した記録対象データDiを指定されたトリガ検出器23に出力するセレクタ回路22を備えている。

(もっと読む)

画像転送調整アダプタ

【課題】画像転送インターフェースにおける画像データとクロック信号との同期を実用状態と同じ条件で簡単に評価できると共に、表示装置側の位相調整にも利用可能な画像転送調整アダプタを提供することを目的とする。

【解決手段】ビデオコントローラと表示装置との間を接続するコネクタにクロック信号を遅延させる遅延器を設け、遅延器の遅延量を外部から可変可能にすることで、画像データとクロック信号との位相調整を行い、表示装置側で受信される画像データ信号のセットアップ時間及びホールド時間を確保出来るようにした。

(もっと読む)

信号伝達回路

【課題】 コストダウンの障害となるLDMOS(Laterally Diffused Metal Oxide Semiconductor)の使用数を削減しコストダウンを図れる信号伝達回路を提供する。

【解決手段】 低電位の回路において、パルス発生器11aは信号入力端HINから入力した信号の正負のエッジを検出し、それぞれのエッジを表すパルス信号をスイッチング素子Q1〜2に出力する。スイッチング素子Q1〜2は電流源Ires1〜2をオン/オフし、LDMOSQ3を介して高電位の回路において、抵抗R3に電流を供給する。抵抗R3は電流地に応じた電圧を両端に発生し、異なる閾値を有するインバータInv1〜2によって、低電位の回路にて入力された信号の正負のエッジが復元され、パルス検出回路12a、RS(Reset-Set)フリップフロップ13、スイッチング素子Q5〜6、抵抗R13〜14によって、入力された信号が復元される。

(もっと読む)

遅延同期ループ及びこれを具備した半導体メモリー装置

【課題】 互いに異なる位相を有した複数個のクロック信号を発生することができる遅延同期ループを提供する。

【解決手段】 クロック信号とフィードバッククロック信号との位相差を検出し、前記位相差によって変化する複数ビットの遅延制御信号を発生する位相検出器12と、前記複数ビットの遅延制御信号に応答して前記クロック信号を遅延させて複数個の出力クロック信号及び前記フィードバッククロック信号を発生する所定個数の縦続接続された第1の遅延セルを具備する第1の遅延器18と、前記複数個の遅延制御信号に応答して反転クロック信号を遅延させて複数個の反転出力クロック信号を発生する所定個数の縦続接続された第2の遅延セルを具備する第2の遅延器22と、前記複数個の出力クロック信号及び前記複数個の反転出力クロック信号の中で関連があるクロック信号を位相混合して補正された複数個の出力クロック信号を発生する位相混合器24とを含む。

(もっと読む)

半導体装置

【課題】 出力信号のAC特性を自動調整する機能を備えた半導体装置を提供する。

【解決手段】 第一及び第二の信号CLK,RDXを複数の端子2a,2bから並行して出力する信号出力部1と、各端子2a,2bから出力される第一の信号CLKと第二の信号RDXの遅延時間を検出する遅延検出部6と、遅延時間に基づいて第一の信号CLKと第二の信号RDXとの間の遅延時間を相殺するように、信号出力部1と端子2aとの間に遅延素子4a〜4dを挿入する遅延制御部7とを備えた。

(もっと読む)

対称性時間/電圧変換回路

本発明は、時間/電圧変換回路に関し、前記時間/電圧変換回路は、構造的に互いに同一であり、その各々がそれぞれの論理制御信号UpおよびDwnを受ける入力部、ならびに論理制御信号VupおよびVdwnの継続時間を表す対応する電圧を与える出力部を有する2つの単純な時間/電圧変換器CTT1およびCTT2と、各々が当該単純な変換器CTT1およびCTT2に接続されている正302および負304の入力部ならびに2つの制御信号UpおよびDwnの間の電圧の差を表す信号Vdiffを与える出力部をもつ微分器ブロックBE2とを備える。微分器ブロックBE2からの出力Vdiffは、積分器ブロックBE3に接続されている。  (もっと読む)

(もっと読む)

ディジタルPWM手段

【課題】 簡単な構成で、短いPWM信号周期でも高い分解能のPWM信号であって、加えて、スイッチング周波数のスペクトル強度を低減するPWM信号を出力するディジタルPWM手段を実現すること。

【解決手段】

2値以上を持つ信号を出力する手段であって、そのうちの1つの値が継続する時間と該値の繰り返す周期の比率が、入力信号に応じて変化するディジタルPWM手段であって、該値の繰り返す周期を固定しないで変化させることによって、簡単な構成で、短いPWM信号周期でも高い分解能のPWM信号であって、加えて、スイッチング周波数のスペクトル強度を低減するPWM信号を出力するディジタルPWM手段を実現できる。

(もっと読む)

容量結合による高電圧レベルのシフト

【課題】簡単な回路構成で、高電圧のレベルシフトを行う。

【解決手段】アース電圧(アース1)を基準とする入力回路(10)と、コンデンサ(C1またはC2)を介して入力回路に結合された別のアース電圧(アース2)を基準とする出力回路(12)とを備える回路構造である。

(もっと読む)

2つのPLLを用いた微小時間差回路及び時間測定回路

【課題】1桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得る。

(もっと読む)

シフトレジスタ及びその駆動方法

本発明は、インバータの入力部をインバータの閾値電位にし、インバータの入力部に容量手段を介してCK信号を入力することで、CK信号は増幅され、その増幅されたCK信号をシフトレジスタに用いる。つまり、インバータの閾値電位を取得することで、トランジスタの特性ばらつきに殆ど影響しないシフトレジスタを提供することができる。  (もっと読む)

(もっと読む)

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】基準信号と内部クロック信号とが同期しているか否かを瞬時に判断することによって検査効率を向上させることができる遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路を提供する。

【解決手段】遅延同期ループ回路に、各タップ信号をクロック信号とする複数のフリップフロップを直列に接続することによってシフトレジスタを形成し、複数のフリップフロップにクロック信号として基準信号からの遅延時間の長いタップ信号から順に入力した場合に、このシフトレジスタから出力される第1の検査信号と、複数のフリップフロップの全てにクロック信号として基準信号を入力した場合に、このシフトレジスタから出力される第2の検査信号とを検出し、これらの第1の検査信号と第2の検査信号との差に基づいて良否を判定することとした。

(もっと読む)

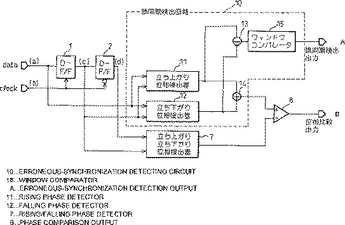

位相誤同期検出回路

位相比較回路に関し、特にデータとクロックとの位相差の比較において、データのデューティが100パーセントからずれたときに生じる位相の誤同期を検出する位相誤同期検出回路を提供する。データとクロックとの位相差を検出する位相比較器において、その位相誤同期検出回路は、データの立ち上がりとクロック位相との位相差を検出してその平均位相差を出力する第1の位相検出部と、データの立ち下がりとクロック位相との位相差を検出してその平均位相差を出力する第2の位相検出部と、前記第1の位相検出部からの平均位相差と前記第2の位相検出部からの平均位相差との差が所定の範囲を超えるときに位相誤同期と判定する位相誤同期判定部と、により構成する。  (もっと読む)

(もっと読む)

可変遅延回路及び半導体集積回路装置

【課題】 高い精度で遅延時間を制御できる可変遅延回路を用いた半導体集積回路装置を提供することを目的とする。

【解決手段】入力クロック信号を遅延させる第1のDLL回路3と、第1のDLL回路よりも高い精度で遅延を制御できる第2のDLL回路10とを有し、第1及び第2のDLL回路の位相比較(31、14)を独立に動作させ、かつ第2のDLL回路の遅延量制御を第1のDLL回路の動作に従属させることで、入力クロック信号に対し所定の位相関係を有する出力クロック信号を出力するように第1及び第2のDLL回路で遅延を与える半導体集積回路装置。

(もっと読む)

等間隔パルス列生成装置および生成方法

【課題】 低消費電力を図り、かつ周波数の変動を生じない精度の良い出力波を得ることのできる位相合成装置および位相合成方法を提供する。

【解決手段】

クロックに同期した位相データと所定電圧値とのクロス点前後の位相データの差分をサンプルホールドした後アナログ値に変換するD/A変換器2と、D/A変換器により変換されたアナログ値を電流に変換する電流源3および該電流を時間的に積分するコンデンサ4からなる積分器5と、積分器の電荷を放電するリセット回路6とを備える直線補間回路を有する位相合成装置およびそれを用いた位相合成方法により、コンデンサのゲイン変化やD/A変換におけるDCオフセット誤差に影響されることなく、ジッタの小さい精度の良い出力波を合成することができる。

(もっと読む)

ギガヘルツ周波数に効率的な遅延同期ループを有する多重位相クロック発生器を備える光学駆動回路

【課題】800MHzまたはそれ以上の周波数を有する入力クロックから、32個の異なる位相を発生させうる遅延同期ループ基盤の多重位相クロック発生器回路を備える光学(ディスク)駆動システムを提供する。

【解決手段】Nで分周されたクロックを、フィードバックループ内のM個の電圧制御される第1遅延素子に出力するための周波数分周器を有する遅延同期ループを備え、分周されていないクロックを遅延させて、M個の多重位相クロックを出力するために、フィードバックループの外部に同じM個の電圧制御される遅延素子を更に備える多重位相クロック発生器。光学駆動システムの光学駆動回路と、光学ディスク上の隣接する溝に書き込まれるマークの重複を防止するための書き込みストラテジを行う方法とを提供し、該回路及び方法は、GHzの周波数範囲で高解像度(例えば、T/32)でスイッチングする多重の書き込みストラテジ波形(チャンネル)を生成する。

(もっと読む)

クロック生成回路

【課題】

所望の分数逓倍、分周クロックを出力し、面積、電力の増大を抑止するクロック生成回路の提供。

【解決手段】

複数段の遅延回路10A1〜10A4を備え、入力される信号の遅延を測定する第1の遅延回路列と、第1の遅延回路列に対し信号伝播方向が逆向きに配置され、複数段の遅延回路10B1〜10B4を備えた遅延再現用の第2の遅延回路列と、を備え、第1の遅延回路列で遅延が検出された位置の遅延回路から出力される信号に基づき、前記遅延が検出された位置に対応する、前記第2の遅延回路列の遅延回路において、遅延回路の出力端子が入力端子に帰還されて閉ループを構成しリング発振回路を構成し、リング発振回路の発振出力が、第2の遅延回路列の出力端子から取り出される。第1の遅延回路列の前段には、制御信号に基づき、入力信号に対する出力信号の位相が可変に制御する位相補間器201、202を備え、第1の遅延回路列は、位相補間器201、202の出力信号の位相差を測定する。

(もっと読む)

駆動状態検出回路

【課題】交流駆動される被駆動体の駆動状態を検出する駆動状態検出回路に関し、付加的な回路を設けることなく、簡単な構成で被駆動体の状態を検出できる駆動状態検出回路を目的とする。

【解決手段】交流駆動される複数の被駆動手段(21、22)の駆動状態検出回路において、該被駆動手段に流れる交流電流を各々検出する電流検出手段(Rs1、Rs2、Rs3、Rs4、D1、D2)と、該電流検出手段で検出された複数の交流検出信号のうち最大検出出力する最大値出力手段(91)と、該出力手段の出力信号に係数乗算する係数乗算手段(94)と、電流検出された複数の交流検出信号を各々係数乗算手段(94)の出力信号とを比較し、各被駆動手段(21、22)の状態に応じた状態信号を出力する比較手段(95、96)と、この複数の状態信号を論理合成する論理合成手段(99)と、この出力に基づいて駆動状態検出信号生成する出力手段(100)とを有する。

(もっと読む)

クロックツリーの動的な平衡方法

【課題】 より多い電流を発生して、クロックがより遅くなるある沈みの時間遅延を補償することができるクロックツリーの動的な平衡方法を提供する。

【解決手段】クロックツリー回路において、制御可能なバッファを前記クロックツリー回路の特定なレベルに差込み、且つ何れか二つの位相の異なるクロックを接収する制御器を提供し、前記制御器の出力バスC[x:0]により制御可能なバッファにおけるPMOS/NMOSの排列を制御する。

(もっと読む)

381 - 400 / 415

[ Back to top ]