Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

341 - 360 / 415

半導体装置

【課題】

従来の半導体装置では、簡単な回路でソフトエラーを検出し、エラーの伝播を防ぐことが困難であった。

【解決手段】

本発明にかかる半導体装置は、複数の論理回路を直列に接続した発振回路10と、複数の論理回路のうち少なくとも2つ以上の論理回路の出力信号が入力され、前記出力信号の間の位相差が所定の位相差の範囲外となる場合に発振回路10を一時停止させ、他のブロックに発振回路10にエラーが発生したことを通知するリセット信号を出力するエラー検出回路20とを有するものである。

(もっと読む)

多相デジタルサンプリングのための装置および方法

【課題】入力信号周波数と基準信号周波数との間の関係を決定する方法および装置を提供する。

【解決手段】本システムは、基準信号から複数の内部基準信号を得る。内部基準信号は、レベル検出回路20aに与えられる。レベル検出回路20aは、入力信号をある期間内にある回数サンプリングする。これらのサンプルに関連付けられた値は、前回の期間からのサンプルの1つの値と同様に記憶される。記憶されたサンプルの相関が取られ、入力信号周波数と基準信号周波数との間の関係が得られる。

(もっと読む)

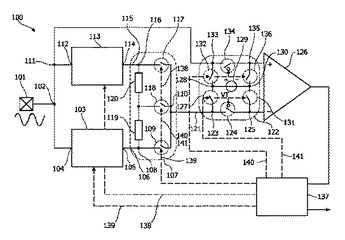

位相検出システム

位相検出システム(100)が、入力端子(101)、第1及び第2ピーク検出器(103,113)、平均化ユニット(107)、オフセットユニット(122)、及び比較器(126)を具えている。入力端子(101)は第1及び第2ピーク検出器(103,113)に結合され、入力信号を位相検出システム(100)に供給する。平均化ユニット(107)は、オフセットユニット(122)と、第1ピーク検出器及び第2ピーク検出器(103,113)の両方との間に結合され、中間信号を発生する。オフセットユニット(122)は入力端子(101)に結合され、信号強度の所定オフセット値を入力信号または中間信号に加えることによって2つの比較可能な信号を発生する。比較器(126)はオフセットユニット(122)に結合され、これら2つの比較可能な信号を比較することによって、入力信号の位相を示す出力信号を発生する。  (もっと読む)

(もっと読む)

パルス信号測定装置及び方法

【課題】パルス信号の入力及びオーバーフローの双方について割り込み信号を発生するタイマを用いてパルス信号の幅や周期を正確に測定可能なパルス信号測定方法を提供する。

【解決手段】リロードレジスタへリロードすると共に割り込み信号を出力し、カウント値がオーバーフローした場合にはリロードレジスタへリロードせずに割り込み信号を出力すると共にオーバーフローフラグをオン状態にするタイマを用いてパルス幅又は周期を測定する際に、割り込み信号を受けてリロードレジスタのカウント値を読み出し(ステップST1)、タイマのオーバーフローフラグの状態を判別し(ステップST2)、オーバーフローフラグがオンしている場合に、リロードレジスタから読み出した今回値と前回値との比較に基づいてパルス信号の入力の有無を判断する(ステップST6)。

(もっと読む)

信号発生装置

【課題】信号発生装置の複数のチャンネルに供給されるクロックを停止することなく、チャンネル間の出力信号位相を制御する。

【解決手段】第1及び第2チャンネル20及び22は、クロック位相シフト回路26及び28と、メモリ、並直列変換回路、DACを有する信号発生ブロック10及び12を具えている。位相比較回路24は、信号発生ブロック10及び12内のメモリから波形データを読み出すための分周クロックを受けて、これらの位相を比較し、位相差信号を生成する。CPUは、この位相差信号を用いてクロック位相シフト回路26及び28を制御し、信号発生ブロック10及び12に供給するクロックの位相シフトを行うことで、第1及び第2チャンネル20及び22の出力信号の位相関係を所望の関係に制御する。

(もっと読む)

振幅制御回路

【課題】 個体やIC面内のばらつきがあっても増幅回路の出力振幅を一定にする。

【解決手段】 増幅回路100からのパルス出力信号がコンパレータ1の−側入力端子とコンパレータ2の+側入力端子、出力信号のハイレベルに対応するVref20がコンパレータ1の+側入力端子、出力信号のロウレベルに対応するVref21が−側入力端子に接続される。/EX-OR3はコンパレータ1とコンパレータ2の出力が同レベルのときにハイレベルを出力する。LPF4は出力信号の振幅が小さ期間においては、/EX-OR3からのハイレベルが入力するとハイレベルとロウレベルの中間レベルに向かって進む信号を出力し、電圧参照回路5はLPF4の出力に応答して電流源の電流を増減するための参照電圧を電流源8に供給する。

(もっと読む)

電力/ダイエリア削減を目的とするクロックスペクトラム拡散(ディザリング)回路の完全デジタル化

【課題】クロック列をデジタル的にスペクトラム拡散する。

【解決手段】クロック列を形成するクロック、及びクロック列を変調し、ディザリングされたクロック列を生成するべく、クロック列の周波数を時間変動分周値によって分周する可変分周器を有する。本回路は更に、周波数変調波形を生成するべくディザリングされたクロック列を蓄積する第1のアキュムレータ、及び位相変調信号を生成するべく、周波数変調波形を蓄積する第2のアキュムレータを有する。本回路は更に、位相変調信号に基づいて、時間変動分周値を計算する位相値計算器、及び最初に述べたクロック列の拡散スペクトラムである第2のクロック列を生成するべく、ディザリングされたクロック列の変調をトラッキング及びフィルタリングするクローズドループ制御回路を有する。

(もっと読む)

半導体装置

【課題】本発明は、低いコストでワンチップLSIと同等のデータ転送速度を達成する半導体システムを提供することを目的とする。

【解決手段】半導体装置は、外部から受信した受信クロック信号を入力として内部クロック信号を供給する内部クロック発生回路と、チップの一辺に配置され該内部クロック信号を出力するクロック送信用端子と、該一辺に配置された複数の入出力端子と、該内部クロック信号に基づいて入出力制御用クロック信号を生成する制御用クロック発生回路と、該入出力制御用クロック信号に同期して該入出力端子を介して外部へのデータ出力及び外部からのデータ取り込みを行う複数の入出力回路と、該制御用クロック発生回路と該複数の入出力回路の各々とを接続する同一長の複数の接続配線を含むことを特徴とする。

(もっと読む)

半導体デバイス

【課題】 クロックやデータの分配において、SKEWを小さくできるとともに、動作依存の消費電力(AC成分)を小さくでき、また、分配回路自身が発生するノイズを抑制できる。

【解決手段】 一又は二以上の回路ブロック10−1〜10−nを有するデジタル回路1aが搭載された半導体デバイスにおいて、クロックを分配するクロック配線20と、データを分配するデータ配線30とを備え、クロック配線20のクロック主経路21が、クロック分岐路22の各分岐点間に接続されたクロック用バッファ25を有し、データ配線30のデータ主経路31が、データ分岐路32の各分岐点間に接続されたデータ用バッファ35を有し、それらクロック用バッファ25及びデータ用バッファ35にBIAS信号を与えるバイアス配線40と、BIAS信号を生成する遅延ロックループ回路(DLL)60とを備えた。

(もっと読む)

スイッチ動作検出回路

【課題】 スイッチ回路から出力されるオン/オフ信号を高精度に検出することが可能なスイッチ動作検出回路を提供できるようにする。

【解決手段】 スイッチ回路1からオン/オフ信号Sinが入力されると、所定の短い期間よりも長く、かつ所定の長い期間よりも短い期間において、前記オン/オフ信号Sinの電位反転が発生したか否かを検出する電位判定検出回路18と、前記電位判定検出回路18の検出結果に基づいて、予め設定された所定波形の開閉検出信号を生成して出力する開閉検出信号出力回路17とを設け、オン/オフ信号Sinを検出する精度を向上させることができるようにする。

(もっと読む)

半導体装置のデータ出力装置及び出力方法

【課題】半導体装置からデータを出力するときに、データ遷移によって発生しうる出力ドライバでのパワーノイズを減少し、高周波数動作で高速データを正確かつ安定的に処理できる半導体装置のデータ出力装置及び出力方法を提供する。

【解決手段】複数のデータを第1〜第4比較部100,200,300,400で並列して比較する。これら比較結果の隣接する比較結果を第1〜第4XOR部110,210,310,410で論理演算し、入力されるデータを反転するか否かを決定し、この決定結果に基づいて、第1〜第4リピーター120,220,320,420でデータを反転または反転せずに出力する。

(もっと読む)

位相同期ループ回路及び位相同期方法

【課題】 電源電圧のレベルが低くなっても高周波数の多様なクロック信号を発生することが可能な位相同期ループ及び方法を提供すること。

【解決手段】 位相同期ループ回路は外部クロック信号と帰還クロック信号を受信し、外部クロック信号の位相が帰還クロック信号の位相より先行するとアップ信号を発生し、外部クロック信号の位相が帰還クロック信号の位相より遅れるとダウン信号を発生する位相検出器と、アップ信号に応答して制御電圧が増加し、ダウン信号に応答して制御電圧を減少するループフィルタ回路と、制御電圧を受信してn(nは4以上の整数)個の内部クロック信号を直接発生する電圧制御発振器回路とを含むこともできる。また、位相同期ループ回路は少なくとも4個のループを含み制御電圧を受信して複数の内部クロック信号を発生する電圧制御発振器回路も含むことができる。

(もっと読む)

位相同期ループ回路での周波数検出器及び周波数エラーの検出方法

【課題】 位相同期ループ回路において周波数エラーを高速で検出できる周波数検出器及び周波数エラーの検出方法を提供する。

【解決手段】 予測されたランレングス信号の予測分布度に基づいて、周波数検出周期の間にサンプルされたRF信号からランレングス信号を検出するランレングス信号検出ユニットと、周波数検出周期の間に、検出されたランレングス信号をカウントする少なくとも一つのカウンタを備えたカウンタユニットと、サンプルされたRF信号のパッシングエッジをカウントして、周波数検出周期を制御するエッジカウンタと、カウンタユニットに含まれたカウンタによりカウントされた値及び所定の基準値を利用して、周波数検出周期の間の周波数エラーを生成する周波数エラー生成ユニットとを備える。

(もっと読む)

データスライサ

【課題】入力信号を適切にスライス可能なデータスライサを実現する。

【解決手段】現在の入力電圧信号の最大値と最小値とだけではなく、入力電圧信号に含まれるヘッダパターンにおける平均電圧と、ヘッダパターン検出完了時のピーク電圧・ボトム電圧とにも基づいて、スライスレベルを算出する。具体的には、スライスレベルをS15、ヘッダパターンの平均電圧をS6、ヘッダパターン検出完了時のピーク電圧をS7、ヘッダパターン検出完了時のボトム電圧をS8、最大電圧検出・保持部に保持された最大電圧をS10、最小電圧検出・保持部に保持された最小電圧をS11として、スライスレベルの電圧値を、S15=S6+(S10+S11)/2−(S7+S8)/2と算出する。

(もっと読む)

クロック発生装置及び半導体集積回路装置

【課題】 高速動作メモリを用いる場合であっても拡散スペクトル・クロック信号を用いて、EMIを効果的に低減することができるクロック発生装置及び半導体集積回路装置を提供する。

【解決手段】 拡散スペクトル・クロック発生器210は、DDR SDRAM112Aの連続アクセスを判定し、DDR SDRAM112Aのデータ読み出し時の連続アクセスでは拡散OFFにする状態判定器220を備える。

(もっと読む)

アナログデジタルコンバータ

【課題】V−F変換を利用したADコンバータであって、変換周波数を高めることなく、高精度にAD変換を行うことが可能なものを実現する。

【解決手段】二本のVCOを設け、両VCOの周期差を利用して主VCOの周期未満のV−F変換値を求める。BASE−VCO1から出力されるパルス信号のパルス数をカウンタ4にて計数することにより、デジタル信号の上位ビットを生成する。一方、下位ビットについては、第3レジスタ10並びに第2および第3減算器11,12により、サンプリング周期ごとに、現在のサンプリング信号Psの活性化時点からBASE−VCO1およびJAW−VCO2の出力の位相一致時点までの間に含まれる、BASE−VCO1の出力のパルス数に基づいて、サンプリング周期内初頭からBASE−VCO1の出力のサンプリング周期内最初のパルス発生までの位相差を算出することにより生成する。

(もっと読む)

信号伝送回路

【課題】 クロック信号を含むいずれの信号であっても、その信号のデューティを維持することができる信号伝送回路を提供する。

【解決手段】 第1の配線経路11および第1のデューティ調整回路12からなる本経路の特性と同一の特性を有する、第2の配線経路22および第2のデューティ調整回路23からなるレプリカ回路を備え、本経路,レプリカ経路に1つのエッジから作られた相補信号を入力し、これら本経路からの信号INRとレプリカ経路からの信号INFとの双方の信号の位相を位相比較器30で比較し、比較結果に応じてそれら双方の信号INR,INFの位相が揃うように制御回路40で第1,第2のデューティ調整回路12,23を制御する。

(もっと読む)

クロック周波数制御装置

【課題】 入力クロックの周波数に対する出力クロックの周波数の比が分数であっても、周期が一定である出力クロックを小規模回路で生成するクロック周波数制御装置を提供する。

【解決手段】 クロック周波数制御装置100は、第1のクロックCK1の周波数と第2のクロックCK2の設定周波数比f2/f1を、約分した後の除算の商mと剰余rと分母dとして記憶する周波数比率記憶部1と、剰余rの累積加算値が分母d以上になることにその値からdを減算するとともに桁上げ信号を出力する累積加算部2と、商mを累積加算部2からの桁上げ信号とともに累積加算する累積加算部3と、CK2の周波数を計数するカウンタ5と、累積加算部3の出力とカウンタ5の出力の差分を算出する差分算出部6と、その差分値に応じて発振周波数を制御するための差分値評価部7Aと、差分値評価部7Aの制御により発振周波数が制御されるCK2出力用VCXO9とを有する。

(もっと読む)

同期回路

【課題】 リセット端子を持たない1:nDEMUXやn:1MUXの複数個を同期させて並列動作させることが可能な同期回路を実現する。

【解決手段】 クロック信号を入力して作動する複数のカウンタIC手段の動作タイミングを一致させる同期回路において、前記複数のカウンタIC手段のうち、基準となるカウンタIC手段のクロック信号と同期対象となる他のカウンタIC手段のクロック信号との位相差を検出する位相差検出手段と、検出された前記位相差に基づいて前記他のカウンタIC手段のクロック信号の位相を制御する位相制御手段と、を備える。

(もっと読む)

パルス幅変調回路及び多相クロック生成回路

【課題】

周波数の微調整を行うことが可能なパルス幅変調回路及び多相クロック生成回路を提供すること。

【解決手段】

本発明にかかるパルス幅変調回路は、基準クロックに基づいて多相クロック信号を生成する多相クロック生成手段と、入力データと、多相クロック信号とに基づいてパルス幅変調信号を生成するパルス幅変調信号生成手段とを備えたパルス幅変調回路であって、多相クロック生成手段は、位相ロックループ回路を有し、多相クロック信号のうち任意のクロック信号を選択し、帰還クロックとして前記位相ロックループ回路に出力するパルス幅変調回路である。このような構成によれば、多相クロック生成回路の生成する多相クロックのクロック周波数が変更可能となり、クロック周波数及びパルス周波数の微調整を行うことが可能となる。

(もっと読む)

341 - 360 / 415

[ Back to top ]