Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

261 - 280 / 415

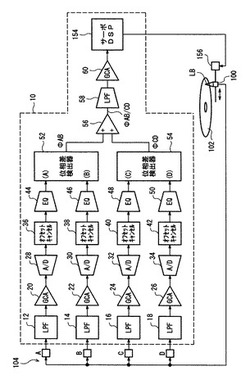

ディジタル信号の位相差検出方法

【課題】比較的低速かつ小規模のディジタル回路により精度の高い位相差検出を行う。

【解決手段】トラッキングサーボ回路10において、入力部のローパスフィルタ(LPF)12〜18および利得制御増幅器(GCA)20〜26はアナログ回路であり、A/D変換器28〜34より後段のオフセット・キャンセル回路36〜42、イコライザ(EQ)44〜50、位相差検出器52,54、加算器56、LPF58、利得制御増幅器(GCA)60およびサーボDSP154はすべてディジタル回路で構成される。両位相差検出器52,54は本発明の位相差検出方法にしたがって両入力信号の位相差を検出する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路の内部でデータ抽出回路のジッタ耐性をテストする。

【解決手段】半導体集積回路10は、第1のクロックを生成するクロック生成回路13と、第1のクロックを位相変調し、かつこの変調されたクロックを用いてジッタが付加されたテストデータを生成するテストデータ生成回路15と、テストデータをサンプリングして再生データを抽出するデータ抽出回路14と、再生データのエラーを検出する検出回路16とを具備する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 PVT変動に起因して周波数変調プロファイルが変化することを防止することができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 入力クロックCLKINと出力クロックCLKOUTの位相を位相比較記30で比較し、その比較結果信号POに基づいて制御回路20で新たな遅延パターンを算出し、その新たな遅延パターンに従って1クロックパルス毎に遅延セル11_0,11_1,11_2,11_3,…,11_N−2,11_N−1,11_Nの段数を切替信号S[0],S[1],S[2],S[3],…,S[N−2],S[N−1],S[N]により切り替えながら入力クロックCLKINを入力させて周波数変調を行なう。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】デューティ補正された遅延固定クロックを生成することができ、1つのDLLだけでもデューティ補正が可能で、かつ、入力されるクロック信号のデューティ比を効率的に補正して出力することができる半導体メモリ装置を提供すること。

【解決手段】遅延固定動作により遅延固定クロックを生成するDLL回路と、前記遅延固定クロックと、その遅延固定クロックの偶数倍に分周したクロックとを用いて、前記遅延固定クロックのデューティ比を補正するデューティ補正回路とを備える半導体メモリ装置を提供する。

(もっと読む)

メータ駆動回路

【課題】 ゲインリダクションメータとゲインメータに同じ構成のメータ駆動回路を使用しても、ゲインリダクションメータにおいて圧縮率の極小値を明確に認識できること。

【解決手段】 メータ駆動回路40は、入力されたエンベロープ信号を反転してエンベロープフォロワ部40bに入力することのできる第1の選択部SWaと、エンベロープフォロワ部40bの出力を反転してゲインリダクションメータに供給することのできる第2の選択部SWbを備えている。

(もっと読む)

クロックスキューコントローラ及びそれを備える集積回路

【課題】クロックスキューを補償することができるコントローラを備える集積回路を提供する。

【解決手段】第1クロックマッシュに入力される第1クロックと第2クロックマッシュに入力される第2クロックとの間のスキューを調節するためのクロックスキューコントローラを備える。クロックスキューコントローラは、第1出力クロックと第2出力クロックとの間の遅延時間に対応するパルス信号を発生するパルス発生器と、パルス信号のパルス幅に対応するデジタル信号を出力するパルス幅検出器と、デジタル信号に対応する時間だけ、第1及び第2クロックのうちのいずれか一つを遅延させるクロック遅延調節器と、を備えて、クロックマッシュの間のクロックスキューを検出し、該検出されたスキューに対応する遅延時間だけクロックマッシュに供給されるクロック等の遅延時間を調節することができる。

(もっと読む)

電圧制御発振回路

【課題】動作が誤発振状態または準安定状態となったことを検出し、誤発振状態または準安定状態から抜け出して正常な発振状態にとすることができるVCOをを提供する。

【解決手段】本発明の電圧制御発振回路は、互いに逆相の差動のクロック信号が入力される差動遅延素子を縦続接続し、バイアス電圧によって差動遅延素子に流れる電流の量を制御することで、該差動のクロック信号の遅延量を制御する差動リングオシレータ型の電圧制御発振回路であり、いずれかの差動遅延素子の差動出力の出力電圧と、異常動作を検出する電圧に設定されたリファレンス電圧とを比較することにより異常発振を検出して検出信号を出力する位相検出部と、差動遅延素子毎に設けられ、検出信号が入力されると、差動出力対間の電位差を増幅するクロスカップル回路とを有している。

(もっと読む)

パルス検出回路、包絡線検出回路、および、電子装置、ならびに、パルス検出方法

【課題】IRのような素子性能の限界に及ぶ超高周波域で良好に動作し消費電力が少なく安価で信頼性が高く且つ通常のCMOS半導体プロセスで製造可能な新たなルス検出回路、包絡線検出回路および電子装置ならびにパルス検出方法を提供することを目的とする。

【解決手段】ゲートおよびドレインを短絡したMOSトランジスタ103(108)が介挿された負帰還路を有する増幅回路20a(20b)と、増幅回路の入力端に一端側が接続され他端側が被検出信号が供給される信号入力端として設定されたコンデンサ105(110)とを含み、信号入力端に供給される被検出信号(Vs)の波形をその変動における一方の極性側のピークレベルが略一定に揃い且つ他方の極性側に向けて当該変動に相応する振幅変化を呈する波形に変換する信号波形変換部と、信号波形変換部10a(10b)の出力信号から被検出信号が担うパルスを検出するパルス検出部とを備える。

(もっと読む)

PLL回路

【課題】入力信号の断、回復状態でも出力の周波数変動を抑制し、周波数精度を維持するPLL回路の提供。

【解決手段】入力を所望周波数に分周する第1分周手段3と、電圧制御発振器7出力を所望周波数に分周する第2分周手段8と、前記第1分周手段3出力と前記第2分周手段出力8間の第1位相比較手段4と、前記第1分周手段3出力と前記第2分周手段8出力の反転の一方の第1選択手段11と、前記第2分周手段8出力と前記第1選択手段11出力間の第2位相比較手段12と、前記第1位相比較手段4出力と、前記第2位相比較手段12出力の一方の第2選択手段6と、入力信号監視手段9と、前記入力信号監視手段9からの監視結果に対して一定時間のタイミングを生成するタイミング生成手段10と、を備え、前記第1選択手段11及び前記第2選択手段6は、前記タイミング生成手段10からの信号状態に従って選択する。

(もっと読む)

半導体装置

【課題】テスト中に所望の位相に対して追随できるテスト回路を備え、安価にDDRifのテストを行うことを目的としている。

【解決手段】本発明における半導体装置は、位相シフト量を決定するDLL200と、テストモード時に所定位相ずらす演算回路300と、位相シフト量を設定するレジスタ11〜16と、設定した位相にシフトして信号の送受信を行う伝送回路10とを備える。伝送回路10は、第1の信号を設定した位相にシフトする位相シフタ1と、テストモード時に第1の信号をループバックする双方向バッファ21と、双方向バッファ21から出力された信号の位相をシフトする位相シフタ2と、第3の信号の位相をシフトする位相シフタ3と、テストモード時に第3の信号をループバックする双方向バッファ22と、双方向バッファ22から出力された信号の位相をシフトする位相シフタ4と、位相シフタ2,4の出力信号を取り出すFIFO30とを備える。

(もっと読む)

クロック出力制御回路、装置、クロック出力制御方法

【課題】クロック供給開始までの時間を短縮すること。

【解決手段】OCXO102の発振器のクロック出力の安定度を確保するために、電源101を入れてから一定時間経過するまで発振器の生成クロックの出力を停止するクロック出力制御回路であって、取得した外部の基準クロックに基づいて発振器の生成クロックの周波数安定度が所定値以内であるか判定し、保証時間経過以前であっても、所定値以内である時点で、生成クロックの出力を許可する。

(もっと読む)

半導体装置、半導体装置のテスト回路、及び試験方法

【課題】デシリアライザにCDR回路を搭載したSerDesによって、スペクトラム拡散クロック発生器の異常の有無を検出する。

【解決手段】本発明による半導体装置10は、スペクトラム拡散クロックに同期して入力されるシリアルデータ4に対しクロックデータリカバリを実行するCDR(Clock Data Recovery)回路16と、CDR回路において追従可能な周波数帯域幅を制御する周波数追従制御回路15とを具備する。

(もっと読む)

電圧比較回路およびそれを用いた電源管理回路

【課題】複数のしきい値電圧を簡易に調節する。

【解決手段】電圧比較回路100は、複数の入力電圧Vin1〜Vinnを、それぞれに設定されたしきい値電圧Vth1〜Vthnと比較し、大小関係を判定する。複数の分圧抵抗対RP1〜RPnは、複数の入力電圧Vin1〜Vinnを、それぞれに設定された分圧比r1〜rnで分圧し、複数の分割電圧Vd1〜Vdnを生成する。基準電圧源10は、調節可能な基準電圧Vrefを生成する。複数のコンパレータCMP1〜CMPnは、基準電圧Vrefを、複数の分圧抵抗対RP1〜RPnにより生成された複数の分割電圧Vd1〜Vdnとそれぞれ比較する。複数のコンパレータCMP1〜CMPnの入力段にそれぞれ設けられた複数の差動対を、半導体基板上に隣接して配置する。

(もっと読む)

通信仲介デバイス

【課題】 アイドル時の消費電力の削減化が図られた通信仲介デバイスを提供する。

【解決手段】 内部クロック生成回路15が、HSアイドル検出回路10による、第1の間隔である125μsよりも短い時間間隔で第2のパケットが到着したことの検出を受けて、480MHzの周波数のクロックCLK1の生成を開始して、HSDLL16,エラスティシティバッファ17,Rxデータデシリアライザ18,Txデータシリアライザ21に供給し、第1のパケットの到着の時間間隔が125μsに戻ったことの検出を受けて、480MHzの周波数のクロックCLK1の生成を停止する。

(もっと読む)

クロック供給装置

【課題】簡単な構成で大きなジッタ削減効果を発現でき、安定したクロックを供給することが可能なクロック供給装置を提供する。

【解決手段】差動のクロックドライバ11と、クロックドライバ111による正相の第1クロックCK1が伝搬される第1クロックライン12と、クロックドライバ112による逆相の第2クロックCK2が伝搬される第2クロックライン13と、インダクタL1とキャパシタC1の並列共振回路14と、を有し、並列共振回路14において、インダクタL1は、一端が第1クロックライン12に接続され、他端が第2クロックライン12に接続されており、キャパシタC1は、第1電極が第1クロックライン12に接続され、第2電極が第2クロックライン13に接続されている。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

システムクロック供給装置及び基準発振器の周波数ずれ判定方法

【課題】システムクロック供給装置及び基準発振器の周波数ずれ判定方法に関し、装置内の基準発振器自身の周波数ずれを、測定用の発振器を用いずに判定し、周波数異常箇所を特定し、異常周波数クロックの送出を防ぐ。

【解決手段】二重化構成(N系及びE系)のシステムクロック供給装置内にそれぞれ備えられたOCXO等の基準発振器(#N,#E)9−1の出力クロックと、システム同期用に通常入力されるリファレンスクロック(例えば8KHz)とを、周波数ずれ測定部(#N,#E)1−1でそれぞれ比較し、所定回数の周波数ずれの発生を誤検出保護回路(#N,#E)1−2で測定し、該両系の測定結果を基に異常個所判定部(#N,#E)1−3で、自系若しくは他系の基準発振器(#N,#E)9−1の出力クロックの周波数ずれ又はリファレンスクロックの異常を判定して異常箇所を特定し、異常箇所を他系に切り替えるよう選択信号を送出する。

(もっと読む)

コンパレータ

【課題】本発明は、オフセット電圧のばらつきを十分に低減することが可能なオフセット付きのコンパレータを提供することを目的とする。

【解決手段】本発明に係るコンパレータは、オフセット電圧Voffsetを定めるオフセット設定部1と、非反転入力電圧Vinpからオフセット電圧Voffsetを減じるオフセット減算部4と、オフセット減算部4の出力電圧(Vinp−Voffset)と反転入力電圧Vinnとの高低に応じて出力論理COMP_OUTを変遷する比較部5とを有して成る構成とされている。

(もっと読む)

多相クロック生成回路

【課題】従来の多相クロック生成回路では、出力クロック信号に任意の周波数プロファイルを設定することができなかった。

【解決手段】本発明にかかる多相クロック生成回路1は、基準クロック信号に基づき多相クロック信号を生成する位相ロックループ回路10と、多相クロック信号の周波数プロファイルを保持し、開始信号に基づき周波数プロファイルの出力を開始し、基準クロック信号に基づき任意の周期で周波数プロファイルを更新する周波数プロファイル保持回路20と、周波数プロファイルに基づいて多相クロック信号のうち任意の位相のクロック信号を選択し、選択したクロック信号を位相ロックループ回路10に帰還させるクロック選択回路30とを有することを特徴とするものである。

(もっと読む)

ノイズ除去回路

【課題】画像処理装置において、同期信号幅をサンプリングし、そのサンプリング値からマスク幅を自動選択することで、画像処理クロックが変った場合でも、マスク期間の再調整を不要にするノイズ除去回路を提供する。

【解決手段】このノイズ除去回路は、同期信号のエッジを検出するエッジ検出回路と、画像データの処理終了を検知し、画像データ完了信号を出力する画像データ処理回路と、1ライン目の前記同期信号のエッジから同期信号幅をカウントし、該カウント値を保持するとともにマスク幅として出力する調整器と、1ライン目は前記同期信号のエッジと前記画像データ完了信号からマスク信号を生成し、2ライン目以降は前記同期信号のエッジと前記マスク幅に応じてマスク信号を生成するマスク信号生成回路と、を備えるものである。

(もっと読む)

261 - 280 / 415

[ Back to top ]