Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

181 - 200 / 415

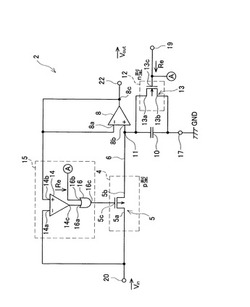

ホールド回路

【課題】 低消費電力化が可能なホールド回路を提供する。

【解決方法】 ピークホールド回路2では、信号保持用のコンデンサ10の一方の電極と入力端子20の間に、スイッチ回路4が形成されている。スイッチ回路4は絶縁ゲート型トランジスタ5を備えており、ゲート電極5cが切換回路15に接続されている。絶縁ゲート型トランジスタ5は切換回路15によって制御され、出力電圧Voutのピーク電圧を保持する際に絶縁ゲート型トランジスタ5を遮断する。コンデンサ10に蓄えられた電荷が変動することなく、出力電圧Voutのピーク電圧が保持される。また、切換回路15はリセット端子19に接続されており、出力電圧Voutをリセットする際に、絶縁ゲート型トランジスタ5を遮断する。入力端子20からGNDへと貫通電流が流れることがない。消費電力が抑制される。

(もっと読む)

発振検出回路

【課題】低電力化を可能とし、リーク電流による誤動作の発生を無くした発振検出回路を提供する。

【解決手段】発振検出回路は、基準電圧源に接続された第1の入力端子と発振回路出力端に接続された第2の入力端子とを有しており、複数のバイポーラトランジスタにより構成される差動回路を採用し、差動回路の出力端に接続され出力端の電位に応じて充電または放電を行う容量素子と、容量素子の電位に基づいて発振信号端の所望の発振状態を検出する検出回路を有する。

(もっと読む)

自動クロック切替回路および方法、ならびに電子機器

【課題】入力されたクロックが適切なものであるか常時監視することができ、クロックの切り替えを常時適切に行うことができるようにする。

【解決手段】判定回路10に固定クロックCLK1を常時入力する。判定回路10では、その常時入力される固定クロックCLK1に基づいて対象クロックCLK2の状態を監視し、対象クロックCLK2が入力停止状態にあるか、もしくは対象クロックCLK2の周波数が所定の周波数の範囲外にあるか否かを判断する。固定クロックCLK1を常時入力としているため、常にクロックの判定を行うことが可能であり、固定クロックCLK1から対象クロックCLK2へ、または対象クロックCLK2から固定クロックCLK1への切り替えが常時可能となる。また、対象クロックCLK2の入力停止状態から所望とするクロックの周波数範囲の判定まで、切れ目のない判定が可能となる。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】遅延固定ループで反映される遅延の程度を測定して読み出し命令に反映することにより、CASレイテンシに対応する最終出力イネーブル信号を生成することができる半導体メモリ装置を提供すること。

【解決手段】本発明の半導体メモリ装置は、遅延固定ループ310と、外部クロック信号に同期化したロック完了情報に応答して基準クロック信号とフィードバッククロック信号との間の遅延の程度を測定し、これを遅延測定値として出力する遅延及び遅延時間測定手段330と、外部クロック信号に同期化した読み出し命令情報を、基準クロック信号とDLLクロック信号との間の遅延の程度に対応する分だけ遅延させ、遅延測定値及びCASレイテンシ情報に対応してDLLクロック信号に同期化させ、最終出力イネーブル信号として生成する出力イネーブル信号生成手段350と、を備える。

(もっと読む)

リング発振器及びこれを用いるマルチ位相クロック補正回路

【課題】クロスカップル構造を有する複数のバッファを備えて発振し、CMLレベルのクロック信号を生成することのできるリング発振器を提供し、また、基準位相クロック信号を補正して希望の周波数、及び互いに予め定められた位相差を有するマルチ位相クロック信号を生成することのできるマルチ位相クロック補正回路を提供する。

【解決手段】 本発明のリング発振器は、各々クロスカップル構造を有し、予め定められた電圧レベルのバイアス電圧が印加されて複数のクロック信号を生成するための複数のバッファ手段を備え、前記複数のクロック信号が、前記バイアス電圧に対応するスイング幅を有する。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

位相検出装置、位相検出方法、再生装置及び再生方法

【課題】

記録媒体から再生される再生信号とクロック信号との位相差を正確に検出することが可能な位相検出装置、位相検出方法、該位相検出装置を備えた再生装置、再生方法を提供する。

【解決手段】

位相同期回路39がリミット位相ディテクタ41を備えるので、例えば図4に示すゼロクロスのタイミング(C)が検出されたとき(ST605でYES)、クロックカウンタ47によるカウント値と所定の値とを比較し(ST606)、カウント値が所定の値より小さいときに(ST606でNO)Cから次のクロックの立ち上がりまでの間、位相カウンタ51をイネブルでない状態とすることができる。つまり、リミット位相ディテクタ41(の位相カウンタ51)の出力を無効にすることができる。この結果、例えばノイズ等の影響を受け易い所定カウント値より小さいパルス幅のRF信号(入力信号)に基づき位相エラー信号が求められることを防止することができる。

(もっと読む)

パワー半導体の駆動回路装置およびそれに用いる信号伝達回路装置

【課題】制御出力信号が制御入力信号を忠実に復元しているか否かを検出、監視する自己診断機能を備えたパワー半導体の駆動回路装置および信号伝達回路装置を提供する。

【課題を解決するための手段】

パワー半導体の駆動回路装置30は、制御入力信号Sinを生成する電子制御装置32と、主経路34と自己診断機能38を有する信号伝達回路装置300と、信号伝達回路装置300からの制御出力信号Soutで駆動されるパワー半導体40とを備える。自己診断機能38は帰還パルス送信回路360、第2信号伝達回路370および第2受信回路380を有する。第2受信回路380では制御出力信号Soutが制御入力信号Sinに一致しているか、または不一致であるかを比較し、比較した結果を比較信号出力端子390に出力する。比較信号出力端子390に出力された信号は電子制御装置32に伝達される。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

半導体装置

【課題】Loopbackテストの際に電圧振幅マージン不足の半導体装置が次工程へと流出するのを防止する。

【解決手段】シリアライザ17は、テストモード期間にクロック信号CLK1に応じてパタン発生器20が出力するパラレルのテストパタン信号をシリアル信号に変換して出力バッファ16よりテスト治具側の外部ループバックパスへ出力する。CPU21は、遅延制御信号DLC1,DLC2によって一方の可変遅延素子VDL1,VDL2の遅延時間を制御する。入力バッファ10の出力であるテストパタン信号VRxとLSIテスタ等より印加される外部基準電圧Vrefとの差動信号VRx1がCDR12に印加され、クロック信号CLK2が生成される。両信号VRx,CLK2の一方の位相が変更されて、外部基準電圧Vrefの値毎にタイミングマージンがチェックされる。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

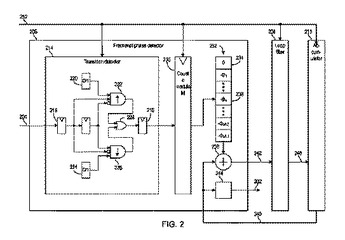

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

周波数異常検出回路

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

信号逓倍器、信号生成器、光送信器および光通信装置

【課題】回路の製造ばらつきや経時変動があっても、クロック信号のデューティ比を精度よく制御すること。

【解決手段】入力部11には、連続して電圧が変化するクロック信号が入力される。供給部12は、一定の参照電圧を供給する。セレクタ13は、入力部11から入力されたクロック信号の電圧が、供給部12によって供給される参照電圧を跨ぐごとに電圧を交互に切り替えたクロック信号を出力する。演算回路14は、入力部11から入力されたクロック信号と、セレクタ13から出力されたクロック信号と、の排他的論理和を出力する。

(もっと読む)

多周波発振装置

【課題】装置の大型化を招くことなく、位相のコヒーレントを保つことができる多周波発振装置を得ることを目的とする。

【解決手段】基準発振器1により発振されるクロックの周波数fclkに応じた周波数切替時間間隔Δtで、周波数の切替を指示する制御信号を出力する周波数切替制御器2と、周波数切替制御器2から制御信号を受ける毎に、基準発振器1により発振されるクロックの周波数fclkに応じた周波数間隔Δfで、出力信号の周波数f1,f2,…,fnを切り替える信号発生器3とを備え、クロックの周波数fclkと、周波数間隔Δfと、周波数切替時間間隔Δtとの間に、式(6)または式(7)の関係が成立しているように構成する。

(もっと読む)

電子回路、電子回路を備えた電子装置及び電子装置のパルス検出方法

【課題】回路が簡単で安定性が高い二乗検出回路。

【解決手段】入力端子101と、入力端子101から入力された信号から平衡信号と不平衡信号とを出力する平衡−不平衡変換器102と、ゲート端子に平衡信号が接続され、ソース端子が接地された第1の電界効果型トランジスタ103と、ゲート端子に不平衡信号が接続され、ソース端子が接地された第2の電界効果型トランジスタ104と、第1の電界効果型トランジスタ103のドレイン端子と第2の電界効果型トランジスタ104のドレイン端子とを相互に接続しドレイン電流を出力する出力端子112と、を含む電流出力部120と、電流出力部120の出力線113と接続され、電流出力部120から出力されるドレイン電流を加算した加算電流を出力する電流加算部121と、を含む電子回路1。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

181 - 200 / 415

[ Back to top ]