Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

221 - 240 / 415

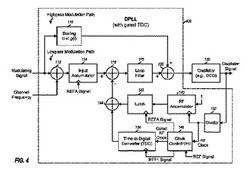

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

アナログスイッチ

【課題】チョッパ型コンパレータ等に適用して、入力電圧及び基準電圧の差が微少な場合にも、アナログスイッチの端子容量による誤差を従来例に比較して抑制することができるアナログスイッチを提供する。

【解決手段】本発明のアナログスイッチは、第1のアナログスイッチと、第1のアナログスイッチに対して並列に接続され、第1のアナログスイッチに比較して、端子容量も電流容量も小さく形成されている第2のアナログスイッチとを有する。

(もっと読む)

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

信号伝達回路

【課題】新たな構成で複数種類の入力信号を1つのトランスを介して入力側から出力側へ伝達することが可能な信号伝達回路を提供することを目的とする。

【解決手段】温度入力信号が立ち上がると、トランス4の1次側コイルに第1のパルス電圧を発生させ、温度入力信号が立ち下がると、1次側コイルに第2のパルス電圧を発生させる1次側回路2と、トランス4の2次側コイルに第1のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち上がらせ、2次側コイルに第2のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち下がらせる2次側回路3とを有して信号伝達回路1を構成し、FAIL入力信号が立ち上がると、1次側コイルに第3又は第4のパルス電圧を発生させ、2次側コイルに第3又は第4のパルス電圧に対応するパルス電圧が発生すると、FAIL出力信号を立ち上がらせる。

(もっと読む)

ノイズフィルタ回路、デッドタイム回路、遅延回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、制御回路、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60;80;100)は、入力信号(IN)に基づく信号を入力する第1のインバータ回路(12;62;82;102)と、入力信号(IN)に基づく信号を入力する第2のインバータ回路(14;64;84;104)と、第1および第2のインバータ回路(12、14;62、64;82、84;102、104)からの信号に基づく信号を、セット信号(S)及びリセット信号(R)として入力するラッチ回路(16;66;86;106)と、を備える。第1および第2のインバータ回路(12、14;62、64;82、84;102、104)のそれぞれは、第1および第2の導電型のトランジスタを含み、第1および第2の導電型のトランジスタの一方の能力は、第1および第2の導電型のトランジスタの他方の能力より低い。

(もっと読む)

半導体装置

【課題】メインスイッチング素子のスイッチングに伴う誤差量を制御することによって、より高精度で信頼性の高い動作が可能な半導体装置の提供を図る。

【解決手段】第1ノードに接続された第1電極S1、第2ノードに接続された第2電極D1、および、該第1および第2電極間の接続を制御する第1制御電極G1を有する少なくとも1つのメインスイッチング素子1と、前記第2ノードに接続される第3電極S2と第4電極D2、および、第2制御電極G2を有し、前記メインスイッチング素子がオンからオフに切り替わるときに生じる電荷をキャンセルするキャンセル用素子2と、を備え、前記キャンセル用素子の駆動を、前記メインスイッチング素子がオンからオフに切り替わるタイミングに対して可変制御するように構成する。

(もっと読む)

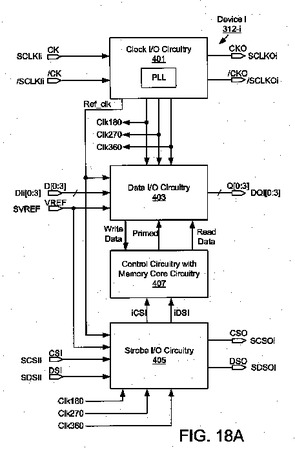

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。  (もっと読む)

(もっと読む)

半導体装置

【課題】消費電流を低減し、差動増幅動作の高速化を図り、かつ小型化を図ることが可能な半導体装置を提供する。

【解決手段】半導体装置101は、制御電極が第1入力ノードに結合されたトランジスタMP1の第2導通電極に結合された第1導通電極と、第1出力ノードに結合された第2導通電極とを有するトランジスタMP3と、制御電極が第2入力ノードに結合されたトランジスタMP2の第2導通電極に結合された第1導通電極と、第2出力ノードに結合された第2導通電極とを有するトランジスタMP4と、第1出力ノード、トランジスタMP3の第2導通電極およびトランジスタMP4の制御電極に結合された第1端子を有する第1のキャパシタCL1と、第2出力ノード、トランジスタMP4の第2導通電極およびトランジスタMP3の制御電極に結合された第1端子を有する第2のキャパシタCL2とを備える。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路においては、品種展開を行う際に追加のフォトマスクが必要となったり、品種の切り替え制御用として専用のボンディングパッドが必要となったりするという課題があった。

【解決手段】クロック入力とデータ入出力とを兼用する少なくとも2個の兼用ボンディングパッド11,12,13と、これらの兼用ボンディングパッドからの入力がクロック信号であるか否かを判定するクロック判定回路14と、このクロック判定回路からの出力に応じて動作する品種を決定する品種選択回路15とを備える。これにより、チップサイズを増加させることなく、また追加のフォトマスクを必要としない半導体製品の品種展開を実現する。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

クロック信号発生回路

【課題】簡単な回路構成により、低速の基準クロックから高速のクロック信号を生成することができ、高速クロック信号の周波数選択の制限を緩和することができるクロック信号発生回路を提供すること。

【解決手段】クロック信号発生回路100は、低速の基準クロック信号S1を発生する基準クロック信号発生回路110と、基本クロック信号発生回路110からの低速の基準クロック信号S1をN1逓倍し、逓倍出力S2を出力するPLL回路130と、PLL回路130の逓倍出力S2を1/N分周し、低速の基準クロック信号S1よりも高速の第2の基準クロック信号S3を出力する分周回路140と、分周回路140の第2の基準クロック信号S3をN2逓倍し、高速のクロック信号である逓倍出力S4を出力するPLL回路150とをこの順序で備える。

(もっと読む)

短絡検出回路

【課題】本発明は、コストアップや電力損失を招くことなく、プッシュプル回路の出力短絡を検出することが可能な短絡検出回路を提供することを目的とする。

【解決手段】本発明に係る短絡検出回路は、パルス信号Vxと同期したダミーパルス信号Vyを生成し、両信号間に所定の位相差が生じているか否かに応じて、OUT1P端子の短絡検出を行う構成とされている。

(もっと読む)

データセンタートラッキング回路及びこれを含む半導体集積回路

【課題】本発明は、外部環境の影響にも安定的に動作し、より向上した電力及び面積効率を具現するデータセンタートラッキング回路及びこれを含む半導体集積回路を提供する。

【解決手段】本発明は、直列連結した複数のクロックバッファーからなり、クロックをバッファーリングして出力信号を出力するクロックツリー;クロックに基づき、出力信号の位相の変化を感知して感知信号を出力する感知部;及び、感知信号に応じて、クロックツリーに供給される電流を調節し、出力信号の位相を調節するディレイ補償部を含む。

(もっと読む)

ノイズ除去回路

【課題】入力信号の“H”,“L”のレベルに拘らず重畳されるパルス性ノイズを除去可能なノイズ除去回路を提供する。

【解決手段】入力信号INが“H”のときに、クロック信号CLKに同期してカウント値CNTをカウントアップさせ、そのカウント値CNTが閾値HTになったときにカウント値CNTを最大値MAXに設定するハイレベル判定部10と、入力信号INが“L”のときに、クロック信号CLKに同期してカウント値CNTをカウントダウンさせ、そのカウント値CNTが閾値LTになったときにカウント値CNTを0に設定するロウレベル判定部20を設ける。更に、カウント値CNTを閾値THと比較し、その比較結果に応じて出力信号OUTを出力する比較器40を設ける。これにより、継続時間が所定のクロック数に満たない入力パルスは除去され、出力信号OUTとして出力されない。

(もっと読む)

A−D変換装置

【課題】電圧−周波数変換方式のA−D変換装置の精度を向上する。

【解決手段】2つの等価な鋸波発生回路18Aおよび18Bと、その2つの鋸波発生回路18Aおよび18Bを交互に切り替えるスイッチ回路19と、を含む電圧制御型発振器24を有する、電圧−周波数変換回路を備える。好ましくは、第1の周期の周期信号を出力する第1の電圧制御型発振器と、第1の周期と異なり、かつ第1の周期と一定の比を保つ第2の周期の周期信号を出力する第2の電圧制御型発振器とを備え、サンプリング周期内に含まれる第1の周期信号の波数に基づいて、入力であるアナログ信号に対応するディジタル信号の上位ビットを算出し、サンプリング信号の活性化時点から第1および第2の周期信号の位相が一致する時点までの間に含まれる周期信号の波数に基づいて、デジタル信号の下位ビットを算出する。

(もっと読む)

データ受信装置およびマイクロコンピュータ

【課題】CR発振回路に温度変化や経年変化が生じても正確な周波数を持つクロック信号を生成する。

【解決手段】CR発振器12の温度を示すA/D変換値とCR発振回路8の逓倍数を決める逓倍数設定値FMULRとを対応付けてEEPROM3に記憶し、A/D変換値(検出温度T)に応じた逓倍数設定値FMULRを読み出してCR発振回路8のレジスタに設定する。通信回路7が同期信号を受信するごとにクロック信号CLKを計数して1ビット長を計測し、その計数値XAと正規の1ビット時間に対する基準周期に基づく基準計数値XBとに基づいて逓倍数設定値FMULRを補正し、補正後の逓倍数設定値FMULRを検出温度Tに対応させてEEPROM3に書き込む。

(もっと読む)

出力装置及び半導体集積装置

【課題】データパターンに関わらず、低消費電流を図ることができる出力装置を提供する。

【解決手段】外部から入力されたデータ信号を差動信号に変換して出力するドライバ回路9からの差動信号を出力する出力装置であって、ドライバ回路9から入力された差動信号を低振幅で差動出力する中継バッファ部11と、中継バッファ部11から出力される差動信号が入力され、振幅を増幅して出力する増幅アンプ部12と、ドライバ回路9に比べて高い駆動力で差動出力をするデータ出力部13とを備える。

(もっと読む)

信号生成装置、直交変調器および直交復調器

【課題】直交変調器において、IQ不整合を補償する技術を提供する。

【解決手段】予め定められた位相差を有する第1信号および第2信号を生成する信号生成装置であって、被変更信号を受け取り、被変更信号のバイアスレベルを、第1信号および第2信号が有するべき位相差に応じて調整するバイアス調整部と、バイアス調整部によりバイアスレベルが調整された被変更信号の論理値の変化点の間隔に応じた位相差を有する第1信号および第2信号を出力する信号出力部と、を備える信号生成装置を提供する。

(もっと読む)

半導体集積回路装置及びパターン検出方法

【課題】レイテンシを軽減する共に、通信速度の向上及び回路面積の低減を実現する。

【解決手段】 入力されたシリアルデータを第1のクロックに基づいて順次取り込んで保持するシフトレジスタSRと、前記シフトレジスタに取り込まれるシリアルデータに含まれる所定のパターンを検出するパターン検出部13a,13b,14a,14b,15a,15bと、前記パターン検出部の検出結果に基づいて前記シフトレジスタに保持されたシリアルデータの出力タイミングを決定する第2のクロック生成部17とを具備したことを特徴とする。

(もっと読む)

半導体記憶装置

【課題】入力データとデータストローブクロックのタイミングにより自動的にデータ入力ストローブ信号の発生タイミングをチューニングする半導体記憶装置を提供する。

【解決手段】入力データとデータストローブクロックの入力タイミングによりデータ入力ストローブ信号の発生タイミングをチューニングする内部チューニング手段と、前記データ入力ストローブ信号に応答して、複数のデータをグローバルラインに伝送するデータ入力センスアンプとを含む。

(もっと読む)

221 - 240 / 415

[ Back to top ]