Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

281 - 300 / 415

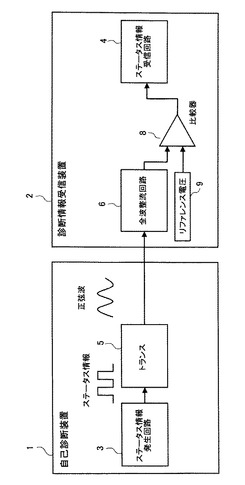

ステータス情報通信システム

【課題】自己診断装置が正常か異常かを判断する際に、ステータス情報発生用クロック信号が一時的に変化しただけでは、自己診断装置が異常であると判断したくない場合にも柔軟に対応できるステータス情報通信システムを得る。

【解決手段】自己の故障診断を行う自己診断装置に設け、自己の故障診断結果であるステータス情報として、正常時にクロック信号を出力し、異常時に前記クロック信号を停止させるステータス情報発生回路と、ステータス情報発生回路のクロック信号を正弦波に変換して出力するトランスと、トランスの出力する正弦波を整流する整流回路と、予め設定した閾値と整流回路の出力とを比較する比較器と、ステータス情報に基づく信号を受信する診断情報受信装置に設け、比較器の出力が入力され、自己診断装置が正常時か異常時かを認識するステータス情報受信回路とを備え、自己診断装置が正常か異常かを判定するものである。

(もっと読む)

遅延信号生成装置、および遅延量制御方法

【課題】短い時間で精度良くデータを記録する。

【解決手段】図1の遅延信号生成装置は、光ディスク記録装置に設けられる。検出部105は、第2遅延信号と第1遅延信号の遅延量の差が検出用パルス信号のパルス幅となるときの第2遅延セレクト信号を求め、その第2遅延セレクト信号に対応する出力位置と第1遅延セレクト信号に対応する出力位置との間にあるバッファの数を、検出結果として出力する。遅延量制御部106は、上記検出結果に基づいて、制御入力信号を求める。記録用ディレイライン101は、上記制御入力信号に応じた遅延量だけ記録用クロックを遅延させる。制御入力信号を求める遅延キャリブレーション動作は、記録中に行われる。

(もっと読む)

フィルタ回路

【課題】単発ノイズを効果的に除去でき、かつ、比較的簡易な回路構成のフィルタ回路を提供すること。

【解決手段】1クロック前の出力データD_OUT(N−1)と、1クロック前の入力データD_IN(N−1)および2クロック前の入力データD_IN(N−2)の双方との差分絶対値S12,S14が、それぞれ減算器12,14にて算出される。セレクタ18によって、S12<S14のときには1クロック前の入力データD_IN(N−1)が現在の出力データD_OUT(N)となり、S12≧S14のときには2クロック前の入力データD_IN(N−2)が現在の出力データD_OUT(N)となる。

(もっと読む)

インタフェイス回路およびインタフェイス回路の動作方法

【課題】不正または異常動作による電子スイッチの誤動作を抑制できるようにする。

【解決手段】異常信号受信回路32は、被検出体検出装置の異常、または、正常動作不能状態の有無を示す異常検知信号をセンサ2より受信し、判定回路31は、異常検知信号により電子スイッチ1の異常、または、正常動作不能状態が検知されているか否かを判定し、電子スイッチ1の異常、または、正常動作不能状態が検知されていると判定した場合、電子スイッチ1からの被検出体の有無を示す検出信号を直前の状態に維持する判定信号を出力するか、または、被検出体が検出されていないことを示す判定信号にして出力し、出力回路33は、判定信号に基づいて、遊技球の有無の状態を示す状態信号を出力する。

(もっと読む)

電力変換装置および電力変換方法

【課題】所望の周波数帯域におけるノイズスペクトルを平坦化することができる電力変換装置および電力変換方法を提供することにある。

【解決手段】

インバータシステム1は、入力される電力を所望の形態に変換するスイッチング素子の開閉動作をデジタル制御する、演算装置を有する制御装置10は、スイッチング素子を開閉するための制御信号を生成する比較器8a、8b、8cに出力するキャリア信号の周波数fcを、離散的かつ周期的に時間変化させるキャリア周波数生成部9を備えている。キャリア周波数生成部9は、キャリア周波数fcの値fc11におけるm11次高調波の周波数m11×fc11と、キャリア周波数fcの他の値fc12におけるm12次高調波の周波数m12×fc12とが、演算装置のクロック周波数Fより低い周波数で重畳しないように、キャリア周波数fcの各値fc11およびfc12を選択した。

(もっと読む)

発振装置および周波数検出装置

【課題】 中心周波数と周波数可変範囲を自在に設定できる高安定、高精度な電圧制御発振器を提供すること。

【解決手段】 第1の水晶発振器の第1の周波数成分と、第2の水晶発振器の第2の周波数成分とを加算器等で加算する等して、所望の中心周波数および所望の可変周波数範囲を作る。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】入力されるシステムクロック信号と反転されたシステムクロック信号との交差点と、基準信号とが一致するように調整可能な回路を備えた半導体メモリ装置を提供すること。

【解決手段】このため本発明は、システムクロック信号と反転されたシステムクロック信号との交差点を基準とする第1クロック信号を生成する第1クロック入力部と、システムクロック信号と基準信号との交差点を基準とする第2クロック信号を生成する第2クロック入力部と、反転されたシステムクロック信号と基準信号との交差点を基準とする第3クロック信号を生成する第3クロック入力部と、遅延制御信号に対応して第1クロック信号を遅延させ遅延クロック信号として出力する遅延部と、遅延クロック信号と第2クロック信号との位相差又は遅延クロック信号と第3クロック信号との位相差に対応して遅延制御信号を出力するクロック遅延調整部とを備える半導体メモリ装置を提供する。

(もっと読む)

比較方法、および、比較回路

【課題】0と1を含む2つの数列間のハミング重みを比較する方法及びその回路、また、2つのデジタル数間の大きさを比較する方法及びその回路が簡単に実現する。

【解決手段】第1数列に含まれる1の数を計数し、第2数列に含まれる1の数を計数して、前記第1数列に含まれる1の数と前記第2数列に含まれる1の数との比率を出力する回路と、前記比率を予め設定した閾値で前記第1数列と前期第2数列間のハミング重みの大小を判別可能とする。

(もっと読む)

半導体装置

【課題】デバイスの使用環境に応じて、動的にコンデンサの容量を変更し、ノイズを低減

する。

【解決手段】第1電源(110)と第2電源(111)との間に設けられたデカップリン

グ容量を有する半導体回路であって、半導体装置のノイズ量を測定する手段(102)と

、ノイズ量の測定結果に応じてデカップリング容量の容量値を可変させる手段(104)

とを備えることを特徴とする。

(もっと読む)

クロック制御回路および半導体集積回路

【課題】クロックの立上りエッジおよび立下りエッジの両エッジをトリガとするフリップフロップに対してクロックを分配するクロックイネーブラを提供する。

【解決手段】排他的論理和ゲート230はクロックCKとラッチ270の不一致を生成する。ラッチ240は、イネーブル信号ENが論理L(無効)にある間に排他的論理和ゲート230からの入力を通し、イネーブル信号が論理H(有効)に遷移するとその直前の入力を保持する。選択器220はラッチ240の出力を選択信号として、クロックの正転信号または反転信号の何れか一方を選択する。ラッチ270は、イネーブル信号が論理Hにある間に選択器220からの入力を通し、イネーブル信号が論理Lに遷移するとその直前の入力を保持する。イネーブル信号が論理Lから論理Hに遷移すると、その停止していたレベルを再起点として出力端子Xからクロックが出力される。

(もっと読む)

周波数比較器、周波数合成器及び関連方法

【課題】電圧に基づいて内部周波数を設定し、これを外部周波数と比較するアナログ周波数比較器と、アナログ周波数比較器の同じ原理でクロック信号を合成するアナログ周波数合成器、及び関連の方法を提供する。

【解決手段】周波数比較器は、第一信号と入力電圧に基づいて基準信号を生成する周波数検出回路と、該入力電圧に基づいて第二信号を生成する周波数発生器と、周波数検出回路と周波数発生器に結合され、基準信号と第二信号の一方に基づいて充電電流をイネーブルして電圧レベルを上げ、更に基準信号と第二信号のもう一方に基づいて放電電流をイネーブルして電圧レベルを下げる電荷ポンプ回路と、電荷ポンプ回路に結合され、該電圧レベルに基づいて第一信号と第二信号間の周波数関係を示す決定論理とを含む。

(もっと読む)

到達ロックループ技術を用いたスペクトラム拡散クロック生成器

ランダム周波数変調および正確な可変周波数拡散を備えるスペクトラム拡散クロック信号到達ロックループ技術を用いた新しい技術が示される。到達ロックループは、正確な拡散制御を有する到達比較器、ループフィルタ、およびVCOの3つのモジュールを含む。到達ロックループは不安定にされ、一定の周波数で発振し、VCOからの高周波出力信号を周波数において拡散するため、最終誤差補正出力上に低周波変調信号を生成する。到達比較器の入力において周波数拡散の周期を小量にリセットするために定時信号に対してサイクルスリップが生成されるように拡散周波数が長くなるまで低周波変調信号のそれぞれのサイクルにおける拡散周波数の周期も、微小ランダム量だけ何サイクルも増加する。  (もっと読む)

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】スケルチ検出回路は、差動信号の電位振幅が、スケルチレベルを超えているかどうかを検出し、その検出信号を出力するピーク検出回路と、検出信号のパルス幅を、そのパルス幅の時間を含めて、差動信号のデータの1周期分の時間以上の時間だけ延長するパルス幅延長回路とを備える。ここで、ピーク検出回路は、差動信号の電位振幅に応じた電位を持つ第1および第2の信号を出力する入力アンプ回路と、入力アンプ回路と同一構成であり、スケルチレベルに相当するリファレンス電圧に応じた電位を持つ第3および第4の信号を出力するレプリカアンプ回路と、第1および第2の信号に応じて流れる合成電流と第3および第4の信号に応じて流れる固定電流とを比較し、その電流差に応じて、差動信号の電位振幅がリファレンス電圧を超えているかどうかを表す検出信号を出力する電流比較回路とを備える。

(もっと読む)

クロック選択回路及びそれを備えたクロックデータリカバリ回路

【課題】クロック選択回路の出力切り替えに起因するグリッチを排除する。

【解決手段】クロック選択回路は、互いに位相のずれた複数のクロック信号を受け、これらクロック信号の中から一つ以上を選択的に出力する2個のクロック選択部(11a、11b)、これらクロック選択部(11a、11b)のいずれか一方を選択し、当該選択した方から出力されたクロック信号を出力するクロック切替部(12)、及びこれらクロック選択部(11a、11b)及びクロック切替部(12)を制御する制御部(13)を備えている。制御部(13)は、2個のクロック選択部(11a、11b)のうちクロック切替部(12)によって選択されていない方に対してクロック信号の再選択を指示し、当該指示後に、クロック切替部(12)に対して出力の切り替えを指示する。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置の遅延固定クロックの出力において、デューティ比を容易に補正して出力可能な遅延固定回路を備える半導体メモリ装置を提供すること。

【解決手段】このため、本発明は、システムクロックを所定の時間遅延させ、遅延固定クロックを出力する遅延固定回路と、該遅延固定クロックのデューティ比を補正して第1クロックを出力するにあたり、前記第1クロックの第2エッジと、前記第1クロックによって生成された第2クロックの第2エッジとのタイミング差に対応して、前記遅延固定クロックのハイレベル区間とローレベル区間との比を調整するデューティ補正回路と、前記第1クロックの第1エッジと前記第2クロックの第1エッジとの位相を合わせるクロック同期回路とを備える半導体メモリ装置を提供する。

(もっと読む)

半導体集積回路

【課題】PLL(Phase Locked Loop)回路を搭載した半導体集積回路において、当該PLL回路の発振安定待ちの時間を有効利用する。

【解決手段】実動作準備期間中に、PLL回路50の帰還ループを遮断した状態で位相比較器51の参照クロック入力部Fpと帰還クロック入力部Frとの双方に基準クロック100を供給して、位相比較器51における位相差の検出不感帯が小さくなるように当該位相比較器51内のリセット信号の遅延を調整する。

(もっと読む)

AD変換器、無線受信機

【課題】消費電力の増大を招くことなく、受動素子の数を削減しチップ占有面積を小さくして低コスト化を図ることが可能なAD変換回路を提供すること。

【解決手段】n次元ベクトルを表すm(n<m<2n)個のアナログ信号のそれぞれを1ビット以上に量子化してm個並列の量子化信号を生成する量子化部と、このm個並列の量子化信号をそれぞれ復号してm個の復号アナログ信号を生成する復号部と、このm個のアナログ信号のそれぞれと上記m個の復号アナログ信号のそれぞれとの差のそれぞれを定数倍してm個の増幅残差信号を出力する残差増幅部と、を有する変換ステージを複数縦続接続して備えた変換部と、この変換部の変換ステージそれぞれにおけるm個並列の量子化信号を該変換ステージの縦続位置に応じた遅延量を考慮して並列位置ごとに合成し、m個並列のディジタル信号を生成する合成部とを具備する。

(もっと読む)

複数のメモリのための信号バッファリングおよびリタイミング回路

【課題】複数のメモリ素子のための信号バッファリングおよびリタイミング回路を提供する。

【解決手段】複数のメモリ素子のための信号バッファリングおよびリタイミング(SBR)回路である。PLLをベースとするクロック発生器によって、受け取ったホスト・クロック信号から1組の位相シフト・クロック信号セットが生成される。複数の位相選択器の各々によって、前記1組の位相シフト・クロック信号セットからサブセットの連続クロック信号が個々に選択される。個々のサブセットの連続クロック信号が、異なる組の1つまたは複数のバーニヤに印加され、個々のバーニヤによって、複数の連続クロック信号の中から1つのクロック信号が個々に選択される。SBR回路は、スキューおよび遅延に関連する比較的厳格な信号タイミング要求事項を満足するように設計することができる。

(もっと読む)

可変周波数多相発振器

【課題】簡単なデューティサイクル制御と、広い周波数レンジと、簡単な周波数調整構成と、低消費電力を備え、集積回路に組み込まれ、且つ、その集積回路を複雑にすることのない多相出力を有する可変周波数多相発振器を提供する装置および方法を提供すること。

【解決手段】多相信号を供給するための可変周波数多相発振器が開示される。この可変周波数多相発振器は、相関器、複数の遅延セル、およびNOR回路を備える。上記相関器のそれぞれは、電流供給部、キャパシタ、コンパレータ、スイッチ、及び論理ユニットを備える。上記複数の遅延セルは、大きな周波数レンジの範囲内で相が相関性を有する多相信号を発生させる。上記多相信号の周波数とデューティサイクルは調整可能である。

(もっと読む)

281 - 300 / 415

[ Back to top ]