Fターム[5J039MM02]の内容

Fターム[5J039MM02]に分類される特許

1 - 20 / 49

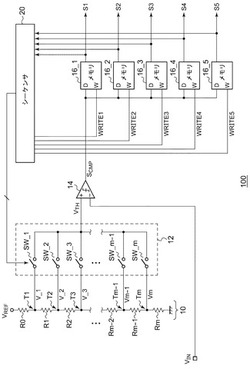

電圧検出回路、それを用いた温度検出回路、電子機器

【課題】回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路を提供する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

位相調整回路及び半導体装置

【課題】回路規模を増やすことなく、スキュー調整及び位相調整を実現する。

【解決手段】本実施形態の本実施形態の位相調整回路12は、第1クロック信号と第2クロック信号との位相差に応じて動作する。位相調整回路12は、調整用駆動素子120と、駆動素子121及び122とを備える。調整用駆動素子120は、入力信号を駆動させ、調整信号を生成する。駆動素子121及び122は、第1クロック信号と第2クロック信号との間に位相差が生じた場合、調整信号と並行した同相及び/又は逆相のクロストーク信号を生成する。

(もっと読む)

ピークホールド回路及びボトムホールド回路

【課題】ピークホールド回路及びボトムホールド回路の検出精度を高め、高温動作における当該回路の検出精度の劣化を抑制すること。

【解決手段】各ゲートに入力端子1と出力端子2が接続される第1の差動入力回路7と、第1のカレントミラー回路10を備える第1の差動増幅回路12と、第1のカレントミラー回路10に流れる電流I1に比例する充電電流I2を生成する第5のトランジスタ13と、ゲートが第1の差動増幅回路12の出力ノード16に接続され、ソースとドレインがそれぞれ第5のトランジスタ13のドレインとキャパシタ17に接続される第6のトランジスタ14と、充電電流I2を充電するキャパシタ17を備え、出力電圧VOUTが入力信号VINのピーク値に近づくに従って充電電流I2を減少させることで、ピークホールド回路の過剰の行き過ぎを抑制し、検出精度を高めた。

(もっと読む)

半導体集積回路装置

【課題】ドレイン電流が温度依存性、プロセスばらつき依存性がないようにMOSFETの基板電圧を制御可能な半導体集積回路装置を提供する。

【解決手段】半導体基板上に複数のN型MOSFETを備えた集積回路本体16Bと、複数のN型MOSFETの一つのドレイン電流をモニタするモニタ部15Bと、ドレイン電流が一定になるよう半導体基板の基板電圧を制御する基板電圧調整部14Bとを備える。モニタ部は、電流源12B及びモニタ用N型MOSFET11Bを有する。基板電圧調整部は、モニタ用N型MOSFETのドレイン電位と基準電位を比較し、その結果に基づく出力電圧をモニタ用N型MOSFETの基板電圧にフィードバックする。モニタ部は、リーク電流キャンセル用N型MOSFETを有し、そのゲートとソースが略同電位である際のソース−ドレイン間の電流をモニタ用N型MOSFETのドレインに加算する。

(もっと読む)

基準周波数発生装置

【課題】比較器が出力する追従誤差に応じて適切な制御を行い、外乱の影響によっても基準周波数信号の精度が低下しない構成の基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、電圧制御発振器と、位相比較器と、制御器と、ファジィ補償器と、を備える。電圧制御発振器は、基準周波数信号を出力する。位相比較器は、基準周波数信号を分周した信号と、リファレンス信号と、を比較して位相差を算出する。制御器は、位相差を考慮して制御電圧信号を電圧制御発振器に出力する。ファジィ補償器は、位相差が急激な変動をしているか否かを、ファジィ理論を用いて判定する。そして、ファジィ補償器は、位相差が急激な変動をしていると判定した場合は、当該位相差が基準周波数信号に影響を及ぼさないように補償値を決定する。

(もっと読む)

増幅回路装置並びにそれを用いた比較回路装置および定電圧出力装置

【課題】印刷などによって低温で生成された場合であっても高速駆動が可能でかつ良好な出力特性を得ることができる増幅回路を提供する。

【解決手段】オペアンプ100は、差動増幅回路110、バイアス回路120、電圧レベルをシフトするレベルシフト回路ユニット150と増幅回路ユニット160からなるソース接地増幅回路140を具備し、すべてのトランジスタを同一プロセスにて簡易に製造できるディプレッション型のトランジスタにて構成する。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

信号処理装置

【課題】 温度によるクロックの変動を抑える。

【解決手段】 クロックを用いて信号を生成する信号処理部と、外部からの入力信号と前記信号処理部から出力された信号との位相差を検出し、前記位相差を示す信号を出力すると共に前記入力信号が無くなるとその直前の位相差の信号を出力する位相差検出部と、温度補償型の発振器からの出力信号に応じて前記位相差検出部からの出力に応じた値をカウントし、前記カウント値に基づいて基準信号を生成するデジタル発振器と、前記デジタル発振器からの基準信号と前記クロックを分周した信号との位相差に応じて前記クロックを生成するクロック生成部とを備える。

(もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】受信した差動信号RX+,RX−の電位振幅が所定値を超えているときその検出信号Vpをパルスとして出力するピーク検出回路11と、ピーク検出回路11から出力する検出信号Vpのパルス幅を差動信号RX+,RX−の少なくとも1周期分延長するパルス幅延長回路12とを備える。ピーク検出回路11は、差動信号RX+,RX−に同一のDCバイアスを与えた後にその差分に対応する電圧信号Vdataを出力する入力差動増幅回路11Aと、入力差動増幅回路11Aのほぼレプリカ回路として構成され、参照電圧Vref’をレベルシフトしたシフト参照電圧Vrefを出力するレプリカ参照電圧生成回路11Bと、電圧信号Vdataとシフト参照電圧Vrefとを比較して検出信号Vpを出力する電圧比較回路11Cと、を備える。

(もっと読む)

クロック信号生成装置および離散時間型回路

【課題】電源電圧、環境温度などの外部変動要因により、離散時間型回路において必要となるクロック信号に変動が生じた場合などにおいて、離散時間型回路が必要とするノンオーバーラップ時間、およびクロック信号のデューティ比を最適に設定することができるクロック信号生成装置を提供すること。

【解決手段】本発明のクロック信号生成装置において、クロック信号遅延算出部は、クロック信号生成回路の可変遅延回路における外部変動要因による遅延特性をモニターする遅延検出回路を有して、N相のクロック信号の遅延量を算出し、クロック信号遅延制御部は、遅延変動データ部に記憶されている外部変動要因をパラメータとした遅延変動データと、算出されたN相のクロック信号の遅延量とに基づいて、可変遅延回路における遅延量を可変するよう構成されている。

(もっと読む)

クロック信号生成装置

【課題】本発明は、温度特性、電源電圧特性、個体バラツキを吸収し、最適なノンオーバーラップ時間を有する2相クロック信号を確実に生成できる信頼性の高いクロック信号生成装置を提供することを目的とする。

【解決手段】本発明のクロック信号生成装置は、ノンオーバーラップクロック信号を使用する負荷回路において使用される2相クロック信号の遅延時間を可変する可変遅延器と、2相クロック信号におけるHレベル区間のノンオーバーラップ時間を検出し、ノンオーバーラップ時間に応じた検出信号を出力するノンオーバーラップ検出器と、ノンオーバーラップ検出器からの検出信号に基づいて可変遅延器を制御する制御信号を生成する制御信号生成部と、を備えている。

(もっと読む)

コンパレータ回路

【課題】フォールデッドカスコード接続の差動増幅段を有するコンパレータにおいて、オフセットの温度依存性を減らし検出精度を向上させる。

【解決手段】ソース共通接続された一対の差動MOSトランジスタを有する差動入力段(11)と、差動MOSトランジスタのドレイン端子にフォールデッドカスコード接続されたカスコード段(12)と、差動入力段とカスコード段に共通に接続された電流回路(Mn11〜Mn13,Mn21〜Mn23)と、カスコード段の出力ノードに接続された出力段(13)とを備えたコンパレータ回路において、前記電流回路は、カスコード段のMOSトランジスタのキャリア移動度の温度特性に起因する動作点の変動をキャンセルするような温度特性を付与された電流を流すように構成した。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力電圧の閾値の変動があっても、ヒステリシス電圧が変化せず、温度特性の影響を受けないヒステリシスコンパレータを提供する。

【解決手段】入力端子INとグランドとの間に接続された抵抗2,3は、入力電圧Vinに対応する電圧を発生し、コンパレータ1の入力端子に与える。コンパレータ1が“H”を出力しているとき、抵抗8にはPMOS6のドレイン電流が流れる。PMOS6のドレイン電流に相当するPMOS4のドレイン電流が抵抗2及び抵抗3の接続点に与えられることにより、ヒステリシス電圧が設定される。温度が変化して抵抗2,3,8の抵抗値が変化しても、PMOS4のドレイン電流が抵抗2及び抵抗3の接続点に与えられることにより設定されるヒステリシス電圧の値は、変化しない。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

電圧比較回路、その電圧比較回路を有する半導体集積回路及び電子機器

【課題】しきい値のばらつきを低減させ、入力される2信号の間に所定のオフセット電圧が発生したことを検出する高速かつ高精度なオフセット付きの電圧比較回路、その電圧比較回路を有する半導体集積回路及び電子機器を得る。

【解決手段】定電流回路12と差動入力回路11の一方の入力トランジスタM1との間に接続された抵抗R1を備え、電流制御回路4によって、該抵抗R1の両端電圧差が基準電圧Vrefの所定値Vaで一定になるように、各入力トランジスタM1及びM2にバイアス電流を供給する定電流回路12をなすPMOSトランジスタM3から出力される電流が制御されるようにした。

(もっと読む)

1 - 20 / 49

[ Back to top ]