Fターム[5J055FX05]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 帰還を行うもの (2,113) | 電気信号に変えられる現象、物理量 (2,102) | 電圧値 (1,457)

Fターム[5J055FX05]に分類される特許

101 - 120 / 1,457

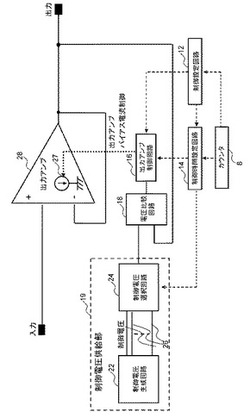

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S3に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。伝送路27のレベルは、トランジスタT1のゲートと外部端子P2とをACカップリングするキャパシタC1により、キャパシタC1の容量値に応じた傾きで立ち下がる。プルダウン回路44は、外部端子P2の電位に応じて、トランジスタT1のゲート電圧をプルダウンする。

(もっと読む)

半導体スイッチング素子の駆動回路

【課題】駆動電圧の印加に制限があるスイッチング素子を高い周波数で高速にスイッチングできる半導体スイッチング素子の駆動回路を提供する。

【解決手段】ダイオードDa1及びスイッチSa1,スイッチSa2及びダイオードDa2で正側,負側直列回路を夫々構成し、コンデンサC1,C2を正側,負側直列回路に夫々並列に接続し、スイッチSa1,Sa2によりゲート駆動用電源3とコンデンサC1,C2の間の接続形態を切替える。スイッチS1及びS2の共通接続点とFET1のゲートとの間に抵抗素子Rgを接続し、前記ゲートとゲート駆動用電源3の正側端子との間にスイッチS3を配置する。通電制御回路4は、スイッチSa1,Sa2,S1〜S3を制御してコンデンサC1,C2を充電する経路,FET1のゲートを充電する経路,ゲートの電位が電圧VGを超えようとする際にゲート駆動用電源3に還流電流を流す経路と、FET1のゲートを放電する経路を形成する。

(もっと読む)

電子装置

【課題】電流制御用トランジスタ、電流検出用抵抗及びオフ駆動用スイッチング素子の少なくともいずれかの異常を検出できる電子装置を提供する。

【解決手段】制御回路は、正常時のミラー期間Tmの終了時t4におけるIGBT110dのゲート電圧がミラー電圧Vmより高い場合、電流制御用FET121aのショート故障、又は、電流検出用抵抗121bのショート故障が発生していると判断する。具体的には、IGBT110dのゲート電圧の立ち上がり時t2を基準として、所定時間T1経過後のt4におけるIGBT110dのゲート電圧に基づいて異常を検出する。これにより、電流制御用FET121a又は電流検出用抵抗121bの異常を検出するころができる。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

ドライバ回路

【課題】単電源駆動で、歪が小さく、大振幅の信号出力電圧が得られるドライバ回路を提供する。

【解決手段】1は入力端子、2、3は出力端子、4は第1の反転型オペアンプ、5は第2の反転型オペアンプ、6は非反転型オペアンプ、7はトランス、8は正電源電圧VCC、9はアナロググランドAGND(VCC/2)、10はグランドGND(0V)を示す。第1の反転型のドライバ用オペアンプの出力を第2の反転型のドライバ用オペアンプと非反転型のドライバ用オペアンプで受け、それらの出力を差動構成とすることで、低電圧での単電源駆動でも大振幅で、歪の小さい出力信号電圧が得られる構成とした。

(もっと読む)

スイッチング素子駆動回路

【課題】スイッチング素子駆動回路において、スイッチング素子のスイッチング損失を抑制する。

【解決手段】 ゲート電圧検出回路201は、スイッチング素子11のゲート電圧Vgsを検出し、このゲート電圧がスイッチング素子11の閾値電圧未満に設定された所定電圧未満のとき、Hレベルの昇圧指示信号を出力する。電圧制御回路103は、前記昇圧指示信号がLレベルの間は、制御電源102の所定電圧V1をそのまま出力し、前記昇圧指示信号がHレベルの間は、前記所定電圧V1を昇圧した電圧V2を出力する。駆動信号出力回路104は、PWMパルス出力回路111から出力されるPWMパルスの電圧を電圧制御回路103から出力される電圧に増幅する。従って、駆動信号出力回路104からスイッチング素子11への駆動信号は、前記PWMパルスがHレベルになった時に、先ず昇圧された電圧V2となり、スイッチング素子11のゲート電圧Vgsが所定電圧にまで上昇すると、所定電圧V1となる。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

駆動回路

【課題】電圧駆動型素子のスイッチング特性におけるトレードオフ関係を改善する駆動回路を提供すること。

【解決手段】駆動回路1は、ゲート抵抗R1とそのゲート抵抗R1に対して並列に接続されている分岐回路部23を備えている。分岐回路部23は、分岐ゲート抵抗R3とツェナーダイオードZD1を有するとともに、分岐ゲート抵抗R3とツェナーダイオードZD1が直列に接続されている。ツェナーダイオードZD1のカソードが駆動電源V1の正極端子14側に接続されており、ツェナーダイオードZD1のアノードがトランジスタTr1の制御端子12側に接続されている。

(もっと読む)

電圧駆動型スイッチングデバイスの駆動回路

【課題】ターンオン時のゲート電流を所望の電流値に高精度に設定でき、スイッチング損失の低減が可能な電圧駆動型スイッチングデバイスの駆動回路を得る。

【解決手段】IGBT1のゲート端子に接続され、駆動用パルス信号2のオン/オフゲート制御信号に基づき、IGBT1をターンオン/ターンオフさせるゲート信号を前記ゲート端子に出力するゲート駆動定電流回路が示されている。このゲート駆動定電流回路は、正電源3とGND電位4間に直列に接続された第1の抵抗5と第1のトランジスタ15と第2の抵抗6と制御信号伝達トランジスタ7、および正電源3とIGBT1のゲート端子間に直列に接続されたゲートオン抵抗8と定電流出力トランジスタ9を備え、第1のトランジスタ15のベース端子は第1のトランジスタ15のコレクタ端子と短絡接続されている。

(もっと読む)

スイッチング素子の駆動回路

【課題】スイッチング素子S*#のオン状態への切り替えによってこれを流れる電流が急激に大きくなると、ツェナーダイオード40およびクランプ用スイッチング素子42を備えて構成されるクランプ回路による対処が間に合わなくなるおそれがあること。

【解決手段】スイッチング素子S*#のオン操作指令に伴い、まず制限用電圧VLを端子電圧とする直流電圧源25を電源とし、定電流用スイッチング素子27を用いてスイッチング素子S*#のゲート充電処理を行う。そして、所定時間が経過することで、定常用電圧VH(>VL)を端子電圧とする直流電圧源22を電源とし、定電圧用スイッチング素子23を用いてスイッチング素子S*#のゲート充電処理を行う。

(もっと読む)

半導体装置

【課題】高電位側スイッチ素子の十分な駆動電圧を実現した半導体装置を提供する。

【解決手段】半導体装置は、入力電圧用端子、出力用端子、接地電位用端子、電源電圧用端子、第1端子を有し、入力電圧用端子と出力用端子との間にソースードレイン経路を有する第1MOSを含む第1チップ、出力用端子と接地電位用端子との間にソースードレイン経路を有する第2MOSを含む第2チップ、第1MOSのゲートにその出力が接続された第1駆動回路、第2MOSのゲートにその出力が接続された第2駆動回路、電源電圧用端子に接続されたドレインと、第1端子に接続されたソースとを有するPMOSとを含む第3チップが一つのパッケージ内に封止され、第1端子と出力用端子との間に容量が接続可能とされ、第2MOSがオンとされるとき、PMOSはオンとされ、第2MOSがオフとされるとき、PMOSはオフとされる。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】2つのトランジスタTr1,Tr2によりリレーのコイル13aに通電するECU11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の各々を定期的に且つ互いに時間をずらして所定時間だけ低下させることにより、一方のトランジスタの通電能力が落ちてドレイン・ソース間電圧が所定値以上になる期間を発生させる。そして、故障判定部32は、各トランジスタのソース電圧VS1,VS2の差が所定の閾値以上になったことを検知すると、トランジスタTr1,Tr2が設けられている通電用配線L1,L2の負荷側部分LS1,LS2の何れかが断線していると判断する。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】トランジスタTr1,Tr2によりリレーのコイル13aに通電する装置11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の両方を定期的に所定時間だけ低下させることにより、両トランジスタTr1,Tr2の通電能力が落ちてドレイン・ソース間電圧が所定値以上になる検査用期間を発生させ、該検査用期間中に、故障判定部32が、各トランジスタTr1,Tr2のドレイン・ソース間電圧を監視し、ドレイン・ソース間電圧が判定値未満のトランジスタがあれば、該トランジスタが設けられている通電用配線の反負荷側部分(LD1又はLD2)が断線していると判定する。

(もっと読む)

高周波モジュールおよび無線通信システム

【課題】低コスト化または小型化を実現可能なマルチバンド対応の高周波モジュールおよび無線通信システムを提供する。

【解決手段】例えば、高周波電力増幅装置HPAIC1は、GSM用のパワーアンプ回路部PABK_LB(PABK_HB)と、GSMかW−CDMAかを選択するモード設定信号Mctlを受けて、アンテナスイッチ制御信号SctlをVSW1レベルかVSW2レベルで出力する制御回路を備える。VSW2は、発振回路OSCからのクロック信号を用いてVSW1を昇圧することで生成される。HPAIC1は、MctlによってGSMが選択された際には、OSCを停止させると共にVSW1レベルのSctlをアンテナスイッチ装置ANTSWに出力し、MctlによってW−CDMAが選択された際には、OSCを用いてVSW2レベルのSctlをANTSWに出力する。

(もっと読む)

半導体出力回路及び外部出力信号生成方法並びに半導体装置

【課題】電源電圧の低下による外部出力信号のばらつきを抑制する。

【解決手段】内部入力信号Aの電位がグランド側からVDD側、あるいはVDD側からグランド側へ変化するのに応じて、出力部1は外部出力信号EBの電位を変化させる。差動部2は、外部出力信号EBと、所定の基準信号VREFとに応じた出力信号を出力し、外部出力信号EBが所定の基準信号VREFに応じた電位となるようボルテージフォロアとして機能する。これにより、外部出力信号EBの低電圧側出力電圧VOLのばらつきを抑制する。

(もっと読む)

高周波スイッチ

【課題】マルチモードシステムにおいてSOI基板上に形成された高周波スイッチの挿入損失特性を改善する。

【解決手段】少なくとも1つの第1ポート10および第2ポート20、共通ポート30、第1および第2シリーズスイッチ40,50を有する。第1ポート、第2ポートは、各々高周波信号を入力または出力する。共通ポートは、第1ポートまたは第2ポートを介して入出力される高周波信号を送信または受信する。第1シリーズスイッチは、少なくとも1つの第1のFETを備え、第1のFETのゲートに接続される第1ゲート抵抗への印加電圧に応じて第1ポートと共通ポートとの間を導通または遮断する。第2シリーズスイッチは、少なくとも1つの第2のFETを備え、第2のFETのゲートに接続され、第1ゲート抵抗よりも大きな抵抗値を有する第2ゲート抵抗への印加電圧に応じて第2ポートと共通ポートとの間を導通または遮断する。

(もっと読む)

高周波半導体スイッチ

【課題】送信端子および受信端子に求められる特性を考慮して設計されたFETを有する高周波半導体スイッチを提供する。

【解決手段】高周波半導体スイッチ10は、複数の電界効果型トランジスタ50を有する。複数の電界効果型トランジスタ50は、それぞれ、基板100に間隔を置いて形成されたソース領域130およびドレイン領域140と、当該間隔上であって基板100上に形成されたゲート160と、基板100上に形成されソース領域に接続されるソースコンタクト172と、基板100上に形成されドレイン領域140に接続されるドレインコンタクト182とを含む。受信端子側に接続される受信端子側トランジスタ50aのソースコンタクト172およびドレインコンタクト182間の距離Lrは、送信端子側に接続される送信端子側トランジスタ50cのソースコンタクト172およびドレインコンタクト182間の距離Ltよりも長い。

(もっと読む)

101 - 120 / 1,457

[ Back to top ]