Fターム[5J056AA00]の内容

論理回路 (30,215) | 回路の種類 (3,583)

Fターム[5J056AA00]の下位に属するFターム

入力回路 (420)

論理演算回路 (504)

出力回路 (1,065)

インターフェース、レベルシフト、レベル変換 (1,016)

Fターム[5J056AA00]に分類される特許

201 - 220 / 578

半導体集積回路及びLSIシステム

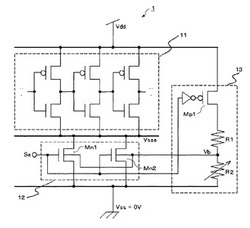

【課題】CMOS論理回路を小さいスイッチで高速動作させることができ、サブスレッショルドリーク電流を効果的に低減可能な半導体集積回路及びLSIシステムを提供すること。

【解決手段】半導体集積回路は、CMOS論理回路と、CMOS論理回路の電圧供給源とCMOS論理回路の電源端の間に設けられた、第1のMOSFETを有するスイッチ回路と、第1のMOSFETと逆チャネルの第2のMOSFETと、第2のMOSFETのドレインに接続された第1の抵抗と、第1の抵抗及び第1のMOSFETのソースに接続された第2の抵抗と、を有するデジタルアナログ変換回路とを備える。第1のMOSFETのバックゲートと、第1の抵抗と第2の抵抗の接続点が接続される。また、第1のMOSFETのゲートに供給される制御信号と第2のMOSFETのゲートに供給される制御信号が共通である。

(もっと読む)

内蔵型低電圧差動信号インターフェース付の高速ディジタル・ガルヴァニック・アイソレータ

【課題】 様々な種類の高速ディジタル・ガルヴァニック・アイソレータ及びそれに対応する集積化低電圧差動信号(「LVDS」)インターフェースを提供する。

【解決手段】 幾つかの実施形態によれば、ファントム電力が、ガルヴァニック・アイソレータの一方の側にアイソレータの他方の側から、2つの側を相互接続するシールドが付いたツイストペア・ケーブルを介して与えられるため、電力を別の電源を通して、又はアイソレータの両側に向けられて 接続された別個の物理的な配線によって、ガルヴァニック・アイソレータの両側に与える必要性が取り除かれる。そのようなファントム電源の構成により、コストが削減され、電力消費が低下され、またノイズ・レベルが低い高速シリアルデータ通信が必要な装置の中で利用できる工学設計の選択肢の数が増加される。

(もっと読む)

半導体集積回路

【課題】周辺の回路ブロックの動作に与える影響を抑制しつつ、パワーゲーティングによって回路ブロックが動作状態に移行できるようになるまでの時間を短くする。

【解決手段】タイミング制御部13は、回路ブロックB1の動作中に回路ブロックB2が待機状態から動作状態へ移行するように指示された場合、スイッチング素子T1−1〜T1−nがオンしないように制御し、回路ブロックB1の停止中に回路ブロックB2が待機状態から動作状態へ移行するように指示された場合、スイッチング素子T1−1〜T1−nがオンするように制御する。

(もっと読む)

半導体装置

【課題】低消費電流の半導体装置を提供する。

【解決手段】このサーモスタットIC1では、目標温度に応じたレベルの一定の参照電圧Vrefを発生する参照電圧発生回路4と、検出温度に応じたレベルの電圧Vtを出力する温度センサ5と、参照電圧Vrefと電圧Vtの高低を比較し、比較結果を示す信号を出力する比較回路6とを備え、参照電圧発生回路4および比較回路6の活性化/非活性化の制御が可能になっている。したがって、全部の回路を常時活性化させていた従来に比べ、消費電流が小さくて済む。

(もっと読む)

半導体集積回路

【課題】CPUの動作に支障を来すこと無く、消費電力を削減することが可能な半導体集積回路を提供する。

【解決手段】CPU10と別に設けられた電源制御回路40は、半導体チップ1上に設けられたCPU10からの信号(例えばアイドル信号Si)を検出する。電源制御回路40は、この信号に応じて、CPU10に対してスイッチ素子30_1を制御して電源電圧Vpの供給を制御する。この制御により、CPU10の動作に支障をきたすことなく、効率よく電源制御が行える。

(もっと読む)

電流変動制御装置、半導体集積回路、電流変動制御方法および電流変動制御プログラム

【課題】面積を小さくでき、かつ、消費電流の変化を抑制して安定した動作を行う半導体集積回路の全体消費電流を制御する電流変動制御装置を提供する。

【解決手段】電流変動制御装置は、本来的用途に応じて設けられている複数の既存内部回路Bを選択的に活性化させて調整用の消費電流を生じさせる電流制御回路と、内部回路Aのリセット解除およびリセット投入を制御するリセット制御信号を出力するとともに電流制御回路に動作許可を与える動作許可信号を出力するリセット制御回路と、を備える。電流制御回路は、既存内部回路Bに活性化制御信号を出力し、内部回路Aのリセット解除前に既存内部回路Bを順次選択して活性化させることによりこれら既存内部回路Bによる調整用消費電流を徐々に上昇させ、内部回路Aのリセット解除時に既存内部回路Bの活性化を停止させる。

(もっと読む)

電源遮断制御回路および電源遮断制御方法

【課題】リーク電流の大きさに基づいた集積回路の電源遮断の制御をする電源遮断制御回路および電源遮断制御方法を提供する。

【解決手段】集積回路の基本回路をモデル化したモデル回路を含むモデル回路部と、前記モデル回路で生じたリーク電流によって充電される出力電圧と予め設定された基準電圧とを比較する電圧比較回路部と、前記比較結果から前記出力電圧が前記基準電圧に達するまでの到達時間を計測し、該計測結果から前記リーク電流の大きさを判定する判定回路部と、前記判定されたリーク電流の大きさに基づいて、前記集積回路の電源遮断を制御する電源遮断制御回路部と、を備える、電源遮断制御回路。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

デジタル処理コンポーネント内で使用する適応電圧スケーリングクロック発生器およびその操作方法

【課題】デジタル処理コンポーネントの電源レベルを調整して、適正な電力消費を実現する。

【解決手段】複数の動作周波数に変更することができるクロック信号を選択的にデジタル処理コンポーネント(100)に加えるクロック制御回路(705,710,715)が開示される。クロック制御回路(705,710,715)は(i)第1の動作周波数を第2の動作周波数に変更するコマンドを受信する、(ii)コマンドに応答して加えられたクロック信号をディセーブルする、(iii)第2の動作周波数を有するテストクロック信号を発生する、(iv)テストクロック信号を電源調節回路(125)に加える、および(v)電源調節回路(125)からの状態信号を感知するように操作できる。状態信号はデジタル処理コンポーネント(100)の電源レベルが第2の動作周波数に対して適切な最適値に調節されていることを示す。

(もっと読む)

レベル変換回路

【課題】レベル変換を適切に行うことができるレベル変換回路を提供する。

【解決手段】レベル変換回路45は、第1〜第4のPMOSトランジスタPH1,PH2,PH40,PH41と、第1及び第2のNMOSトランジスタNH1,NH2と、バイアス回路46とを含み、基準電圧GNDと第1電源電圧Vddを信号レベルとする入力信号INを、基準電圧GNDと第1電源電圧Vddよりも高い第2電源電圧Vppを信号レベルとする出力信号OUTにレベル変換する。バイアス回路46により、第3及び第4のPMOSトランジスタPH40,PH41のゲートにバイアス電位PBが供給され、出力信号OUTの変化時に第3及び第4のPMOSトランジスタPH40,PH41に流れる電流が第1及び第2のNMOSトランジスタNH1,NH2に流れる電流と比例関係となるよう制御される。

(もっと読む)

高信号レベル対応入出力回路

インターフェース回路用の信号ドライバ(211)は、第1信号レベルにおいて出力信号および入力信号を受け付ける第1ステージレベルシフタ(311)を持つ。この信号ドライバ(211)はまた、第1ステージレベルシフタ(311)に結合され、第2信号レベルにおいて信号を出力する第2ステージレベルシフタ(312)を持つ。第1(311)および第2(312)ステージレベルシフタの電子構成要素は、第2信号レベルよりも低い信頼性の限界を持っている。第1ステージレベルシフタ(311)および第2ステージレベルシフタ(312)の第1および第2ステージ構成は、第2信号レベルにおいて信号を出力する処理の際に、電子構成要素が、信頼性の限界より高い端子〜端子信号レベルにさらされるのを、防止する。  (もっと読む)

(もっと読む)

高信号レベル対応入出力回路

レベルシフタ(410)は少なくとも2つのプルダウン回路(M1,M2,412またはM3,M4,422)を持つ。この回路は、レベルシフタから出力される最大信号レベルより低い信頼性の限界を伴う電子構成要素で作られる。このレベルシフタはまた、プルダウン回路(M1,M2,412またはM3,M4,422)に結合されるタイミング回路(411,421)を持つ。このタイミング回路は、電子構成要素が経験する端子〜端子信号レベルが信頼性の限界を超えることを防止するプルダウン回路への、入力信号(入力,input_n)の印加時間を制御する。  (もっと読む)

(もっと読む)

半導体集積回路装置および消費電力制御方法

【課題】追加回路を最小限に抑えた設計で消費電力を効果的に削減する消費電力制御を行う半導体集積回路装置を提供する。

【解決手段】バスマスタ3、4は、バスアクセス要求を発行して、かつアクセス許可がない場合は、クロックゲーティング回路6にクロック遮断要求を発行し、バスアービタ2は、バスアクセス許可を発行したとき、該バスアクセス許可の発行先のバスマスタに関するクロック遮断解除要求をクロックゲーティング回路に発行し、クロックゲーティング回路6は、クロック遮断要求を発行したバスマスタへのクロック供給を遮断し、クロック供給が遮断されたバスマスタに関するクロック遮断解除要求が発行されたとき該バスマスタへのクロック供給の遮断を解除する。

(もっと読む)

半導体集積回路装置

【課題】他の性能を落とさずに低消費電力化LSI及びLSIの低消費電力化を達成する半導体集積回路装置を提供すること。

【解決手段】低消費電力化LSI101は、経年劣化の少ない動作初期の段階は、主に基準電圧から経年劣化マージンに相当する電圧を差し引いた動作電圧値を記憶し、経年劣化が進むとともに同一性能を保証するため段階的に動作電圧値が基準電圧に近づいていく動作電圧値を記憶する経年劣化係数テーブル104を備え、電源電圧制御部102は、不揮発記憶装置105に記憶された実使用時間と経年劣化係数テーブル104の値から最適な前記動作電圧値を求め、この動作電圧値を基に電源電圧を変化させる。

(もっと読む)

半導体集積回路

【課題】回路ブロックの電源供給/切断を制御する構成において安全且つ高速に回路ブロックの電源復帰が可能な半導体集積回路を提供することを目的とする。

【解決手段】半導体集積回路は、内部回路と、前記内部回路へ電源を供給する経路に設けられ、制御端子に印加される制御信号の電圧に応じた導通状態となることにより、前記内部回路への電源供給状態を制御する電源スイッチと、前記制御信号を所定の電圧にクランプするクランプ回路と、前記クランプ回路のクランプ動作の有効及び無効を切り替える切り替え回路とを含み、前記内部回路への電源供給状態を前記電源スイッチにより切断状態から供給状態に変化させるときに前記クランプ回路のクランプ動作を有効な状態に設定することを特徴とする。

(もっと読む)

昇圧回路

【課題】入力電圧VINが低い場合でもレベルシフタを構成するトランジスタの閾値のばらつきの影響を抑制して動作するようにし、かつ、出力電圧VOUTの立ち上がりが速く、所望の出力電圧に達した後はレベルシフタによる消費電力を抑制することができる昇圧回路を提供する。

【解決手段】電源電圧VDDレベルのクロック信号CK3,CK4を出力電圧VOUTレベルにシフトするレベルシフト部20A,20Bに、出力電圧VOUTが低くても正常に動作するレベルシフタ30と、出力電圧VOUTが高い時に低消費電流で動作するレベルシフタ40を設け、動作開始から出力電圧VOUTが所定の電圧に上昇すると想定されるまでレベルシフタ30を選択し、その後、レベルシフタ40に切り替えて昇圧動作を継続する。

(もっと読む)

レベルシフト回路及びパワー半導体装置

【課題】低耐圧トランジスタを使用して構成可能であり、CMOSプロセスに適した回路構成を有するレベルシフト回路を提供する。

【解決手段】レベルシフト回路10が有するトランジスタM5は、V_BOOTとV_LXの間に結合され、ハイサイドNMOSトランジスタMAのゲートを駆動するための出力信号を生成する。V_BOOTは、ブートストラップ回路11によってV_LXを基準に生成される。V_LXは、トランジスタMAのソース電位である。PMOSトランジスタM3は、ソースとバックゲートがV_BOOTに、ドレインがトランジスタMAのゲートに結合される。クランプ・トランジスタM11は、ゲートがトランジスタMAのソースに、ソースとバックゲートがトランジスタM3のドレインに結合される。クランプ・トランジスタM12は、ゲートがトランジスタMAのソースに、ソースとバックゲートがトランジスタM3のゲートに結合される。

(もっと読む)

レベルアップ変換回路

【課題】高電圧側の電源電圧の変動による遅延時間の変動を小さくし、クロック出力用に使用する場合にはクロックジッタを低減し、高信頼性を得ることができ、また、高電圧側の電源電圧を低くした高速信号ラインにも使用できるようにしたレベルアップ変換回路を提供する。

【解決手段】PMOSトランジスタPM7、PM8を設け、入力デジタル信号SINがVDDL(Hレベル)の場合、ノードN5の電位を高電圧側の電源電圧VDDHとし、入力デジタル信号SINが0V(Lレベル)に変化したときに、PMOSトランジスタPM2がOFFからONになる時間を短くする。

(もっと読む)

レベルシフト回路

【課題】第1p型トランジスタにおけるカット電流を低減する。

【解決手段】高レベル電源電圧HVを一端に受ける第1および第2p型トランジスタ14,20と、一端が第1および第2p型トランジスタの他端にそれぞれ接続され、他端に可変負電源電圧ZVssが供給される第1および第2n型トランジスタ18,24を含む。

第1n型トランジスタ18の制御端に通常正電源電圧Vcc、第2n型トランジスタ24の制御端に負電源電圧Vssを供給することで、第2p型トランジスタ20と第2n型トランジスタ24の接続部から高レベル正電源電圧HVのいずれかを出力する。この高レベル正電源電圧HVを出力する時に、前記可変負電源電圧ZVssを第1n型トランジスタ18の十分なオン状態が維持できる範囲内で負電源電圧Vssより高い電圧にする。

(もっと読む)

電源選択装置

【課題】出力端子に接続された被供給回路の動作が不安定とならず、かつ貫通電流が発生しない電源選択装置を提供する。

【解決手段】本電源選択装置は、電圧源入力端子1と電圧源出力端子3との間に直列に接続されたPMOSトランジスタ11aとPMOSトランジスタ11bを備え、電圧源入力端子2と電圧源出力端子3との間に直列に接続されたPMOSトランジスタ11cとPMOSトランジスタ11dを備え、電源電圧切り替え時に、PMOSトランジスタ11a〜11cを遮断状態にし、かつPMOSトランジスタ11dを導通状態にして、電圧源入力端子2に入力された電圧を、PMOSトランジスタ11cの寄生ダイオードを介して電圧源出力端子3へ供給する。

(もっと読む)

201 - 220 / 578

[ Back to top ]