Fターム[5J056AA00]の内容

論理回路 (30,215) | 回路の種類 (3,583)

Fターム[5J056AA00]の下位に属するFターム

入力回路 (420)

論理演算回路 (504)

出力回路 (1,065)

インターフェース、レベルシフト、レベル変換 (1,016)

Fターム[5J056AA00]に分類される特許

161 - 180 / 578

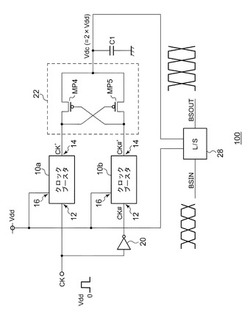

ブースト回路およびそれを用いたΔΣ変調器、電子機器

【課題】ブースト回路におけるビットエラーを防止する。

【解決手段】ビットストリーム信号BSINを受け、その振幅をブーストして出力するブースト回路100が提供される。第1クロックブースタ10aは、クロック信号CKを受け、その振幅をブーストする。第2クロックブースタ10bは、反転されたクロック信号CK#を受け、その振幅をブーストする。スイッチ22は、クロックブースタ10a、10bの出力信号CK’、CK#’を受け、ハイレベルである一方を選択する。第1キャパシタC1は、スイッチ22の出力端子にカップリングされる。レベルシフタ28は、ビットストリーム信号BSINのハイレベルを、第1キャパシタC1に生ずる電圧レベルにレベルシフトする。

(もっと読む)

半導体集積回路装置

【課題】電源スイッチによる電源遮断技術とDVFSによる低消費電力化技術とを共存可能にし、効率的な消費電力の低減を実現する。

【解決手段】電源VDDが供給される電源スイッチ部7、該電源スイッチ部7による電源遮断が行われる回路ブロック2、およびレベルシフタ13と、電源VDD2が供給される電源スイッチ部8、該電源スイッチ部8による電源遮断が行われる回路ブロック3、およびレベルシフタ14とは、異なるDEEP−NWELL領域19,20にそれぞれ形成されており、これにより、DEEP−NWELLを介しての異なる電源間でのショートを防止する。

(もっと読む)

CMOSバイアス回路

【課題】電源電圧の変動の影響を低減することが可能なCMOSバイアス回路を提供する。

【解決手段】CMOSバイアス回路は、起動回路と、被起動回路部と、を備え、起動電流供給部は、第1の端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され第1の電流を出力する第1の電流供給回路と、を含み、起動電流停止制御部は、内部電流をカレントミラーした停止制御電流を第1のMOSトランジスタの他端に供給し、被起動回路部は、内部電流が第1の電流値以上のときは内部電流を第2の電流値まで増加させ、起動電流が零ならば内部電流を第2の電流値で安定させ、零より大きい起動電流に応じて内部電流を第1の電流値以上に増加させる。

(もっと読む)

レベルシフト回路、スイッチング素子駆動回路及びインバータ装置

【課題】レベルシフト回路の電圧変動等に起因するコモンモードノイズ発生時でもクランプすることなく、信号を伝達できるレベルシフト回路、スイッチング素子駆動回路及びインバータ装置を提供する。

【解決手段】セットパルス及びリセットパルスを発生するパルス発生回路と、セットパルスを電流に変換する第1スイッチング素子及びリセットパルスを電流に変換する第2スイッチング素子と、浮動電位側にあり、第1スイッチング素子で電流に変換された信号を電圧に変換するセット用負荷及び第2スイッチング素子で電流に変換された信号を電圧に変換するリセット用負荷と、セット用負荷の信号レベルおよびリセット用負荷の信号レベルから、制御パルス信号を再生するパルス再生回路を備えるレベルシフト回路において、セット用負荷及びリセット用負荷として非線形の負荷特性を有する回路を用いる。

(もっと読む)

同期出力を有する周波数分周器

【解決手段】周波数でクロック信号を分周し、優れた信号特性を有する差動信号を供給し得る分周器が記述される。1つの典型的な設計では、分周器はシングルエンド分周器及び同期回路を含む。シングルエンド分周器は、周波数でクロック信号を分割し、タイミングスキューを有する相補型信号である第1及び第2信号を供給する。同期回路は、クロック信号に基づき第1、第2信号をリサンプリングし、低減したタイミングスキューを有する差動信号を供給する。1つの典型的な設計では、同期回路は第1及び第2スイッチ、並びに第1及び第2インバータを含む。第1スイッチ及び第1インバータによって第1サンプリング−保持回路又は第1信号をリサンプリングする第1ラッチが形成される。第2スイッチ及び第2インバータによって、第2サンプリング−保持回路又は第2信号をリサンプリングする第2ラッチが形成される。 (もっと読む)

スタートアップ回路

【課題】必要とするキャパシタの数を削減し、且つ電源電圧が低下しても基準電圧回路から出力する基準電圧の変動を防止できるようにする。

【解決手段】電源投入時に定電流回路10に起動電流を供給するキャパシタC1と、該キャパシタC1に流れる起動電流を入力しそのミラー電流が出力するカレントミラー回路(MN31,MN32)とを設ける。そして、該カレントミラー回路の出力電流を基準電圧回路20に起動電流として供給する。

(もっと読む)

電子装置およびその外部電源供給装置の制御方法

【課題】電子装置およびその外部電源供給装置の制御方法を提供する。

【解決手段】本発明による電子装置1は、オン状態とオフ状態を有する外部電源供給装置5と電気接続し、該電子装置はスイッチモジュール2と、内部電源モジュール3とを含み、スイッチモジュールが触発されると、スイッチ信号を生成する。内部電源モジュールは、スイッチ信号を受信し、トリガ信号を生成して、外部電源供給装置に伝送することにより、外部電源供給装置をオフ状態からオン状態に切り換え、該外部電源供給装置は、電子装置に電源を供給する。

(もっと読む)

演算回路

【課題】 低消費電力化が図られた演算回路を提供することを目的とする。

【解決手段】 第2の電源分離領域12に対応して設けられた第2の電力制御回路22が、第2の電源分離領域12よりも一段だけ前段の第1の電源分離領域11での情報パケットAの処理の開始時点で、第2の電源分離領域12への電力供給を開始するとともに、第2の電源分離領域12での情報パケットBの処理の終了時点で第2の電源分離領域12への供給電力を遮断する。

(もっと読む)

レベルシフト回路

【課題】低消費電力で高速動作が可能なレベルシフト回路を提供する。

【解決手段】レベルシフト回路は、タイミング制御回路1と、充電回路2と、放電回路3と、電圧保持回路4と論理合わせ回路5とを有する出力信号生成回路6とを備えている。出力信号Voutの論理を決定するために電流駆動力が大きいトランジスタQ21とトランジスタQ31とを縦続接続し、これらトランジスタQ21とトランジスタQ31とに貫通電流が流れないようにタイミング制御回路1がトランジスタQ21とトランジスタQ31のオン・オフを制御するため、トランジスタQ21およびトランジスタQ31が同時にオン状態となることはない。よって、低電源電圧端子から、トランジスタQ21およびトランジスタQ31を通して、接地端子へ貫通電流が流れることがなく、レベルシフト回路は低消費電力で高速動作が可能である。

(もっと読む)

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

半導体集積回路装置

【課題】従来のパワースイッチと比較して、高速動作を行う活性状態と、内部論理状態は保持しているが低リーク状態である非活性状態を実現し、その二つの状態間の遷移を高速かつ低雑音かつ低電力を実現する。

【解決手段】第1の外部電源電圧(VDD)を与える第1電源線と第2の外部電源電圧(VSS)を与える第2電源線間に、複数の回路からなる内部回路ブロックと電源電圧を制御するパワー制御回路を具備し、制御回路は出力MOSFET(MPP)を具備し、出力MOSFETはゲートとソースが等電圧であっても一定のオフ電流が流れるものであって、出力MOSFET(MPP)の閾値電圧は、内部回路MOSFETのそれよりも小さい。

(もっと読む)

動的な電圧及び周波数管理

一実施形態において、集積回路は、テストに不合格となるまで、各々、より低い要求供給電圧大きさで集積回路のロジック回路のテストを繰り返すように構成された自己校正ユニットを備えている。テストに合格する最も低い要求供給電圧大きさを使用して、集積回路の要求供給電圧大きさを発生する。一実施形態では、集積回路は、集積回路のエリアにわたって物理的に分布されたロジックゲートの直列接続体と、論理的遷移をその直列接続体へ送出し、そしてそれに対応する遷移をその直列接続体の出力において検出するように構成された測定ユニットとを備えている。送出と検出との間の時間量を使用して、集積回路の供給電圧大きさを要求する。 (もっと読む)

電流制限回路

【課題】回路面積を削減しつつ、より適切に電流を制限することが可能な電流制限回路を提供する。

【解決手段】電流制限回路は、第1の端子と、第1の端子との間に負荷回路を接続した場合に、第1の端子よりも電位が低くなる第2の端子と、第1の端子と第2の端子との間に接続され、n型MOSトランジスタである第1のトランジスタと、第1のトランジスタのソースと第2の端子との間に接続され、MOSトランジスタである第2のトランジスタと、第2のトランジスタのソース・ドレイン間の電圧を検知し、検知された検知電圧に基づいて、第1のトランジスタのゲートに印加する第1の電圧を制御する第1の制御回路と、第2のトランジスタのゲートに印加する第2の電圧を制御する第2の制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】2系統の電源を使用する半導体集積回路において、電源投入・遮断時に、一方の電源が投入されていない場合、回路内部のノードの電位が不定になってしまう箇所が発生するという課題があり、更に、その結果として回路内部に無駄な貫通電流が流れるという課題があった。

【解決手段】VDDIOを電圧降下させてノードN1にVDD以下の所定電位を印加する電圧降下手段82と、ノードN1に接続され、VDDを入力するインバータ83と、インバータ83の出力信号に基づきオン/オフ動作し、オン状態のときには、“L”を出力するNMOS84とを有する論理回路80を設け、VDDIOが印加され、VDDが印加されていないときは、NMOS84からレベルシフタのノードN3にL”を出力してレベルシフタ90内の論理レベルを確定する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置及びそのスイッチトランジスタの制御方法

【課題】従来の半導体装置では、電源スイッチ回路の回路規模が大きくなる問題があった。

【解決手段】本発明にかかる半導体装置は、グローバル電源配線とローカル電源配線との導通状態を制御信号に応じて制御するスイッチトランジスタと、制御信号を遅延させて後段に接続されるスイッチトランジスタに伝達する遅延回路と、を備える複数のスイッチセルを有する半導体装置であって、外部から制御信号を受け、直列に接続された遅延回路により制御信号を伝達し、スイッチトランジスタを順次導通させるチェーン部と、チェーン部の最終段に配置されるスイッチセルを介して制御信号が与えられ、並列に接続された遅延回路により制御信号を複数の系列に分配し、分配された制御信号によりスイッチトランジスタを並列して導通させるツリー部と、を有する。

(もっと読む)

接触式集積回路カード読み取り機の電源インターフェース回路

本発明は、接触式ICカードに電源を供給する電源インターフェース回路を具現するにあたって、さらに簡単な構成で且つ安定して電源を供給することができる技術に関する。本発明による電源インターフェース回路は、外部から供給される電源制御信号を反転及び増幅して出力する電源制御部と、前記電源制御部の出力信号によって相補型トランジスタ部の接地端子側トランジスタのオン/オフ動作を制御するスイッチングダイオード部と、前記電源制御部から直接入力される制御信号と前記スイッチングダイオード部を介して入力される制御信号によって相補型トランジスタが互いに相反する動作を行いながら電源端子電圧を電源出力部側に伝達するか、または当該電源出力部のカード電源端子を接地電圧のレベルにミューティングさせる相補型トランジスタ部と、前記相補型トランジスタ部の動作によって、当該相補型トランジスタ部を介して入力される電圧をICカードのカード電源端子に出力するか、またはカード電源端子を接地電圧のレベルに維持する電源出力部と、を備えて構成されることを特徴とする。 (もっと読む)

半導体装置、及び動作モ−ド切換方法

【課題】動作モード切換用パッドの配置自由度を向上させる。

【解決手段】パッドに新規に設けたプルアップ回路、及びプルダウン回路のスイッチを排他的に(交互に)切り換えられるようにして、プルアップ回路接続時のパッド電位と、プルダウン回路接続時のパッド電位とのEOR演算を行う。それぞれの電位は時系列で測定されるため、先に測定された電位は一時的な記憶回路に格納しておき、次に測定された電位とEOR演算を行う。以上の演算処理により、パッケージピンとパッドが接続されている端子は「0」、OPENの端子は「1」の情報を得ることができるため、これらの情報を基に動作モードを切り換える。

(もっと読む)

レベルシフト回路

【課題】出力信号の電圧値を変化させるための入力信号のしきい値を任意の値に設定することができるレベルシフト回路を提供する。

【解決手段】入力信号Sinの入力端子2と基準電位の入力端子3との間に直列に接続された抵抗R1、R2により分圧回路9を構成する。トランジスタT1は、分圧回路9から出力される検出電圧Vdetに基づいてオンオフされる。出力回路8のトランジスタT2と抵抗R5は、電源電圧VDDBを供給する電源線10とグランド線4との間に直列に接続する。トランジスタT2は、トランジスタT1のオンオフに応じてオンオフし、コレクタから電源電圧VDDBまたは0Vの出力信号Soutを出力する。

(もっと読む)

増幅回路、基準電圧生成回路、集積回路装置、電気光学装置、及び電子機器

【課題】寄生容量等の悪影響を最小限に抑えた上で高精度な電圧を出力する。

【解決手段】演算増幅器OPと、入力ノードNIと演算増幅器OPの第1の入力端子NEGとの間に設けられる電荷蓄積用キャパシタCAと、演算増幅器OPの出力端子に設けられる位相補償用キャパシタCCと、を含み、電荷蓄積用キャパシタCAは、両端の電極が金属層又はポリシリコン層で形成される第1タイプのキャパシタType1で構成され、位相補償用キャパシタCCは、一方の電極がポリシリコン層で、他方の電極が不純物層で形成される第2タイプのキャパシタType2で構成され、位相補償用キャパシタCCは、平面視において電荷蓄積用キャパシタCAの下方に配置されることを特徴とする。

(もっと読む)

161 - 180 / 578

[ Back to top ]