Fターム[5J056AA00]の内容

論理回路 (30,215) | 回路の種類 (3,583)

Fターム[5J056AA00]の下位に属するFターム

入力回路 (420)

論理演算回路 (504)

出力回路 (1,065)

インターフェース、レベルシフト、レベル変換 (1,016)

Fターム[5J056AA00]に分類される特許

101 - 120 / 578

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】電源線VDDTL,VSSTL間に接続された回路ブロック10Aと、電源線VDDTL,VSSL間又は電源線VDDL,VSSTL間に接続された回路ブロック10Aの出力信号を受ける論理回路10B−1と、電源線VDDL,VSSL間に接続された論理回路10B−1の出力信号を受ける回路ブロック20と、を備える。電源線VDDTL,VSSTL間には、アクティブ状態においては第1の電圧、スタンバイ状態においては第1の電圧よりも低い第2の電圧が供給され、電源線VDDL,VSSL間には、アクティブ状態及びスタンバイ状態のいずれにおいても第1の電圧が供給される。これにより、サブシュレッショルド電流低減を維持しつつ、クリティカルパスの高速化を実現することが可能となる。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】スタンバイ時における半導体装置の消費電力を低減する。

【解決手段】スタンバイ時においてハイレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDT1L,VSSTLに接続し、スタンバイ時においてローレベルを出力すべき論理回路については、一対の電源ノードを擬似電源線VDDTL,VSST1Lに接続する。スタンバイ時における擬似電源線VDDTL,VDDT1L,VSSTL,VSST1Lの電位VDDT,VDDT1,VSST,VSST1は、VDDT<VDDT1<VDD、VSST>VSST1>VSSを満たす。これにより、スタンバイ状態においてオンするトランジスタのゲート電極と基板との間を流れるリーク電流や、スタンバイ状態においてオフするトランジスタのドレインと基板との間を流れるリーク電流が低減される。

(もっと読む)

リンギング抑制回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できるリンギング抑制回路を提供する。

【解決手段】電源と信号線12Pとの間に接続されるNチャネルMOSFET19と、信号線12Mとグランドとの間に接続されるPチャネルMOSFET20とを備え、リンギング抑制回路18は、信号線12P,12Mの電位と、それぞれに対応するNチャネルMOSFET19,PチャネルMOSFET20のゲートに付与される電位との差に応じてNチャネルMOSFET19及びPチャネルMOSFET20をオンさせて、信号線12P,12Mに発生しようとするリンギングの抑制を図る。

(もっと読む)

断線検出回路

【課題】ノイズなどの不要成分の影響を極力抑制して信頼性良く断線検出できるようにする。

【解決手段】電源Vc−グランド間には、負荷M、MOSトランジスタM1、抵抗R1が直列接続されている。第1電圧検出回路3は抵抗R1の端子電圧を検出する。制御回路2は、第1電圧検出回路3により検出された抵抗R1の検出電圧について閾値電圧ref1と比較した検出結果に基づいて断線を検出する。

(もっと読む)

レベルシフト回路

【目的】高電位側のスイッチング素子SWHのオンオフ状態にかかわらずdv/dtノイズによる誤動作を対策することができるとともに、貫通電流の発生を抑制することのできるレベルシフト回路を提供する。

【構成】インバータINV5,INV6、抵抗R8〜R11およびトランジスタMP3,MP4により、レベルシフトされたデータを記憶する記憶素子30の出力を入力側にフィードバックするフィードバック回路を構成する。当該フィードバック回路により、第1および第2のスイッチ素子MN1,MN2をプルアップもしくはプルダウンする合成抵抗の抵抗値を上記記憶素子の出力に従い変化させて、貫通電流を発生させることなくdv/dtノイズによる誤動作を対策することができる。

(もっと読む)

半導体装置

【課題】チップの製造プロセスの微細化にともなって各種リーク電流(サブスレッショルドリーク電流、ゲートトンネルリーク電流、GIDL(Gate-Induced Drain Leakage)電流などの接合リーク電流)が増大している。それらのリーク電流はチップの消費電流を増加する。

【解決手段】第1回路ブロックと、前記第1回路ブロックに接続される第1電源線及び第2電源線と、前記第1電源線と第1電位を供給する第1電位点とを接続するための第1トランジスタと、前記第1トランジスタのゲートに接続される第1駆動回路と、前記第1駆動回路より駆動力の大きい第2駆動回路とを有し、第1の状態から前記第1の状態よりも前記第1電源線と前記第2電源線の間の電位差が大きい第2の状態へ遷移する場合に、第1の期間において前記第1トランジスタを前記第1駆動回路によって駆動し、その後第2の期間において前記第1トランジスタを前記第2駆動回路によって駆動する。

(もっと読む)

レベルシフト回路

【課題】消費電流を低減することができ、信号伝達に必要な電源電圧を低減することができ、電源電圧が揺れても正確に信号を伝達することができるレベルシフト回路を得る。

【解決手段】本発明のレベルシフト回路は、インバータ回路INV2、レベルシフト素子MOS1、第1の抵抗R1及びカレントミラー回路CM1を備える。インバータ回路INV2は、入力信号を反転して出力する。レベルシフト素子MOS1は、入力信号を反転した信号をゲート信号として動作する。第1の抵抗R1の一端は、インバータ回路の出力に接続されている。カレントミラー回路CM1は、第1の抵抗R1を介してインバータ回路INV2の出力から入力した電流に対応する電流をレベルシフト素子MOS1のソースから接地点に流す。

(もっと読む)

電圧変化検知装置

【課題】電界効果トランジスタの閾値電圧がばらついた場合にも、検知電圧のばらつきを低減でき、所望の電圧検知範囲で電圧変化を検知することができる電圧変化検知装置を提供する。

【解決手段】ドレインが電源電位に接続され且つソースが第1のノードにおいて第1の定電流源又は第1の抵抗に接続され且つゲートが固定電位に接続されている第1の電界効果トランジスタと、ドレイン及びゲートが電源電位に接続され且つソースが第2のノードにおいて第2の定電流源又は第2の抵抗に接続されている第2の電界効果トランジスタと、当該第1のノードの電位と当該第2のノードの電位との比較結果に応じて電源電位が所定の検知電位を跨いで変化したことを検知した旨の検知信号を生成する検知信号生成部と、を含む電圧変化検知装置。

(もっと読む)

内部電圧発生器

【課題】プルアップ駆動部とプルダウン駆動部が同時に駆動される期間を相殺して、常に一定の内部電圧を維持することができる内部電圧発生器を提供すること。

【解決手段】本発明の内部電圧発生器は、基準電圧を用いて内部電圧のレベルを検出する検出部210と、該検出部の出力信号に応じて、前記内部電圧を出力する内部電圧端を放電駆動する第1の駆動部220と、該第1の駆動部に流れる放電電流を感知する電流感知部230と、該電流感知部の出力信号に応じて、前記内部電圧端を充電駆動する第2の駆動部240とを備える。

(もっと読む)

駆動回路

【課題】短絡時にFETの破壊を防ぐこと。

【解決手段】本発明の駆動回路(14)はFET(MP1、MP2、MN1、MN2、MP3、MN3、MP4)を具備する。FET(MN1)は、FET(MP1)に接続され、そのゲートに信号IN1が供給される。FET(MP1、MN1)の接点A1にはFET(MP2)のゲートが接続されている。FET(MN2)は、FET(MP2)に接続され、そのゲートに信号IN2が供給される。FET(MP2、MN2)の接点B1にはFET(MP1)のゲートが接続されている。FET(MP3)は、ノードOUTに接続され、そのゲートが接点(B1)に接続されている。FET(MN3)は、ノードOUTに接続され、そのゲートに信号IN3が供給される。FET(MP4)は、そのソースが接点A1に接続され、そのドレインがノードOUTに接続され、そのゲートが接点B1に接続されている。

(もっと読む)

半導体装置

【課題】 半導体装置の電源投入時におけるノイズの影響及び電圧降下を抑制すること。

【解決手段】 本半導体装置は、複数の内部回路に第1電圧を供給するための第1電源線及び第2電源線を備える。第1電源線と内部回路の間には第1スイッチが、第2電源線と内部回路の間には第2スイッチがそれぞれ設けられている。制御回路20は、複数の内部回路1〜3のうち一の内部回路3の電源投入時において、第1スイッチSW3Aに続いて第2スイッチSW3Bをオンにすることで電源を投入する。また、電源投入に伴い発生するノイズ及び電圧降下の大きさに基づいて、他の動作中の内部回路1〜2における第1スイッチSW1A及びSW2Aを制御する。この構成によれば、内部回路の電源投入時におけるノイズの影響及び電圧降下を抑制することができる。

(もっと読む)

集積回路装置、電子機器及び調整電圧の制御方法

【課題】 温度条件が変化しても停止電圧との適切な電位差を保ち低消費電力を実現する集積回路装置等を提供する。

【解決手段】 集積回路装置1であって、第1の振幅と比べて、入力された発振信号400の振幅の方が大きい場合に、第1の矩形波信号408を出力する第1の矩形波信号生成部11と、前記第1の振幅よりも大きな第2の振幅と比べて、前記発振信号400の振幅の方が大きい場合に、第2の矩形波信号402を出力する第2の矩形波信号生成部12を含む。

(もっと読む)

レベルシフタおよびそれを用いた試験装置

【課題】従来と異なる形式のレベルシフタを提供する。

【解決手段】レベルシフタ200は、第1下側電圧VssLと第1上側電圧VddLのいずれかのレベルをとる入力信号Inを、第2下側電圧VssHと第2上側電圧VddHのいずれかのレベルをとる出力信号Outにレベルシフトする。SRフリップフロップ100の出力信号Outは、そのセット端子への信号のポジティブエッジに応じて第2上側電圧VddHに遷移し、そのリセット端子への信号のポジティブエッジに応じて第2下側電圧VssHに遷移する。ANDゲート202は、SRフリップフロップ100の出力信号Qに対して反転論理レベルを有するフィードバック信号FBQと入力信号Inとの論理積を、SRフリップフロップ100のセット端子へと出力する。NORゲート204はフィードバック信号FBQと入力信号Inとの否定論理和を、SRフリップフロップ100のリセット端子へと出力する。

(もっと読む)

回路装置、電子機器及び電源供給方法

【課題】断熱的回路動作と非断熱的回路動作を切り替え可能である回路装置、電子機器及び電源供給方法等を提供すること。

【解決手段】回路装置は、論理回路200と、電源回路100と、を含む。第1のモードでは、電源回路100は、非直流の電源電圧VPK、VMKを論理回路200に供給し、論理回路200は、その非直流の電源電圧VPK、VMKが供給されることで断熱的回路動作を行う。第2のモードでは、電源回路100は、直流の電源電圧VDD、VSSを論理回路200に供給し、論理回路200は、その直流の電源電圧VDD、VSSが供給されることで非断熱的回路動作を行う。

(もっと読む)

論理回路及び半導体装置

【課題】クロックゲーティングを行う論理回路において、待機電力を低減すること又は誤動作を抑制すること。

【解決手段】論理回路は、クロック信号が供給されない期間に渡って、ソース端子及びドレイン端子に電位差が存在する状態でオフするトランジスタを有する。該トランジスタのチャネル形成領域は、水素濃度が低減された酸化物半導体によって構成される。具体的には、当該酸化物半導体の水素濃度は、5×1019(atoms/cm3)以下である。そのため、当該トランジスタのリーク電流を低減することができる。その結果、当該論理回路の待機電力を低減すること及び誤動作を抑制することができる。

(もっと読む)

集積回路装置及び電子機器

【課題】通常動作モード、低消費電力動作モードでの省電力化等を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第1の電源電圧VDDAを出力する第1のレギュレーターRG1と、外部電源電圧VDDEを受けて、外部電源電圧VDDEを降圧した第2の電源電圧VDDBを出力する第2のレギュレーターRG2と、第1の電源電圧VDDAが供給され、通常動作モード及び低消費電力動作モードにおいて動作する第1のロジック回路LG1と、第2の電源電圧VDDBが供給され、通常動作モードにおいて動作し、低消費電力動作モードでは非動作になる第2のロジック回路LG2を含む。

(もっと読む)

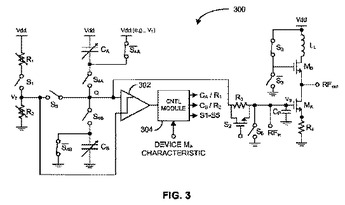

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

半導体装置及び電源スイッチ回路

【課題】電源スイッチがオフからオンの状態に遷移するときの突入電流を防ぐことにより電源スイッチオンに起因する電源ノイズの発生を防止する半導体装置及び電源スイッチ回路を提供する。

【解決手段】電源スイッチ回路が、ソースが第1の電源にドレインが前記機能回路に接続された電源スイッチトランジスタと、電源スイッチトランジスタのオンオフを制御する制御信号を入力とし、電源スイッチトランジスタのドレインと、ソースと、ゲートとにそれぞれ接続され制御信号に基づいて電源スイッチトランジスタをオフからオンの状態にスイッチさせるとき、電源スイッチトランジスタのソースドレイン間電圧が小さくなるほど電源スイッチトランジスタのソースゲート間電圧が大きくなるように電源スイッチトランジスタのゲート電圧を制御する電源スイッチトランジスタ制御回路と、を備える。

(もっと読む)

レベルシフト回路

【課題】高速に信号伝送可能なレベルシフト回路を提供する。

【解決手段】第1の電源電圧で動作する第1の回路と前記第1の電源電圧よりも高い第2の電源電圧で動作する第2の回路との間に接続され、一端に入力された信号を他端に出力する第1のスイッチ素子を有し、前記第1のスイッチ素子の他端に抵抗要素を介して前記第1または第2の電源電圧が供給される伝送回路と、前記第1のスイッチ素子がオフの状態になった場合に、前記第1のスイッチ素子の他端に前記抵抗要素を介して流れる電流と同一方向に電流を供給する制御回路と、を備えたことを特徴とするレベルシフト回路が提供される。

(もっと読む)

半導体集積回路

【課題】外部負荷を駆動する入出力回路を有するデジタル回路と、外部回路と通信を行う通信回路を備えるアナログ回路とを混載して成る半導体集積回路において、入出力回路による内部発生ノイズを低減し、アナログの通信回路における通信エラーの発生を抑える。

【解決手段】外部負荷となるメモリ5を駆動する入出力回路3とCPU2とを有するデジタル回路と、イーサーネットによって外部回路と通信を行う通信回路41を備えるアナログ回路4とを混載して成る半導体集積回路1において、前記入出力回路3と電源VDDとの間に電圧調整回路6を介在して、入出力回路3への供給電源電圧VDD’を可変にする。そして、CPU2が前記通信回路41からエラー通知F2を受信すると、電圧制御回路6へ電圧制御信号F3を出力し、前記入出力回路3の動作を保証できる下限電圧までの範囲で、パッド31,32に加わる電圧を低下させ、ノイズF1を抑える。

(もっと読む)

101 - 120 / 578

[ Back to top ]