Fターム[5J056AA00]の内容

論理回路 (30,215) | 回路の種類 (3,583)

Fターム[5J056AA00]の下位に属するFターム

入力回路 (420)

論理演算回路 (504)

出力回路 (1,065)

インターフェース、レベルシフト、レベル変換 (1,016)

Fターム[5J056AA00]に分類される特許

21 - 40 / 578

電子回路

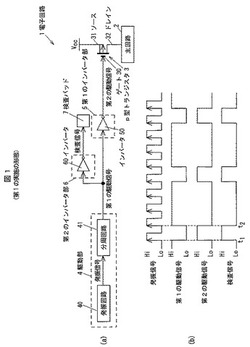

【課題】高い精度で所定の検査を行うことができる電子回路を提供する。

【解決手段】本実施の形態に係る電子回路1は、図1(a)に示すように、主に、主回路2への電圧Vccの供給を切り替えるスイッチ素子としてのp型トランジスタ3と、p型トランジスタ3を駆動する第1の駆動信号を出力する駆動部4と、入力側が駆動部4に電気的に接続され、出力側がp型トランジスタ3に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて第2の駆動信号を出力する第1のインバータ部5と、入力側が駆動部4に電気的に接続され、駆動部4から出力された第1の駆動信号に基づいて検査のための検査信号を出力する第2のインバータ部6と、第2のインバータ部6の出力側に電気的に接続され、検査信号を出力する第1のパッドとしての検査パッド7と、を備えて概略構成されている。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

制御信号発生回路およびそれを用いた半導体装置

【課題】半導体装置の制御に好適な制御信号発生回路を提供する。

【解決手段】ジョンソンカウンタ31は、フリップフロップFF1〜FF4およびゲート回路41〜44を含み、順次入力されるスタート信号ST1〜ST4に応答してそれぞれ制御信号C1〜C4を「H」レベルにした後、順次入力されるストップ信号SP1〜SP4に応答してそれぞれ制御信号C1〜C4を「L」レベルにする。したがって、多数のフリップフロップを用いることなく、所望の時間間隔で制御信号C1〜C4を順次「H」レベルにし、順次「L」レベルにすることができる。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

論理回路および半導体装置

【課題】微細化に適し、且つ演算処理を行う各種論理回路において、演算処理を実行中に電源をオフする場合でも、電源をオフする直前に入力された電位を保持できる論理回路を提供することである。また、該論理回路を有する半導体装置を提供することである。

【解決手段】入力端子および出力端子と、入力端子および出力端子に電気的に接続された主要論理回路部と、入力端子および主要論理回路部に電気的に接続されたスイッチング素子を有し、スイッチング素子の第1端子は入力端子と電気的に接続されており、スイッチング素子の第2端子は主要論理回路を構成する1以上のトランジスタのゲートと電気的に接続されており、スイッチング素子は、オフ状態におけるリーク電流がチャネル幅1μmあたり1×10−17A以下のトランジスタとする論理回路である。また、このような論理回路を有する半導体装置である。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

電源回路

【課題】本発明は、電源回路を提供することを目的とする。

【解決手段】本発明の電源回路は、複数のロードに電力を供給するために用いられ、複数の制御端を有する制御回路、第一電力供給回路、第二電力供給回路及び第三電力供給回路を備え、各々の電力供給回路は、それぞれ制御回路の1つの制御端に接続され、各々の電力供給回路は、全てスイッチングユニットを備え、スイッチングユニットは、第一端、第二端、第一端と第二端との間の接続及び切断を制御するスイッチング端を備え、第一端は、電源に接続され、第二端は、1つのロードに接続され、スイッチング端は、制御端に接続され、第二電力供給回路及び第三電力供給回路は、全て遅延回路をさらに備え、遅延回路は、制御回路の制御端とスイッチングユニットのスイッチング端との間に接続され、第三電力供給回路の遅延回路の遅延時間は、第二電力供給回路の遅延回路の遅延時間より大きい。

(もっと読む)

半導体装置

【課題】電源制御領域を電源遮断状態から電源供給状態に切り換えた際に生じる突入電流と電源ノイズを低減した半導体装置を提供する。

【解決手段】第1、第2のスイッチセルSWa、SWbと、を有し、第1のスイッチセルSWaは、制御信号CNTに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第1のスイッチトランジスタ11と、制御信号CNTを伝達する第1の信号伝達部と、を有し、第2のスイッチセルSWbは、制御信号CNTの論理レベルに応じてグローバル電源配線GVDDからローカル電源配線LVDDへの電源電圧の供給を開始する第2のスイッチトランジスタ21と、ローカル電源配線LVDDの電圧値が閾値電圧に達するまでの期間、制御信号CNTの後段回路への伝達を遮断する第2の信号伝達部と、を有する。

(もっと読む)

半導体集積回路装置

【課題】 集積回路における時間的に変動するばらつきを検出する回路を提供する。

【解決手段】 集積回路内に検出回路100、演算回路101、ばらつき/電圧変換回路113とを設ける。検出回路100において集積回路の特性ばらつきを検出回路100の出力信号の発振周波数として検出する。演算回路101では、タイマ106にて規定した時間間隔毎に検出したばらつき情報をレジスタ111に格納し、統計演算回路112にて統計処理を施し、集積回路の時間的に変動する特性ばらつきを検出する。更に、ばらつき/電圧変換回路113は、検出された特性ばらつきに対応した電圧情報に変換する。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

半導体装置

【課題】 単極性のトランジスタを用いたデジタル回路であっても、出力信号の振幅が小さくなってしまうことを防ぎ、正常に動作する手段を有する半導体装置を提供する。

【解決手段】 ダイオード接続されたトランジスタ101がオフすることによって、トランジスタ102のゲートが、フローティング状態となる。そのとき、トランジスタ102は、オン状態にあり、そのゲート・ソース間には電位差が生じている。

トランジスタ102がオン状態にあるため、トランジスタ102のソースの電位は上昇するが、トランジスタ102のゲート・ソース間の容量によって、ゲート・ソース間の電位が保持されており、かつトランジスタ102のゲートはフローティングとなっているため、容量結合効果によってトランジスタ102のゲートの電位も上昇する。その結果、出力信号の振幅が小さくなることを防ぐことが出来る。

(もっと読む)

半導体回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)が高く、消費電力が少なく、端子数および配線数が少ない回路を提供する。

【解決手段】半導体回路は、複数個のNOT回路が縦続接続され、最終段のNOT回路の出力端子と初段のNOT回路の入力端子とが接続されている。NOT回路は、ゲート11とソース13とが一体構造で形成され、ゲート10が入力端子3に接続され、ドレイン12が出力端子5に接続され、ゲート11およびソース13がグランド端子6に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23が一体構造で形成され、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子4に接続された自己バイアス型インプレーントランジスター2とから構成される。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路の出力信号のノイズを低減する。

【解決手段】一つの実施形態によれば、レベルシフト回路は第一及び第二のレベル変換部が設けられる。第一の出力加速回路は、レベルシフトされた第一の入力信号の立ち上りエッジを制御し、信号変化部分が多段階に分割された第一の信号を生成する。第二の出力加速回路は、レベルシフトされた第一の入力信号の立ち下りエッジを制御し、信号変化部分が多段階に分割された第二の信号を生成する。第三の出力加速回路は、レベルシフトされた第二の入力信号の立ち上りエッジを制御し、信号変化部分が多段階に分割された第三の信号を生成する。第四の出力加速回路は、レベルシフトされた第二の入力信号の立ち下りエッジを制御し、信号変化部分が多段階に分割された第四の信号を生成する。

(もっと読む)

演算およびスリープ・モード中のデータ格納回路並びに方法

【課題】スリープ・モード中に信号を格納するための回路を提供する。

【解決手段】スリープ信号を受け取るスリープ信号入力と、クロック信号を受け取るクロック信号入力と、クロック信号でクロックされる複数のラッチと、クロック信号でクロックされるトライステート素子であって、トライステート素子は1つの入力に、少なくとも1つの格納ラッチが接続され、格納ラッチは複数のラッチの1つであり、トライステート素子は格納ラッチの入力を、予め定められたクロック信号値に応答して選択的に分離するトライステート素子とを含み、回路への電源供給が、スリープ信号に応答して、回路の少なくとも1部の電圧差が低減されて回路の部分の電源が遮断され、格納ラッチに掛かる電圧差が維持され、トライステート素子で受け取られるクロック信号が予め定められた値に保持されて、格納ラッチの入力が分離される。

(もっと読む)

レベルシフト回路

【課題】消費電流の増加を抑制しつつ電源投入時にレベルシフタの状態を確定させる技術を提供する。

【解決手段】信号レベル変換部(11)と、安定化回路(12)とを具備するレベルシフト回路を構成する。安定化回路(12)は、第2電源電圧供給ノード(ND1)と接続ノード(ND2)との接続を制御する第1スイッチ(P3)と、接続ノード(ND2)電圧に応答して接地電圧供給ノード(GND)と出力ノード(ND3)との接続を制御する第2スイッチ(N3)とを備えることが好ましい。そして、第1スイッチ(P3)は、第2電源電圧(VDD)が、第1中間電圧を超えないときに、第2電源電圧供給ノード(ND1)と接続ノード(ND2)とを接続する。また、第2スイッチ(N3)は、第2電源電圧供給ノード(ND1)の電圧に応答して、出力ノード(ND3)と接地電圧供給ノード(GND)とを接続する。

(もっと読む)

定電圧回路とその半導体装置

【課題】 ツェナーダイオードと同等の動作を行える回路ないしは半導体装置を提供することを目的とする。

【解決手段】 実施形態の基準電圧発生回路は、第1のFETと、第2のFETと、一方を電源に接続し他方を前記第1のFETのドレインに接続した第1の抵抗と、前記第1のFETのドレイン−ゲート間に接続した第2の抵抗とを有し、前記第2のFETのゲート−ソース間を接続し、前記第2のFETのドレインを前記第1のFETのゲートに接続し、前記第1のFETのドレインが基準電圧を出力し、前記第1のFETのソースと前記第1のFETのソースがグランド又は他の回路と接続していることを特徴とする。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

双方向レベルシフト回路

【課題】高速に信号の伝達が可能な双方向レベルシフト回路を提供する。

【解決手段】実施形態によれば、第1の回路と、第2の回路と、第3の回路と、第4の回路と、を備えた双方向レベルシフト回路が提供される。前記第1の回路は、双方向に信号を伝達する。前記第2の回路は、前記第1の回路の両端の電位の変化に基づいて前記第1の回路の伝達方向を検出する。前記第3の回路は、前記第1の回路の両端の電位のいずれかがローレベルからハイレベルに上昇してから、前記第1の回路の両端の電位のいずれもがハイレベルになるまでの第1の期間を検出する。前記第4の回路は、前記第1の回路の両端にそれぞれ接続され、前記第1の回路の出力側に前記第1の期間ハイレベルの電位を供給する。

(もっと読む)

レベル変換回路及び半導体装置

【課題】低面積化を図ること。

【解決手段】各信号BDT1〜BDTmをレベルシフトする回路として、クロックトレベルシフト回路(CLS回路)36(361〜36m)を用いた。CLS回路361は、ダイナミックコンパレータ回路(DC回路)411と、ラッチ回路421とを備える。DC回路411は、Lレベルのクロック信号ACKに応答してリセット状態となり、Lレベルの信号CDTm,XCDTmを出力する。また、CLS回路361は、Hレベルのクロック信号ACKに応答して比較状態となり、H1レベルの信号BDTm,XBDTmをH2レベルの信号CDTm,XCDTmにレベル変換する。ラッチ回路421は、相補な信号CDTm、XCDTmに応じた信号ADTm,XADTmを出力し、Lレベルの信号CDTm,XCDTmに応答して出力レベルを保持する。

(もっと読む)

21 - 40 / 578

[ Back to top ]