Fターム[5J079BA41]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 低消費電力化 (202)

Fターム[5J079BA41]の下位に属するFターム

動作電圧低減 (41)

Fターム[5J079BA41]に分類される特許

1 - 20 / 161

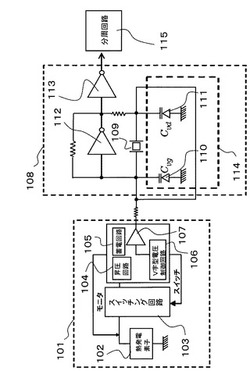

熱発電型携帯機器

【課題】消費電力を低減でき、さらには電気的ノイズも少ない計時用水晶発振回路、さらに時計用水晶発振回路の温度補償法を行う熱発電型携帯機器を提供する事を目的とする。

【解決手段】水晶振動子109を有する水晶発振回路108と、熱源と温度差とに基づき発電する熱発電素子102と、熱発電素子から出力される発電電圧から制御電圧を生成し、制御電圧の値に基づいて水晶発振回路108の負荷容量値を電圧制御し、水晶発振回路108の発振周波数の温度特性を制御する制御部とを有する。

(もっと読む)

発振装置

【課題】低消費電流を実現できる定電圧回路及びそれを用いた水晶発振回路を提供する。

【解決手段】定電圧回路10に温度特性調整素子を備えることにより、定電圧の温度変化に対して負となる傾きと、水晶発振回路20における発振可能な最低動作電圧の温度変化に対して負となる傾きとの差を極小にできるので、水晶発振回路20の消費電流を小さくでき、さらに定電圧回路10で生成する定電流を小さくすることにより、定電圧回路10の消費電流を小さくでき、発振装置100全体の消費電流を小さくできる。

(もっと読む)

半導体装置

【課題】消費電力の低減と、製造コストの低減とを両立する発振回路を提供する。

【解決手段】本発明の半導体装置によれば、直列に接続されて、かつ、それぞれがダイオード接続された複数のMOSトランジスタを用いて、発振回路部を駆動させる電圧を生成する。このとき、複数のMOSトランジスタで生成される電圧の値は、電源電圧と、各MOSトランジスタのスレッショルド電圧の比率とに基づいて得られる。したがって、各MOSトランジスタのスレッショルド電圧を小さく抑えることが出来て、各MOSトランジスタの面積を節約することが出来て、発振回路部の消費電力を削減することが出来る。

(もっと読む)

振動子ユニット、発振回路及び受信回路

【課題】共振子を接続して発振回路を完成するように設計された集積回路に、温度補償を得るためにTCXOを接続すると消費電力が大きくなる。

【解決手段】振動子ユニット20は水晶振動子Xtalを含んで一体に構成され、Xtalの両端子を外部回路に接続するための外部接続端子N1,N2を備える。振動子ユニット20は、Xtalに接続された可変容量キャパシタCVと、CVの容量を制御する温度補償部28とを有する。温度補償部28はXtalの近傍における温度を検知する温度センサ回路30を備え、振動子ユニット20の外部からのトリガ信号の入力に応じて、温度センサ回路30の検知出力に基づいてCVの容量を調節する。

(もっと読む)

発振装置

【課題】消費電力が少なく、高い周波数精度を保持することを可能にする。

【解決手段】発振装置1は、恒温槽付水晶発振器であるOCXO15と、温度補償水晶発振器であるTCXO16とを有しており、CPU11により、OCXO15で基準精度以上のクロック周波数が得られない場合にTCXO16をオンとして使用し、OCXO15をオフとする制御手段を有する。制御手段は、発振装置1起動時にTCXO16のみをオンとして使用し、OCXO15の温度が基準精度以上のクロック周波数が得られる状態に上昇した際に、TCXO16をオフとし、当該OCXO15をオンすることを特徴とする。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。更に前記温度検出値に基づいて、OCXOの設定周波数を補正し、雰囲気温度が基準温度からずれたことによる周波数の変動分を補償するようにする。

(もっと読む)

温度補償発振器および電子機器

【課題】より低消費電力で、起動時の周波数変動を抑制すること。

【解決手段】温度補償発振器は、第1入力端子から入力された温度補償電圧に応じた周波数で発振した基準信号を第1出力端子から出力する発振回路と、第2入力端子から入力された基準信号に基づいて周波数補償量を示す補正データを第2出力端子から出力する補償回路と、補償回路内に設けられ、第3入力端子に第1レベルの信号が入力されている間は基準信号をN分周した信号を第3出力端子から出力し、第3入力端子に第2レベルの信号が入力されると動作を停止する分周器と、補償回路内に設けられ、第4入力端子から入力された信号をクロック信号として動作し、クロック信号を基準として所定の時間が経過すると第2レベルの信号を第4出力端子から出力するカウンター回路とを有する。

(もっと読む)

発振器

【課題】 スタンバイ機能を備えた小型のVCXOを、簡易な構成且つ低コストで実現して、小型VCXOの用途を拡大することができる発振器を提供する。

【解決手段】 小型のVCXO1の下に、スタンバイICを内蔵したスタンバイベース2を積層して接着し、VCXO1の底面部に、入力端子と、グランド端子と、発振出力端子と、電源端子とを備え、スタンバイベース2の上面部に上記各端子に対応する端子を備え、底面部に、入力端子(#1)と、グランド端子(#3)と、発振出力端子(#4)と、電源端子(#6)と、スタンバイ制御信号を入力するスタンバイ端子(#2)を備え、VCXO1の発振出力端子とスタンバイベース2の発振出力端子34との間にスタンバイIC41を接続し、電源端子36とスタンバイ端子32との間に第1の抵抗42を接続し、スタンバイIC41の出力と発振出力端子34との間に第2の抵抗43を接続した発振器としている。

(もっと読む)

圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

(もっと読む)

水晶発振器

【課題】各々出力される信号に対して間欠動作を行い、消費電力を抑えた水晶発振器を提供する。

【解決手段】電源電圧が印加される電源電圧印加端子111と、電源電圧印加端子に接続される温度補償型水晶発振回路部110と、温度補償型水晶発振回路部及び電源電圧印加端子に接続される第一の緩衝増幅部120と、第一の緩衝部に接続され第一の緩衝部から信号が入力される第一の信号出力端子121と、第一の緩衝増幅部に接続され、第一の緩衝増幅部が動作又は停止する様に制御できる信号が入力される第一のE/D端子122と、温度補償型水晶発振回路部及び第一の緩衝増幅部に接続されている第二の緩衝増幅部130と、第二の緩衝増幅部に接続され第二の緩衝増幅部から信号が入力される第二の出力端子131と、第二の緩衝増幅部に接続され第二の緩衝増幅部が動作又は停止する様に制御できる信号が入力される第二のE/D端子132と、を備えている。

(もっと読む)

圧電発振器

【課題】同一のICを用いて広範囲の周波数に対応した圧電発振器を得る。

【解決手段】圧電振動子と、発振回路と、定電流回路と、メモリ回路と、を備えた圧電発振器であって、前記発振回路は、トランジスタのコレクタとベースとの間にコレクタ電位を決める第1の可変抵抗回路を有し、前記定電流回路は、複数のカレントミラー回路からなり、出力電流に関わるカレントミラー回路のトランジスタ素子に第2の可変抵抗回路が接続され、前記メモリ回路の出力部は、前記発振回路の第1の可変抵抗回路と、前記定電流回路の第2の可変抵抗回路と、に信号線で接続され、前記定電流回路の出力電流を制御し、前記トランジスタのコレクタ電位を制御する圧電発振器を構成する。

(もっと読む)

電子回路

【課題】容量を可変させることで発振回路の周波数を調整できる周波数調整機能を有する電子回路を提供する。

【解決手段】電子回路は、複数のスイッチ回路140,141,142,143それぞれに副スイッチ回路150,151,152,153を備えている。この副スイッチ回路は、スイッチ回路と相反する動作を行う。このため、スイッチ回路がオン又はオフする数にかかわらず、発振回路の増幅用アンプ181の入力線184又は出力線185に接続される寄生容量が一定となるため、発振回路の発振周波数を正しく調整できる。

(もっと読む)

回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

(もっと読む)

水晶発振回路における負荷容量の決定方法、水晶発振回路における負性抵抗RLの決定方法、発振回路、及び電子機器

【課題】本発明の目的は、低い負荷容量有する水晶発振回路において、負荷容量、及び負性抵抗RLを決定する決定方法を提供するものである。

【解決手段】(CLn+1/CLn)2=α(nは1以上の整数、α=2-1/2)が成立するように、負荷容量CL1に対して負荷容量CLn(n≧2)を決定する。さらに、CMOSインバータの入力側と出力側の間に最小帰還抵抗Rfminと並列に配置されたリーク抵抗Rzを仮想して、最小合成帰還抵抗RFminを式RFmin=(Rfmin×Rz)/(Rz+Rfmin)を用いて決定し、最大負性抵抗RLmaxの値を、式(RLmax/RFmin)1/2 <α(αは安全係数で2-1/2)を用いて決定する。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

発振回路及び発振回路を搭載した電子機器

【課題】本発明の目的は、水晶発振回路の駆動電流が100nA以下と非常に小さくなり、水晶発振回路の出力が0.1Vpp以下と小さくなっても、水晶発振回路の出力に接続する次段の種々の回路が正常に動作する出力信号を出発振回路、及びそれを搭載した電子機器を提供する。

【解決手段】水晶発振回路の出力を増幅する増幅回路を水晶発振回路の出力側に接続し、水晶発振回路の出力電圧と水晶発振回路のCMOSインバータの入力電圧との差を増幅させる。たとえば、差動アンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧とCMOSインバータの入力電圧とを差動アンプの入力とする。あるいは、3つのオペアンプから構成されるインスツルメンテーションアンプを水晶発振回路の出力側に接続し、水晶発振回路の出力電圧信号と水晶発振回路のCMOSインバータの入力電圧信号との差を増幅させる。

(もっと読む)

圧電振動回路

【課題】発振波形の歪みを小さくし、消費電流も少なく、且つ発振の起動時間も短くて、外部電源変動等に優れた発振回路の提供。

【解決手段】インダクタンスを能動素子と静電容量、抵抗によって発生させた負性静電容量で置き換えた圧電発振器において、第1のロジックインバータIC1の出力は第2のロジックインバータIC2の入力に接続し、第1のロジックインバータの入出力間に第2の抵抗R2を挿入し、第1のロジックインバータの入力と接地間へ第2のコンデンサC2、第1のロジックインバータの出力と第2のロジックインバータ入力の接続点と接地間に第4のコンデンサC4、第2のロジックインバータの出力と接地間に第3のコンデンサC3を挿入し、第1、第2のロジックインバータの接地端子と接地間へは抵抗R3、R5を同様に電源端子と電源間へも抵抗R4、R6を挿入し、電源と接地間に交流時短絡となるコンデンサC5,C6を挿入する。

(もっと読む)

電子回路

【課題】発振回路部の信号反転素子及びインターフェース回路部のインターフェース回路部のインターフェース集積回路素子で消費される電流を抑えて消費電力が少ない電子回路を提供する。

【解決手段】発振回路部とインターフェース回路部と被駆動回路部と備えた電子回路であって、発振回路部用電源電圧印加端子と発振回路部の間に発振回路部用電流制限抵抗が設けられ、インターフェース回路部用電源電圧印加端子とインターフェース回路部との間にインターフェース回路部用電流制限抵抗が設けられ、発振回路部用電流制限抵抗の両端部からグランドに接続されている第一のコンデンサが設けられ、インターフェース回路部用電流制限抵抗の両端部からグランドに接続されている第二のコンデンサが設けられ、インターフェース回路部から出力され被駆動回路部に入力される信号電圧が被駆動回路部が動作するために必要な電圧より大きいことを特徴とする。

(もっと読む)

発振器

【課題】消費電流を増大させることなしに高速起動可能なMEMS発振器の提供。

【解決手段】ドライバアンプと、LC共振回路を備える第1共振器と、MEMS共振器を備える第2共振器と、接続および開放を切り換え可能なスイッチ回路と、スイッチ回路を制御するスイッチ制御部と、を有するMEMS発振器であって、ドライバアンプ、第1共振器、および、スイッチ回路は、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第1閉ループ回路を形成し、ドライバアンプ、および、第2共振器は、第1閉ループ回路とは別の、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第2閉ループ回路を形成し、スイッチ制御部は、MEMS発振器の起動期間の少なくとも一部においてスイッチ回路を接続し、所定の条件が満たされる場合に、スイッチ回路を開放する、MEMS発振器。

(もっと読む)

1 - 20 / 161

[ Back to top ]