Fターム[5J079FA05]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路素子 (3,033) | 半導体素子 (1,687) | FET (266) | MOSFET、MISFET (171)

Fターム[5J079FA05]に分類される特許

121 - 140 / 171

発振回路

【課題】外部クロック信号の入力時における出力クロック信号のDutyの変動を抑える。

【解決手段】発振回路は、内部電源電圧に対応した振幅で発振して内部クロック信号を発生する発振部30と、スイッチ28,29と、トレラント入力回路用のNMOS13と、初段ドライバ15と、カップリング容量27とを有している。スイッチ28,29は、外部クロック信号がクロック端子1,2に入力される時にはオフ状態になり、発振部30が発振する時にはオン状態になる。NMOS13は、入力クロック信号の振幅をオン抵抗値により変化させてドレイン電極から出力する。初段ドライバ15は、NMOS13のドレイン電極の出力を駆動してクロック信号を出力する。カップリング容量27は、入力クロック信号の立ち上がりの際にNMOS13のゲート電圧を変化させて前記オン抵抗値を一定に保つ。

(もっと読む)

発振回路およびその制御方法

【課題】増幅手段の駆動電力を連続制御し、発振起動時間の短縮や動作の安定性を確保しながら定常時の消費電力を効率的に低減することのできる発振回路およびその制御方法を提供する。

【解決手段】発振回路が駆動する負荷容量への充放電電流に応じて発振回路の駆動電力を制御することとしたため、発振起動時間や発振の安定性を犠牲にすることなく定常時の消費電力を効果的に低減することが出来る。また本発明を採用したシステムにおいては、環境の変動に応じて最適な電力を発振回路に与えることが可能となり、システム全体での省エネルギー化、電池の長寿命化が実現出来る。

(もっと読む)

発振回路

【課題】発振増幅器の出力側におけるノイズ成分の影響を抑制すると共に、所望の信号成分を得るための発振回路を提供する。

【解決手段】圧電振動子と増幅器を接続して、発振閉ループを形成してなる発振回路であって、増幅器の入力と、圧電振動子との接続点から、発振信号成分を取り出す。

(もっと読む)

発振回路

【課題】所望の周波数以外の周波数で発振するおそれがあり、また、出力される発振周波

数の波形が正弦波に近似しないことがあった。

【解決手段】第1の電位及び第2の電位間に接続されたCMOSインバータと、一端がC

MOSインバータの入力端に接続された第1の素子部と、一端がCMOSインバータの入

力端に接続され、他端がCMOSインバータの出力端に接続された第2の素子部と、一端

がCMOSインバータの出力端に接続された第3の素子部と、一端が第1の素子部の他端

及び第3の素子部の他端に接続され、他端が第1の電位及び第2の電位のうちの一方に接

続された第4の素子部とを含み、第1、第2、第3、及び第4の素子部は、水晶振動子、

抵抗器、インダクタ及びキャパシタのいずれかであり、第1、第2、及び第3の素子部に

より規定される周波数で発振する。

(もっと読む)

発振回路

【課題】従来の発振回路では、インダクタを有することから、小型化が困難であった。

【解決手段】各エミッタが実質的に接地電位に接続された第1のトランジスタ及び第2の

トランジスタと、第1のトランジスタのベース及び第2のトランジスタのベース間に接続

された水晶振動子と、第1のトランジスタのコレクタ及び電源電位間に接続された第1の

抵抗器と、第2のトランジスタのコレクタ及び電源電位間に接続された第2の抵抗器と、

第1のトランジスタのコレクタ及び第2のトランジスタのベース間に接続された第1のキ

ャパシタと、第2のトランジスタのコレクタ及び第1のトランジスタのベース間に接続さ

れた第2のキャパシタと、第1のトランジスタのベース及びエミッタ間に接続された第3

のキャパシタと、第2のトランジスタのベース及びエミッタ間に接続された第4のキャパ

シタと、を含む。

(もっと読む)

FSK送信装置

【課題】SAW素子とIC(半導体集積回路)と水晶温度センサ素子の各1チップを1個

のセラミックパッケージに収納することにより温度情報を伝達する超小形なFSK送信装

置を市場に提供すること。

【解決手段】2値の周波数信号を送信可能なFSK送信装置において、送信装置は、温度

検出用水晶振動子をもちいた発振回路から温度情報を含んで出力されたデジタル信号列に

より2値の周波数をFSK変調させる2モード発振回路が備わり、2モード発振回路はS

AW共振素子を発振させるための増幅器と、2値の発振周波数状態を切り替えるためのS

W回路からなるFSK変調回路を内蔵し、さらにFSK変調回路からの出力をアンテナに

接続して送信系を構成したことからなることを特徴とするFSK送信装置。

(もっと読む)

温度補償型水晶発振器

【課題】発振回路の出力周波数を制御する3次関数制御電圧の電圧ノイズを低減した温度補償型水晶発振器を提供する。

【解決手段】水晶振動子と、発振周波数制御装置を備えた増幅器と、水晶の発振周波数の温度補償回路と、で構成される温度補償型水晶発振器であって、前記温度補償回路の補償電圧のリファレンス電圧を、ダイオードの順方向電圧を使用して生成することを特徴とする。

(もっと読む)

発振回路

【課題】スイッチによる周波数の切り替え時に発生する発振波形の乱れを解消した発振回路を提供することにある。

【解決手段】第1のIDTとしてのIDT12aおよび第2のIDTとしてのIDT12bの極性を反転する際に、スイッチ手段としてのスイッチSW5〜SW8が遮断されて、第1のIDTとしてのIDT12aおよび第2のIDTとしてのIDT12bの並列接続状態が解除される期間である期間Tdにおいては、スイッチSW5〜SW8がすべて遮断状態となる。期間Tdを必要最小限にして十分な値に設定しておけば、何らかの要因で信号V11または信号V21のレベルが若干ずれたタイミングで切り替わったとしても、両信号が同時にハイレベルとなる事態を回避することができる。したがって、スイッチSW5とスイッチSW6、あるいは、スイッチSW7とスイッチSW8が、それぞれ同時に導通状態となることが回避される。

(もっと読む)

発振回路を内蔵した通信用半導体集積回路

【課題】 外付け部品点数が少なくて済み小型化を図ることができるとともに発振周波数の変動が少ない安定した基準発振回路を内蔵した通信用半導体集積回路(高周波IC)を提供する。

【解決手段】 複数の可変容量素子(Cv1〜Cvn)とこれらの容量素子に接続されたスイッチ素子(SW11〜SW1n)とを含む容量性負荷回路(13)を有する発振回路において、オフ状態のスイッチ素子に接続されている可変容量素子のスイッチ接続側の端子の電位を安定化させる手段(SW21〜SW2n,R6)を設けるようにした。

(もっと読む)

発振回路、物理量トランスデューサ及び振動ジャイロセンサ

【課題】 簡素な構成で、発振ループ内の振幅制御を高精度で実現し、発振の起動時間を短縮できる発振回路、物理量トランスデューサ及び振動ジャイロセンサを提供する。

【解決手段】 発振回路10は、発振ループ内の発振振幅を制御するためのゲインコントロールアンプ20と、発振振幅に応じてゲインコントロールアンプ20のゲインを調整するための制御電圧を出力するゲイン制御回路30とを含む。制御電圧をVc、ゲインをkとした場合に、発振ループ内の発振が定常状態か起動過程かにかかわらず、Vc×kの値が一定である。

(もっと読む)

発振回路

【課題】低消費電力でありながら大きな負性抵抗を得ることができる発振回路を提供する。

【解決手段】発振回路は、SAW振動子Xと、SAW振動子Xと信号路を介して並列接続され発振駆動されるCMOSインバータA1〜A3と、CMOSインバータA1〜A3の出力側と入力側との間に、CMOSインバータA1〜A3の出力側から入力側に信号が正帰還するように、接続された負性抵抗増加回路10と、負性抵抗増加回路10とCMOSインバータA1〜A3の入力側との間に接続する容量素子としての帰還用コンデンサCfと、を含む。

(もっと読む)

発振器の検査方法

【課題】擬似切断モード時にヒューズ切断モードになることを防止する。

【解決手段】nビット(nは任意の自然数)の不揮発性メモリと、nビットの不揮発性メ

モリと対を成すnビットのフリップフロップ回路と、データを不揮発性メモリに書き込む

不揮発性メモリ選択信号、または、データをフリップフロップ回路に書き込むフリップフ

ロップ選択信号を送信する選択信号線と、を有する発振器の検査方法において、選択信号

線に不揮発性メモリ選択信号を送信し、nビットの不揮発性メモリの所定のビットをチェ

ック用ビットとし、チェック用ビットの不揮発性メモリにチェック用データを書き込む第

1の工程と、チェック用ビットの不揮発性メモリのデータがチェック用データと等しいか

否か判定する第2の工程と、第2の工程で等しいと判定された場合、選択信号線にフリッ

プフロップ選択信号を送信し、フリップフロップ回路にデータを書き込む第3の工程と、

からなる。

(もっと読む)

電圧制御型発振器

【課題】温度補償制御信号および外部電圧周波数制御信号とは独立してMOSトランジスタの閾値電圧を制御可能でかつ、周波数の可変範囲を低下させることなく直線性も確保し、小型化を図ることのできる電圧制御型発振器を提供する。

【解決手段】増幅器と、圧電振動子と、前記圧電振動子の両端子間に、負荷容量1と負荷容量2を設け、前記負荷容量1として設けられた容量は、入力電圧に対して容量値変化の小さい可変容量で構成され、前記負荷容量2として設けられた容量は、入力電圧に対して容量値変化の大きい可変容量で構成する。

前記負荷容量1および2の制御端子に高周波除去抵抗を介し、温度補償制御信号と外部電圧周波数制御信号を重畳した信号を入力する。これにより、温度補償制御回路や外部電圧周波数制御回路の出力バイアスを任意に決定できる。

(もっと読む)

発振回路

【課題】 発振特性の変動が少なく、また、低電圧からの安定発振を可能とする発振回路を提供する。

【解決手段】 インバータ回路と、インバータ回路に並列に接続された帰還抵抗と、帰還抵抗の一端と電源との間に接続された第1の容量と、帰還抵抗の他端と電源との間に接続された第2の容量とを有し、前記インバータ回路に水晶振動子を並列に接続することにより発振出力を生成する発振回路において、前記インバータ回路は、電源電圧と定電圧との間に直列に接続されたPchMOSトランジスタおよびNchMOSトランジスタと、第3の容量とを有し、これらトランジスタのうち前記定電位に電流通路の一端が接続された方のトランジスタのゲートに前記第3の容量を介してインバータ回路の入力信号が与えられる。

(もっと読む)

FSK変調器

【課題】FSK変調器において、周波数の切り替え時における出力振幅の変動を低減する。

【解決手段】圧電体平板上に形成した2個の振動状態を有するSAW共振子と、増幅器とSW回路からなるFSK変調器において、前記SAW共振子は、主IDT、ゲイトIDT、副IDT、1対の反射器で構成した2ポート型のSAW共振子からなり、かつ前記主IDTと前記副IDTの極性をSW回路にて同符号として発振器の増幅器に接続して第1の発振周波数fHを発生し、また前記主IDTと前記副IDTの極性を前記のSW回路にて逆符号として発振器の増幅器に接続して第1と若干異なる第2の発振周波数fLを発生する構成とした。

(もっと読む)

発振回路

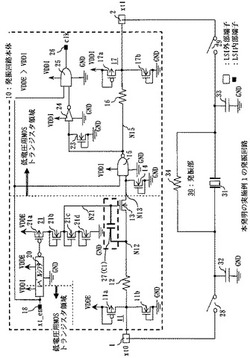

【課題】本発明は発振回路部の発振出力をバッファするバッファアンプを有する発振回路に関し、安定した発振出力を高速に出力することが可能な発振回路を提供することを目的とする。

【解決手段】本発明は、発振回路部と、発振回路部の発振出力を出力する出力アンプとを有する発振回路において、発振回路部の起動電圧と出力アンプの起動電圧との異なる電圧とし、発振回路部が起動した後に出力アンプが起動するようにしたことを特徴とする。

(もっと読む)

交流増幅器及び圧電振電子発振器

【課題】

交流増幅器の低電圧動作を損なうことなく、消費電流を低減でき、かつ出力信号波形のデュティーのずれが少なく、更に十分な増幅特性を有する交流増幅器を提供する。

【解決手段】 連結配線Ndで結ばれた増幅回路AP1とバイアス回路VS1を有し、バイアス回路VS1は前記連結配線Ndを介して前記増幅回路AP1の前記交流信号を入力し、増幅回路AP1の交流信号の振幅に応じたバイアス回路VS1の直流電圧を連結配線Ndを介して増幅回路AP1へ供給する交流増幅器とした。

(もっと読む)

発振回路

【課題】 システムLSI13に高速クロックを供給する手段を少ない回路及び回路素子で構成し、回路規模を増大させず、環境に配慮し、低消費電力を達成できる発振回路を提供する。

【解決手段】 共振回路14またはLSIテスタが外部接続される第1及び第2接続端子9、10、システムLSI13に接続される接続端子11、第1及び第2接続端子9、10間に接続された第1転送回路4と第1インバータ2の第1直列接続回路、第1直列接続回路に並列接続された負帰還抵抗3、第1インバータ2の出力端と接続端子11間に接続された第2転送回路6と第2インバー5の第2直列接続回路、第1接続端子9と接続端子11間に接続された第3転送回路8と第3インバータ7の第3直列接続回路を備え、第1〜第3転送回路2、5、7は、ゲートに相補TE信号が供給される相補MOSトランジスタの並列回路からなり、第1及び第2転送回路2、5に供給される相補TE信号の極性と第3転送回路7に供給される相補TE信号の極性とが逆極性になる。

(もっと読む)

集積回路

【課題】従来の発振器用集積回路では、低振幅の出力波形を要求された場合に、出力増幅回路トランジスタ対のゲート・ソース間電圧が十分に確保できず、大きな負荷を駆動できないという問題があった。

【解決手段】 出力増幅回路112のPチャネルトランジスタ110およびNチャネルトランジスタ111のゲートを、コンデンサ106および107により発振回路104の出力に交流的に結合するとともに、抵抗108および109を介してPチャネルトランジスタ110のゲートはGND電位に、Nチャネルトランジスタ111のゲートは電源電位にバイアスされていることにより、これらのトランジスタのゲート・ソース間電圧が充分に確保され、大きな負荷を駆動できるようにしたことを特徴とする集積回路。

(もっと読む)

水晶発振器

【課題】 用途に応じて出力波形を変更することができる水晶発振器を提供する。

【解決手段】 水晶振動子2と発振回路とを備えた水晶発振器8において、複数の異なる波形を出力する複数の波形出力回路10〜12と、発振回路8の出力回路として、複数の波形出力回路10〜12からの何れか一つを選択するスイッチSW1a、SW1a〜SW3a、SW3bと、スイッチSW1a、SW1a〜SW3a、SW3bを選択するためのデータを記憶する内部メモリ回路6とを備えるようにした。

(もっと読む)

121 - 140 / 171

[ Back to top ]