Fターム[5J079FA05]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路素子 (3,033) | 半導体素子 (1,687) | FET (266) | MOSFET、MISFET (171)

Fターム[5J079FA05]に分類される特許

21 - 40 / 171

発振器

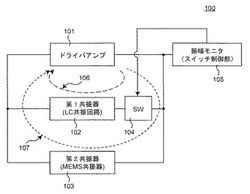

【課題】消費電流を増大させることなしに高速起動可能なMEMS発振器の提供。

【解決手段】ドライバアンプと、LC共振回路を備える第1共振器と、MEMS共振器を備える第2共振器と、接続および開放を切り換え可能なスイッチ回路と、スイッチ回路を制御するスイッチ制御部と、を有するMEMS発振器であって、ドライバアンプ、第1共振器、および、スイッチ回路は、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第1閉ループ回路を形成し、ドライバアンプ、および、第2共振器は、第1閉ループ回路とは別の、ドライバアンプの出力信号の少なくとも一部をドライバアンプへ帰還させる第2閉ループ回路を形成し、スイッチ制御部は、MEMS発振器の起動期間の少なくとも一部においてスイッチ回路を接続し、所定の条件が満たされる場合に、スイッチ回路を開放する、MEMS発振器。

(もっと読む)

発振回路及び電子機器

【課題】本発明の目的は、実装基板に配置される水晶発振回路における浮遊容量Csを低減する手段を提供することである。

【解決手段】本発明は、発振回路を構成するCMOSインバータの入出力端子間に接続する水晶振動子と、前記CMOSインバータの入力端子パッドへ接続する前記水晶振動子側の入力端子を含む入力配線ラインと、前記CMOSインバータの出力端子パッドへ接続する前記水晶振動子側の出力端子を含む出力配線ラインと、前記水晶振動子側の接地電源端子を含む接地電源配線ラインと、前記入力配線ラインと前記接地電源配線ラインとの間、及び前記出力配線ラインと前記接地配線ラインとの間に接続された容量素子と、を有する発振回路において、前記入力配線ラインと前記出力配線ラインとの間の少なくとも一部に前記接地電源配線ラインが配置されていることを特徴とする。

(もっと読む)

水晶発振回路の負荷容量の決定方法およびそれを用いた電子機器

【課題】本発明の目的は、水晶振動子を用いた発振回路の発振起動時間と負荷容量CL値の関係を明確にし、所望の発振起動時間から負荷容量CL値を決定することである。

【解決手段】本発明は、水晶振動子を用いた発振回路において、発振起動時間Tsと発振余裕度Mの関係式又は関係グラフを用いて発振余裕度Mから発振起動時間Ts(Ts0)を求める手段(A)と、発振起動時間Tsと負荷容量CLの関係式、及び駆動電流値Iosから、任意の駆動電流値Iosにおける発振起動時間Tsと負荷容量CLの関係式を求める手段(B)と、前記手段(B)において求められた発振起動時間Tsおよび負荷容量CLの関係式を用いて、前記手段(A)で求められた発振起動時間Ts0に対応する負荷容量CLを決定する手段(C)と、を含むことを特徴とする。

(もっと読む)

発振装置および該発振装置を具備したクロック発生装置、半導体装置、ならびに電子装置

【課題】過渡的な電力消費をしないピークホールド回路(あるいはボトムホールド回路)を用いることで、無駄な電力消費を抑えるとともに、ノイズの発生を抑えて発振特性の悪化を防止することが可能な発振装置技術を提供。

【解決手段】基準電圧を発生する定電圧発生回路4と、駆動電圧または駆動電流によって発振する発振回路1と、発振回路1の出力である発振信号のピークレベルを検出して出力するピークホールド回路2と、定電圧発生回路4で発生された基準電圧VREFとピークホールド回路2で出力されたピークレベルPHに応じて駆動電圧または駆動電流を増減させて発振回路1の電源端子VRに入力するレギュレータ3からなる。ピークホールド回路2は定電流で動作し過渡的な電力を消費しない構成となっている。なお、ピークホールド回路2の代わりにボトムホールド回路を用いても良い。

(もっと読む)

発振回路

【課題】発振子に供給する信号の振幅レベルを正しく測定することができる発振回路の提供を図る。

【解決手段】発振子3に第1発振信号を供給する第1ノードBと、該発振子から第2発振信号を受け取る第2ノードAと、前記第2発振信号を増幅し、前記第1発振信号を生成する発振部6と、前記第1発振信号の振幅レベルを検出するために、観測ノードBにおける観測信号の振幅レベルを検出する検出器8と、を有する。

(もっと読む)

電圧制御発振器

【課題】回路規模の増大を抑制しつつ、広範囲の制御電圧に対して発振周波数を直線的に変化させることが可能な電圧制御発振器を提供すること。

【解決手段】本発明にかかる電圧制御発振器は、増幅器11と、増幅器11に並列に接続され帰還ループを構成する水晶振動子13と、水晶振動子13に対して負荷する容量値が制御電圧VCに応じて変化する可変容量部15,17と、制御電圧VCを生成する制御電圧生成回路14と、を備える。また、可変容量部15は、固定容量152と、固定容量152と直列に接続され制御電圧VCに応じて導通状態が制御されるディプレッション型のトランジスタ151と、を有する。可変容量部17は、固定容量172と、固定容量172と直列に接続され制御電圧VCに応じて導通状態が制御されるエンハンスメント型のトランジスタ171と、を有する。

(もっと読む)

発振回路

【課題】周波数の校正を簡単に且つ高精度に可能な発振回路の提供。

【解決手段】圧電振動子4の両端に接続された入力端子と出力端子を有する第1のインバータ回路1と,第1のインバータ回路の入出力端子間に設けられた第1のフィードバック抵抗3と,第1のインバータ回路の入出力端子に各々接続され,制御信号により容量値が可変設定可能な第1、第2の可変容量素子2a、2bと,所定基準電流を入力端子又は出力端子に供給して第1または第2の可変容量素子を充電する充電回路10と,入力端子又は出力端子の充電電圧と,参照電圧VRとを比較する比較器11と,キャリブレーション時に,第1の時間で,充電回路に入力端子又は出力端子への基準電流の供給を開始させ,第1の時間後の第2の時間での比較器の比較結果に応じて,充電電圧が参照電圧に近づく様に,第1又は第2の可変容量素子の容量値を設定する制御信号生成の制御回路12とを有する発振回路。

(もっと読む)

水晶発振回路

【課題】出力波形の歪みを低減する水晶発振回路を提供する。

【解決手段】正・負電源ライン間に接続されたnMOSM4・pMOSM5と、nMOSM4・pMOSM5にバイアスを与えるnMOSM2・pMOSM3と、nMOSM4・pMOSM5の中心点と正・負電源ライン間に接続されたキャパシタC22・C24と、正・負電源ライン間に接続されたnMOSM14・pMOSM15と、nMOSM14・pMOSM15にバイアスを与えるnMOSM12・pMOSM13と、nMOSM14・pMOSM15の中心点と正・負電源ライン間に接続されたキャパシタC23・C25と、nMOSM2・pMOSM3の中心点とnMOSM12・pMOSM13の中心点との間に接続された水晶振動子X1とを備える。

(もっと読む)

圧電発振器、圧電発振器の温度補償方法

【課題】圧電発振器、圧電発振器の温度補償方法を提供する。

【解決手段】圧電振動子12と、前記圧電振動子12を発振させ発振信号を出力する発振回路14と、前記発振回路14を構成し、前記発振信号の周波数を調整する負荷容量20と、前記発振回路14に組み込まれたMOSFET22と、を有し、前記MOSFET22は、前記MOSFET22のドレイン端子24と前記MOSFET22のソース端子26とを結ぶ前記MOSFET22中の経路を前記負荷容量20に直列に接続することにより前記発振回路14に組み込まれ、前記MOSFET22のゲート端子28には、前記経路を半導通状態にするゲート電圧Vbが印加され、前記半導通状態時の前記経路のオン抵抗の温度特性により発生する前記発振回路14から見た前記負荷容量20の増加分の温度特性により前記発振信号の温度補償を可能とすることを特徴とする。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

集積回路装置及び電子機器

【課題】発振回路の性能を維持しながら静電気保護耐圧を向上できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、振動子XTALの一端に接続される第1のパッドP1と、振動子XTALの他端に接続される第2のパッドP2と、振動子XTALの発振用のバッファー回路BFと、第1のパッドP1側の第1の接続ノードNC1と、バッファー回路BFの入力ノードNIとの間に設けられる第1の保護抵抗素子R1と、第2のパッドP2側の第2の接続ノードNC2と、バッファー回路BFの出力ノードNQとの間に設けられる第2の保護抵抗素子R2と、第1、第2の接続ノードNC1、NC2の一方に接続される容量回路CX1(CX2)とを含む。

(もっと読む)

低消費電力回路

【課題】起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】第1発振トランジスタP31、第1発振トランジスタP31のドレイン端子にドレイン端子を接続した第2発振トランジスタN31、第1容量C2、第1容量C2に一方を接続し、他方を第1発振トランジスタP31と第2発振トランジスタN31の接続ノードに接続した圧電振動子Q1、一方を圧電振動子Q1に接続し、他方を第1発振トランジスタP31のゲート端子に接続した帰還抵抗回路Z3、第1発振トランジスタP31のゲート端子VP1に第1端子を接続し、接続ノードに第2端子を接続した第1振幅制限素子P32、第2発振トランジスタN31のゲート端子VN1に第2端子を接続し、接続ノードに第1端子を接続した第2振幅制限素子N32とを備える。

(もっと読む)

発振回路

【課題】 クロック発振回路のジッタが音質に重要だとは気が付かなかったか、CMOSの発振回路のジッタ性能で十分だと思われていた。しかし、ジッタが多いと、音質的に十分でないことが判明した。そこで、高音質化のため低ジッタ化し、なおかつ高周波化、低電圧化、波形のエッジの急峻さ、波形の対称性を達成する必要性がある。

【解決手段】 CMOSよりもノイズ特性に優れるバイポーラトランジスタを使い、これをコンプリメンタリ接続にすることで、低ジッタ、高周波化、低電圧化、波形のエッジの急峻さ、高い対象性を得ることができた。

(もっと読む)

発振回路

【課題】消費電流を小さくすることができる発振回路を提供する。

【解決手段】定電流が流れるPMOSトランジスタMP3と発振信号XTを増幅するNMOSトランジスタMN3との間に、PMOSトランジスタMP3を流れる定電流がNODE4(NODE3)に流れるのを遮断するためのPMOSトランジスタMP4を備えている。PMOSトランジスタMP4のソースはPMOSトランジスタMP3のドレインに接続され、ドレインはNMOSトランジスタMN3のソースに接続され、ゲートはNODE1に接続されている。また、NODE1は、バイアス信号線50に抵抗素子R2を介して接続されていると共に、信号線52に容量素子C1を介して接続されている。

(もっと読む)

半導体集積回路及び発振回路

【課題】振動子が外付けされて発振回路を実現する半導体集積回路において、振動子が外付けされるパッドと内部回路間の配線による浮遊容量の影響を小さくする。

【解決手段】半導体集積回路は、半導体基板と、第1のパッドP1に第1の抵抗及R1及び第1のコンデンサCACを介して接続の入力端子、及び、第2のパッドP2に第2の抵抗R2及び第3の抵抗RDを介して接続の出力端子を有するインバータ32と、インバータ入力端子と第2の抵抗R2及び第3の抵抗RDの接続点との間に接続され、インバータと共に発振ブロックを構成する帰還素子33と、第1の抵抗R1及び第1のコンデンサの接続点と基板電位との間に接続され、第1のパッドと発振ブロックとの間に配置された第2のコンデンサCGと、第2の抵抗R2及び第3の抵抗RDの接続点と基板電位との間に接続され、第2のパッドP2と発振ブロック間に配置された第3のコンデンサCDとを具備する。

(もっと読む)

半導体装置、及びその制御方法

【課題】発振回路と信号入出力回路とを切り替えて使用可能な半導体装置、及びその制御方法を提供することである。

【解決手段】本発明にかかる半導体装置は、発振素子1が接続可能な第1及び第2の外部接続端子2、3と、反転増幅器4と、反転増幅器の出力側と入力側との間に接続されたフィードバック抵抗5と、反転増幅器4の入力側に接続されたカップリング容量11に印加されるバイアスを安定化するバイアス安定化回路6と、第1の信号入出力部7と、第2の信号入出力部8と、を備える。半導体装置を発振回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を動作状態とし、第1及び第2の信号入出力部7、8を停止状態とする。信号入出力回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を停止状態とし、第1及び第2の信号入出力部7、8を動作状態とする。

(もっと読む)

改善特性を有する共振装置

【課題】実装が容易であり、且つ、公知のオシレータと比較して優れた性能を有する共振装置を提供する。

【解決手段】共振装置は、複数の同期化されたオシレータを備える。各オシレータは、共振器(1)を備える。共振器(1)は、共振器(1)の振動を表す検出信号を、共振器(1)の励振入力(E)に接続されるフィードバックループに供給する検出手段を備える。検出信号は、オシレータのフィードバックループの導電率を制御する。全ての共振器の励振入力は、共振装置の出力を構成する共通部に接続される。容量性負荷(5)は、共通部と基準電圧(GND)との間に接続される。

(もっと読む)

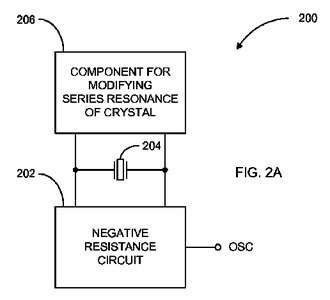

発振器の電力消費を低減させるためのシステムおよび方法

負性抵抗回路と、クリスタルと、発振信号を生成することにおいて、負性抵抗回路の電力消費を減らすために、クリスタルの直列共振を修正するように適合されるコンポーネントとを含む発振信号を生成するための装置。このコンポーネントは、正のリアクタンス回路、1つまたは複数の誘導性素子、またはクリスタルに結合された一対の誘導性素子を含む。この装置は、クリスタルに結合された可変キャパシタのような、発振信号の周波数を調整するための周波数同調コンポーネントを更に含む。負性抵抗回路は、デジタルインバータ回路、反転アナログ増幅器、または自己調整回路を含みうる。この装置は、負性抵抗回路に定常電流を供給するための静止電流ソースと、発振信号が、定義された定常状態に達するのを促進するために、スタートアップ中にのみ、負性抵抗回路にブースト電流を供給するためのスタートアップ電流ソースとを具備する。  (もっと読む)

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

温度補償電圧発生回路、温度補償型発振回路

【課題】温度補償電圧発生回路、及び温度補償型発振回路を提供する。

【解決手段】圧電振動子12と、前記圧電振動子12の発振周波数の温度補償を行う第1可変容量素子16と、前記発振周波数を所定の値に調整する第2可変容量素子18と、を有する発振回路12と、前記第2可変容量素子18に接続され、前記第2可変容量素子18の容量を制御するAFC回路54と、に接続される温度補償電圧発生回路29であって、前記温度補償電圧発生回路29は、前記第1可変容量素子16の一端に接続され、前記第1可変容量素子16の容量を制御する温度補償電圧を出力する第1温度補償電圧発生回路30と、入力側が、前記第1温度補償電圧発生回路30及び前記AFC回路54に接続され、出力側が前記第1可変容量素子16の一端の反対側の他端に接続され、入力された前記温度補償電圧と前記AFC回路54の出力とによって生成された補助温度補償電圧を前記第1可変容量素子30に出力する第2温度補償電圧発生回路44と、を有する。

(もっと読む)

21 - 40 / 171

[ Back to top ]