Fターム[5J079GA04]の内容

電気機械共振器を用いた発振回路 (23,106) | 発振のための増幅部の構成 (697) | MOS、CMOS (103)

Fターム[5J079GA04]の下位に属するFターム

MOS、CMOS2段以上 (23)

増幅素子自体の構成 (10)

Fターム[5J079GA04]に分類される特許

1 - 20 / 70

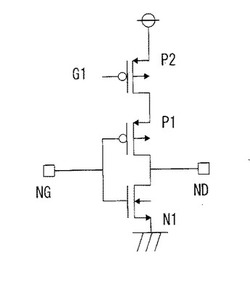

CMOSインバータ

【課題】 入力波形が急峻な場合でも反転電位を用いずに容易にデューティを補正することができるCMOSインバータを提供する。

【解決手段】 PMOSトランジスタP1と、NMOSトランジスタN1と、入力端子NGと、出力端子NDとを具備し、前記PMOSトランジスタ側もしくは前記NMOSトランジスタ側に接続されたスイッチを有している。前記スイッチがPMOSスイッチP2の場合には前記PMOSトランジスタ側に接続され、前記スイッチがNMOSスイッチの場合には前記NMOSトランジスタ側に接続される。入力端子NGに入力信号を入力した後に、前記スイッチに設けられた制御端子G1に制御信号を前記入力信号とずらして入力することによって前記入力信号の電圧を保持させ出力信号のデューティ補正を行う。

(もっと読む)

半導体装置、発振器、アンテナシステムおよび送受信システム

【課題】簡易に半導体基板上に形成でき、差動型で動作する半導体装置ならびにこれを用いた発振器、アンテナシステムおよび送受信システムを提供する。

【解決手段】半導体装置は、半導体基板と、複数の音響波伝播層と、分離層と、音響波反射層と、第1のコンタクトと、第2のコンタクトとを備える。前記複数の音響波伝播層は、前記半導体基板に、互いに離間して形成される。前記分離層は、前記半導体基板に形成され、前記複数の音響波伝播層を互いに電気的に分離するが、音響波は通過させる。前記音響波反射層は、前記半導体基板に形成され、前記複数の音響波伝播層内に前記音響波を閉じ込めるように形成される。前記第1のコンタクトは、前記複数の音響波伝播層の1つに形成され、第1の差動信号が入力または出力される。前記第2のコンタクトは、前記複数の音響波伝播層の他の1つに形成され、前記第1の差動信号とは位相が異なる第2の差動信号が入力または出力される。

(もっと読む)

音響半導体装置

【課題】大きなインダクタンスをもつインダクタ素子を実現する音響半導体装置を提供する。

【解決手段】実施形態によれば、素子部と、第1端子と、を備えた音響半導体装置が提供される。前記素子部は、半導体結晶を含み音響定在波が励起可能な音響共振部を含む。前記第1端子は、前記素子部と電気的に接続される。前記第1端子を介して、前記音響定在波と同期する電気的信号を前記音響共振部から出力する、及び、前記音響定在波と同期する電気的信号を前記音響共振部に入力する、の少なくもいずれかを実施可能である。

(もっと読む)

水晶発振回路

【課題】反転電圧VTH、負性抵抗−RL、発振周波数f0が電源VDDの影響を受けることがなく、定電圧回路を追加する必要がなく、しかも、動作電圧も低くなり、水晶振動子に流れる電流も小さくすることができる発振回路を提供する。

【解決手段】NMOSインバータIVnと、帰還抵抗Rfと、水晶振動子Qzと、が互いに並列接続され、NMOSインバータIVnの入力と電源VSSとの間にキャパシタCGが接続され、NMOSインバータIVnの出力と電源VSSとの間にキャパシタCDが接続された水晶発振回路1において、NMOSインバータIVnが、電源VDDに接続された定電流回路Inと、定電流回路Inと電源VSSとの間に接続されたn型のMOSトランジスタTnと、から構成されている。

(もっと読む)

水晶発振回路における負荷容量の決定方法、水晶発振回路における負性抵抗RLの決定方法、発振回路、及び電子機器

【課題】本発明の目的は、低い負荷容量有する水晶発振回路において、負荷容量、及び負性抵抗RLを決定する決定方法を提供するものである。

【解決手段】(CLn+1/CLn)2=α(nは1以上の整数、α=2-1/2)が成立するように、負荷容量CL1に対して負荷容量CLn(n≧2)を決定する。さらに、CMOSインバータの入力側と出力側の間に最小帰還抵抗Rfminと並列に配置されたリーク抵抗Rzを仮想して、最小合成帰還抵抗RFminを式RFmin=(Rfmin×Rz)/(Rz+Rfmin)を用いて決定し、最大負性抵抗RLmaxの値を、式(RLmax/RFmin)1/2 <α(αは安全係数で2-1/2)を用いて決定する。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

圧電発振器

【課題】 反射素子の反射特性を用いて高周波化、周波数安定化を図ることができる圧電発振器を提供する。

【解決手段】 電界効果型のトランジスタ1のゲートに共振回路3が接続され、ドレインに出力端子7が接続されると共に、電源電圧Vが印加され、ソースに反射素子として圧電共振器6が接続され、共振回路3の共振周波数と反射素子の圧電共振器6の発振周波数とを略同じにした圧電発振器であり、共振回路3とゲートとの間に第1のマッチング回路2と、ドレインと出力端子8との間に第2のマッチング回路7と、ソースと反射素子との間に第3のマッチング回路5を設けるようにしてもよいものである。

(もっと読む)

電子回路

【課題】発振回路部の信号反転素子及びインターフェース回路部のインターフェース回路部のインターフェース集積回路素子で消費される電流を抑えて消費電力が少ない電子回路を提供する。

【解決手段】発振回路部とインターフェース回路部と被駆動回路部と備えた電子回路であって、発振回路部用電源電圧印加端子と発振回路部の間に発振回路部用電流制限抵抗が設けられ、インターフェース回路部用電源電圧印加端子とインターフェース回路部との間にインターフェース回路部用電流制限抵抗が設けられ、発振回路部用電流制限抵抗の両端部からグランドに接続されている第一のコンデンサが設けられ、インターフェース回路部用電流制限抵抗の両端部からグランドに接続されている第二のコンデンサが設けられ、インターフェース回路部から出力され被駆動回路部に入力される信号電圧が被駆動回路部が動作するために必要な電圧より大きいことを特徴とする。

(もっと読む)

発振回路及び電子機器

【課題】本発明の目的は、実装基板に配置される水晶発振回路における浮遊容量Csを低減する手段を提供することである。

【解決手段】本発明は、発振回路を構成するCMOSインバータの入出力端子間に接続する水晶振動子と、前記CMOSインバータの入力端子パッドへ接続する前記水晶振動子側の入力端子を含む入力配線ラインと、前記CMOSインバータの出力端子パッドへ接続する前記水晶振動子側の出力端子を含む出力配線ラインと、前記水晶振動子側の接地電源端子を含む接地電源配線ラインと、前記入力配線ラインと前記接地電源配線ラインとの間、及び前記出力配線ラインと前記接地配線ラインとの間に接続された容量素子と、を有する発振回路において、前記入力配線ラインと前記出力配線ラインとの間の少なくとも一部に前記接地電源配線ラインが配置されていることを特徴とする。

(もっと読む)

水晶発振回路の負荷容量の決定方法およびそれを用いた電子機器

【課題】本発明の目的は、水晶振動子を用いた発振回路の発振起動時間と負荷容量CL値の関係を明確にし、所望の発振起動時間から負荷容量CL値を決定することである。

【解決手段】本発明は、水晶振動子を用いた発振回路において、発振起動時間Tsと発振余裕度Mの関係式又は関係グラフを用いて発振余裕度Mから発振起動時間Ts(Ts0)を求める手段(A)と、発振起動時間Tsと負荷容量CLの関係式、及び駆動電流値Iosから、任意の駆動電流値Iosにおける発振起動時間Tsと負荷容量CLの関係式を求める手段(B)と、前記手段(B)において求められた発振起動時間Tsおよび負荷容量CLの関係式を用いて、前記手段(A)で求められた発振起動時間Ts0に対応する負荷容量CLを決定する手段(C)と、を含むことを特徴とする。

(もっと読む)

発振回路

【課題】周波数の校正を簡単に且つ高精度に可能な発振回路の提供。

【解決手段】圧電振動子4の両端に接続された入力端子と出力端子を有する第1のインバータ回路1と,第1のインバータ回路の入出力端子間に設けられた第1のフィードバック抵抗3と,第1のインバータ回路の入出力端子に各々接続され,制御信号により容量値が可変設定可能な第1、第2の可変容量素子2a、2bと,所定基準電流を入力端子又は出力端子に供給して第1または第2の可変容量素子を充電する充電回路10と,入力端子又は出力端子の充電電圧と,参照電圧VRとを比較する比較器11と,キャリブレーション時に,第1の時間で,充電回路に入力端子又は出力端子への基準電流の供給を開始させ,第1の時間後の第2の時間での比較器の比較結果に応じて,充電電圧が参照電圧に近づく様に,第1又は第2の可変容量素子の容量値を設定する制御信号生成の制御回路12とを有する発振回路。

(もっと読む)

圧電振動回路

【課題】

インバーターを用いて大きな負性抵抗を得、さらに広い発振周波数可変幅を得る圧電発振回路を提供する。及び、大きな負性抵抗を得ることができることを論理的に証明する。

【解決手段】

圧電振動回路として、インバーターの入出力間にコンデンサーと圧電振動子を並列接続した回路と、第1のコイル、第2のコイルを直列接続した回路を備え、第1のコイル、第2のコイルの接続点と回路の接地点間にパスコンデンサーを備え、接続点と接地点間を交流に対して短絡させ、さらに電源と接地間にはコンデンサーを挿入し、交流に対して短絡させ、前記インバーターの電源端子と接地端子間に電圧を印加し、発振回路として構成した。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

集積回路装置及び電子機器

【課題】発振回路の性能を維持しながら静電気保護耐圧を向上できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、振動子XTALの一端に接続される第1のパッドP1と、振動子XTALの他端に接続される第2のパッドP2と、振動子XTALの発振用のバッファー回路BFと、第1のパッドP1側の第1の接続ノードNC1と、バッファー回路BFの入力ノードNIとの間に設けられる第1の保護抵抗素子R1と、第2のパッドP2側の第2の接続ノードNC2と、バッファー回路BFの出力ノードNQとの間に設けられる第2の保護抵抗素子R2と、第1、第2の接続ノードNC1、NC2の一方に接続される容量回路CX1(CX2)とを含む。

(もっと読む)

低消費電力回路

【課題】起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】第1発振トランジスタP31、第1発振トランジスタP31のドレイン端子にドレイン端子を接続した第2発振トランジスタN31、第1容量C2、第1容量C2に一方を接続し、他方を第1発振トランジスタP31と第2発振トランジスタN31の接続ノードに接続した圧電振動子Q1、一方を圧電振動子Q1に接続し、他方を第1発振トランジスタP31のゲート端子に接続した帰還抵抗回路Z3、第1発振トランジスタP31のゲート端子VP1に第1端子を接続し、接続ノードに第2端子を接続した第1振幅制限素子P32、第2発振トランジスタN31のゲート端子VN1に第2端子を接続し、接続ノードに第1端子を接続した第2振幅制限素子N32とを備える。

(もっと読む)

D/A変換回路及び圧電発振器

【課題】安定性と高速動作を維持し、デジタル入力信号のビット数が多くなっても比較的小さい面積で集積化可能なD/A変換回路及び圧電発振器を提供すること。

【解決手段】D/A変換回路1Aは、n個のクランプ電圧生成手段(クランプ回路12a〜12h)と、n個のクランプ電圧生成手段が生成するnビットのデジタル信号の電圧を加算する電圧加算手段(加算器20)と、を含む。n個のクランプ電圧生成手段の各々は、デジタル入力信号2の対応するビットの電圧に応じて、ハイレベル又はローレベルを出力するCMOSインバーター(PMOS15aとNMOS17aによるインバーター等)と、電源電位とグランド電位をそれぞれクリップして第1の電位と第2の電位を生成し、第1の電位と第2の電位をCMOSインバーターの出力のハイレベル及びローレベルとして供給する電圧クリップ手段(PMOS14a、NMOS18a等)と、を備える。

(もっと読む)

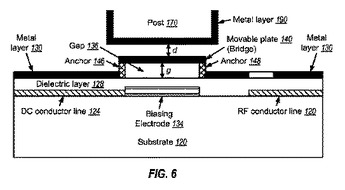

キャビティ内の調整可能なMEMS共振器

調節可能な共振周波数を有し、大きな信号を扱うことができる調整可能なMEMS共振器が説明される。1つの例示的設計では、調整可能なMEMS共振器は、(i)キャビティおよび支柱を有する第1の部分と、(ii)支柱の下に配置された可動プレートを含み、第1の部分と対になった第2の部分とを含む。各部分は、もう一方の部分と対向する表面上を金属層で覆われていてもよい。MEMS共振器の共振周波数を変化させるために、可動プレートを、直流電圧で機械的に動かすことができる。キャビティは、長方形または円形の形状を有してもよく、空であっても、誘電材料で満たされていてもよい。支柱は、キャビティの中央に位置してもよい。可動プレートは、第2の部分に、(i)1つのアンカーによって取り付けられて片持ち梁として働いてもよく、あるいは、(ii)2つのアンカーによって取り付けられてブリッジとして働いてもよい。  (もっと読む)

(もっと読む)

改善特性を有する共振装置

【課題】実装が容易であり、且つ、公知のオシレータと比較して優れた性能を有する共振装置を提供する。

【解決手段】共振装置は、複数の同期化されたオシレータを備える。各オシレータは、共振器(1)を備える。共振器(1)は、共振器(1)の振動を表す検出信号を、共振器(1)の励振入力(E)に接続されるフィードバックループに供給する検出手段を備える。検出信号は、オシレータのフィードバックループの導電率を制御する。全ての共振器の励振入力は、共振装置の出力を構成する共通部に接続される。容量性負荷(5)は、共通部と基準電圧(GND)との間に接続される。

(もっと読む)

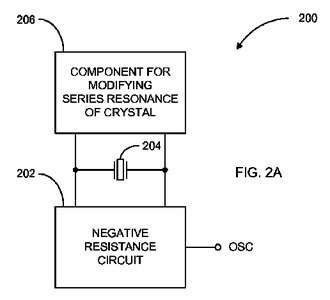

発振器の電力消費を低減させるためのシステムおよび方法

負性抵抗回路と、クリスタルと、発振信号を生成することにおいて、負性抵抗回路の電力消費を減らすために、クリスタルの直列共振を修正するように適合されるコンポーネントとを含む発振信号を生成するための装置。このコンポーネントは、正のリアクタンス回路、1つまたは複数の誘導性素子、またはクリスタルに結合された一対の誘導性素子を含む。この装置は、クリスタルに結合された可変キャパシタのような、発振信号の周波数を調整するための周波数同調コンポーネントを更に含む。負性抵抗回路は、デジタルインバータ回路、反転アナログ増幅器、または自己調整回路を含みうる。この装置は、負性抵抗回路に定常電流を供給するための静止電流ソースと、発振信号が、定義された定常状態に達するのを促進するために、スタートアップ中にのみ、負性抵抗回路にブースト電流を供給するためのスタートアップ電流ソースとを具備する。  (もっと読む)

(もっと読む)

圧電発振器

【課題】圧電発振器にスリープモードを備える。

【解決手段】圧電振動子100を発振させた発振信号Vpを出力する発振回路110と、発振回路110に電流Idを供給する電流源回路120と、発振回路110から出力された発振信号Vpを整形した出力信号OUTを出力するバッファ回路130と、スリープモードとノーマルモードとを切り替える制御信号SLを入力する制御端子140と、を含み、電流源回路120は、制御信号SLがスリープモードの時はノーマルモードの時に比べて発振回路110に供給する電流Idが少なくなるように切り替える第1の切替部124を含み、バッファ回路130は、制御信号SLがスリープモードの時はバッファ回路130を構成する素子への電流の供給を止める第2の切替部132と、制御信号SLがスリープモードの時は発振信号Vpが出力されないように切り替える第3の切替部133と、を含む圧電発振器1。

(もっと読む)

1 - 20 / 70

[ Back to top ]