Fターム[5J081CC42]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 小型・軽量・簡易化 (291)

Fターム[5J081CC42]の下位に属するFターム

IC化(共振器のチップ化等を含む) (118)

省電力化 (66)

他機能と兼用化

Fターム[5J081CC42]に分類される特許

1 - 20 / 107

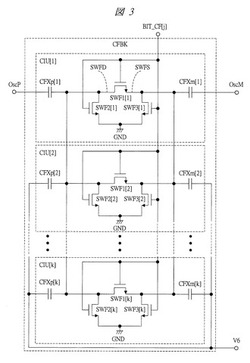

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

注入同期発振器

【課題】回路規模を小型化する注入同期発振器を得る。

【解決手段】発振周波数foの注入同期信号を発生する基準発振器1と、注入同期信号を検波し、注入同期信号の高周波電力に応じた直流電圧を発生すると共に発振周波数foの高調波を発生する検波回路2とを備え、検波回路2は、注入同期信号の高周波電力に応じた直流電圧および発振周波数foの高調波を、発振器3を構成するFET8のドレインに供給するので、FET8に注入同期信号を注入する回路と、FET8に直流バイアスを印加するバイアス回路とを検波回路2で共用することができ、注入同期発振器の回路規模を小型化することができる。

また、発振周波数foの高調波をFET8のドレインに供給するので、注入同期発振器として同期を容易にすることができる。

(もっと読む)

高周波発振器

【課題】安定発振、コンパクトなパッケージを実現したSHF帯に好適な高周波発振器を提供する。

【解決手段】低誘電率、低損失の基板材料として水晶板等の耐熱材を最小限の厚さとした基板を主基板2とし、一次実装する能動素子7とIDT3やデスクリート部品8などを主基板2の表裏にそれぞれ配置し、貫通電極6で両面側の間を接続することで配線長を最短とした。LTCCなどの従来の本体基板に代えて薄い水晶等を要部構成部品を実装する主基板とすることにより、薄型化と小型化を実現した。外力・応力に対する脆弱性を、主面側の保護カバーに加えて裏面にも補強カバーを設け、あるいはモールド構造とすることで補強した。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

帰還型発振装置

【課題】設計および製造が容易で、装置のサイズが小さい帰還型発振装置を提供すること。

【解決手段】帰還型発振装置1において、入力端子から入力された信号を増幅して出力端子から出力するバイポーラトランジスタ10と、マイクロストリップラインによって構成され、バイポーラトランジスタの出力端子と入力端子とを結合して出力端子から入力端子に所定の周波数の信号を帰還してバイポーラトランジスタを発振させる結合回路15と、を有する。

(もっと読む)

磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法

【課題】小型化及び低消費電力化を図ることができる磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法を提供する。

【解決手段】磁気同調デバイス駆動回路10は、固定電圧を出力する電源に接続され、印加された出力電圧制御信号に応じた電圧を出力するスイッチング電源回路11と、スイッチング電源回路11の出力電圧を所望の同調周波数に応じた電流に変換して同調コイル51に供給する定電流回路12と、同調コイル51の電圧の絶対値を所定値だけ大きくするシフト電圧を供給するシフト電圧供給部13と、電流が供給された同調コイル51の電圧とシフト電圧とを加算し、加算後の電圧を出力電圧制御信号としてスイッチング電源回路11に出力する加算回路14と、を備える。

(もっと読む)

高周波発振器

【課題】小型に構成され、高調波と基本波との電力比を増加可能な高周波発振器を得る。

【解決手段】印加された電源電圧に基づいて、発振周波数の基本波で発振動作を行い、発振周波数の2倍波を出力する2倍波取り出し型発振器10と、2倍波取り出し型発振器10の出力端子に接続され、発振周波数の2倍波を通過帯域とする出力回路20とを備え、出力回路20は、2倍波取り出し型発振器10に電源電圧を供給する電源端子21と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する結合線路22と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する伝送線路23と、結合線路22の結合量に応じた出力電力を得る第1負荷抵抗24と、電源端子21に対して並列に接続されたキャパシタ25とを有する。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

静磁波発振装置

【課題】外部磁界からの影響を防止しつつ、小型化及び軽量化を図ると共に、耐振動及び耐衝撃性を向上させた静磁波発振装置を提供する。

【解決手段】静磁波素子を用いて所望の発振周波数を得る静磁波発振装置1であって、静磁波発振装置本体2の周囲に強磁性体33a,33bと振動を吸収可能な非磁性体32a,32b,32cとを交互に積層させると共に、該非磁性体32a,32b,32cが吸収可能な振動周波数を層によって相違させる。

(もっと読む)

広帯域発振回路

【課題】LC型VCOの出力する発振信号の周波数帯域が比較的狭くても、連続した周波数の発振信号(分周信号)の出力が可能な広帯域発振回路の実現。

【解決手段】発振信号を出力する発振器11と、発振器の出力する発振信号を受け、フィルタリングして注入同期信号NINJを出力するフィルタ14と、自己発振動作を行い、注入同期信号により発振動作が規制されて発振信号の分周信号を出力し、制御信号VbDに応じて分周比が変化する注入同期型周波数分周器12と、を備え、フィルタ14は、分周信号に同期したフィルタ制御信号に応じて、発振信号を通過させる通過特性を時間的に制御して注入同期信号NINJを発生する。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

周波数可変共振器

【課題】小型でしかもQ値を向上させることが可能な周波数可変共振器を提供すること。

【解決手段】本発明一例の周波数可変共振器は、交流電源に一端を接続された第1のインダクタと、前記交流電源の他端にカソード端子を接続され、所定の直流電圧を印加される可変容量ダイオードと、この可変容量ダイオードのアノード端子に一端を接続され、他端を前記第1のインダクタの他端に接続され前記可変容量ダイオードに印加される逆バイアス電圧をカットする第1のコンデンサとからなる直列共振回路と、並列接続された第2のインダクタ及び第2のコンデンサからなり、前記第1のインダクタと第1のコンデンサとの接続点に一端を接続され、他端を前記可変容量ダイオードのカソード端子に接続され、前記直列共振回路の共振周波数とほぼ同じ共振周波数を有する並列共振回路と、を有する。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

マイクロ波発振回路およびその実装方法

【課題】 スルーホールを削減してプリント基板の製造コストアップを防ぎ、基板の線膨張率の違いによる発振周波数ずれを防ぎ、基板に窓を空ける必要がなく、発振周波数範囲が狭くなるのを防ぎ、かつ中心周波数の調整が可能なマイクロ波発振回路の提供。

【解決手段】 マイクロ波発振回路100は、上部基板1と、その表面に設けられる第1表層パターン2と、第1表層パターン上に設けられ第1表層パターンと電気的接続される可変容量素子3と、上部基板の表面の第1表層パターンとは異なる位置に設けられる第2表層パターン4と、第2表層パターン上に設けられ第2表層パターンと電気的接続される発振素子5と、上部基板の裏面に設けられる第1および第2裏面パターン6,7と、下部基板8と、下部基板の表面に設けられる第3表層パターン9と、下部基板の裏面に設けられる第3裏面パターン10とを含む。

(もっと読む)

プリントインダクタおよびその製造方法ならびに電圧制御発振器

【課題】プリントインダクタのQ値を高く設定してもその形成面積を小さくすることができるなどの新規のプリントインダクタおよびその製造方法ならびに電圧制御発振器を提供する。

【解決手段】本実施形態のプリントインダクタ1は、第1のインダクタパターン10、第2のインダクタパターン20および接続部材30(例えば、第3のインダクタパターン30A)を備えている。第2のインダクタパターン20(または第1のインダクタパターン10)における遠方部分20a(または10a)の幅寸法は、その近接部分20b(または10b)の幅寸法よりも小さくなるように形成されている。

(もっと読む)

共振器型発振器、及び同調コンデンサ回路

【課題】共振器型発振器のQ値などの特性を高く維持させた設計をより容易に行えるようにする技術を提供する。

【解決手段】静電容量Caの2n倍(nは0〜5までの整数)となっている計6個)のコンデンサ211a〜fが並列に接続され、それらコンデンサ211a〜fにはスイッチ212a〜fがそれぞれ直列に接続されている。コンデンサ211a〜fは、静電容量が大きいものほど、インダクタと接続させる配線402の長さが短い位置に配置されている。それにより、出力する信号の周波数が低くなるほど、配線402の抵抗がQ値に及ぼす影響を低減させる。

(もっと読む)

電圧制御発振器

【課題】電源電圧に重畳されたノイズにより発生する発振器の位相雑音を低減することができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ることのできる電圧制御発振器を提供すること。

【解決手段】この電圧制御発振器1は、直流電源端子16にコレクタが接続された発振用トランジスタ11と、発振用トランジスタ11のエミッタ・接地間に接続された第1の抵抗21と、発振用トランジスタ11のベース・接地間に接続された共振回路27と、発振用トランジスタ11のエミッタと第1の抵抗21との接続点と直流電源端子16とを接続する結合ラインL1上に設けられた第1のキャパシタ22とを具備することを特徴とする。

(もっと読む)

VCO周波数チューニングのための、オーバーラップする2セグメントキャパシタバンク

【解決手段】(例えばFM受信機中の)VCOは、LC共振タンクを含む。LC共振タンクは、粗同調キャパシタバンクおよび微同調キャパシタバンクを含む。粗同調キャパシタバンクは複数のデジタル制御粗同調キャパシタエレメントを含み、アクティブな際に各々は第1キャパシタンス値を供給する。微同調キャパシタバンクは複数のデジタル制御微同調キャパシタエレメントを含み、アクティブな際に各々は第2キャパシタンス値を供給する。キャパシタミスマッチの現実的な問題に対処するため、VCOチューニング範囲の全体にわたるキャパシタンスオーバーラップが、微キャパシタバンクのデジタル制御微同調キャパシタエレメントの全てがアクティブな場合に、微キャパシタバンクのキャパシタンス値が第1キャパシタンス値より大きくなるように第1及び第2キャパシタンス値を選択することによって生成される。 (もっと読む)

1 - 20 / 107

[ Back to top ]