Fターム[5J081CC43]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 小型・軽量・簡易化 (291) | IC化(共振器のチップ化等を含む) (118)

Fターム[5J081CC43]に分類される特許

1 - 20 / 118

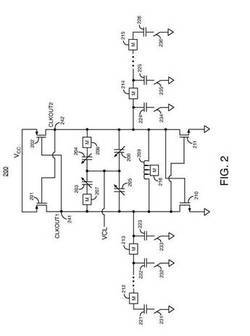

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】インダクタンス素子に起因して発生する起動時の異常発振を効率的に抑えることが可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(SAW共振子10)と、増幅回路20と、スイッチング素子(NMOSスイッチ30)と、を含む。増幅回路20は、共振子の一端から他端への帰還経路、当該帰還経路に設けられている第1のインダクタンス素子(伸長コイル200)、当該帰還経路に設けられ、第1のインダクタンス素子と直列に設けられている可変容量素子(可変容量ダイオード202)、を有している。スイッチング素子は、第1のインダクタンス素子と可変容量素子とを含む回路部に対して並列に設けられている。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

温度特性調整データ生成方法

【課題】n(nは1以上の整数)次の関数で表現される温度特性を持った信号のn−1次の温度係数を調整する際に、n次の温度係数の影響を軽減し、且つコストの増大を抑えることができる、温度特性の調整データを生成する方法を提供する。

【解決手段】温度特性調整データ生成方法は、n(nは1以上の整数)次の関数で表現される温度特性を持った信号を生成する回路を有する半導体装置の温度特性を調整するデータ(803)を、プログラム処理装置(6、10)を用いて生成する方法であって、n+1よりも少ない数の温度における前記信号の値を、前記信号に関する目標値に所定の補正値を加えた値(601)に近づけるように温度特性を調整するデータを生成するデータ生成処理を含む。

(もっと読む)

半導体集積回路装置および発振周波数較正方法

【課題】発振器の発振周波数の較正作業を短縮することができる半導体集積回路装置および発振周波数較正方法を提供する。

【解決手段】DCO50と、温度に対して単調な特性を持って変化する電圧源20から得られる電位に応じたDCO50に設定すべき発振周波数の温度係数および発振周波数の絶対値を記憶する記憶部42と、を備えたことを特徴とする半導体集積回路装置。

(もっと読む)

半導体装置

【課題】同相信号除去比を高めた発振信号を得ることができる半導体装置を提供する。

【解決手段】半導体基板と、前記半導体基板上に第1の絶縁膜を介して設けられた第1の電極4と、前記第1の電極上に第2の絶縁膜を介して設けられ前記第1の電極との間に第1のキャパシタを形成する第2の電極6と、前記第1の電極上に前記第2の絶縁膜を介して設けられ前記第1の電極との間に第2のキャパシタを形成する第3の電極7と、前記半導体基板に設けられ、前記第2の電極と前記第3の電極との間に接続されたインダクタ19と、前記半導体基板に設けられ、前記第2の電極と前記第3の電極との間に接続された増幅回路20と、を備えたことを特徴とする半導体装置。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

発振回路及び半導体装置

【課題】周波数可変範囲の広い発振回路及び発振回路を備えた半導体装置を提供する。

【解決手段】第1の端子と第2の端子との間に接続されたインダクタンス素子と、インダクタンス素子と並列に第1の端子と第2の端子との間に接続された増幅回路と、第1の端子及び第2の端子に接続された第1の容量素子と、を備えた共振型発振回路であって、インダクタンス素子の配線の途中に2箇所以上の引き出し部を設け、2箇所以上設けた引き出し部の間にオンしたときに当該引き出し部間を短絡するスイッチ素子と第2の容量素子とが並列に接続されている。

(もっと読む)

半導体チップ、筺体内信号伝送方法及び筺体内信号伝送システム

【課題】同一の筺体内に配置された半導体チップ間でミリ波の信号伝送媒体を介したミリ波帯域の信号を伝送できるようにすると共に、当該半導体チップ間でより簡易に高速伝送システムを実現できるようにする。

【解決手段】入力信号SINが基準搬送信号Sfに基づいてミリ波の送信信号Soutに変換され、変換後の送信信号Soutが、筺体1内に配置されたCMOSチップ101の送信部から当該筺体1内のミリ波の信号伝送媒体51へ伝送される場合であって、局部発振信号Sf’を発振する発振回路を有して筺体1内に配置され、信号伝送媒体51から受信したミリ波の受信信号Sinを発振回路に注入して当該局部発振信号Sf’を基準搬送信号Sfに同期させ、同期後の局部発振信号Sf’に基づいてミリ波の復調信号SOUTを復元するものである。

(もっと読む)

1 - 20 / 118

[ Back to top ]