Fターム[5J081KK09]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 一次要因 (534) | 容量 (335) | 素子内容量 (235) | バラクタダイオード (198)

Fターム[5J081KK09]に分類される特許

81 - 100 / 198

トランスのカップリングを利用した差動電圧制御発振器及び直交電圧制御発振器

本発明による差動及び直交電圧制御発振器は、電流の再使用構造によって低電力駆動が可能であり、トランスを用いたカップリングにより優れた位相雑音特性を有する。また、周波数可変のための可変キャパシタンス部が粗同調用と微細同調用とに分けられるので、これによって電圧発振利得を低減しつつ広帯域同調範囲を得ることができる。また、抵抗を用いた制御電圧の分配によって各可変キャパシタンス部が全体キャパシタンス領域で線形的に動作するように構成されているので、これによって線形的な制御電圧−発振周波数特性を得ることができる。また、本発明による直交電圧制御発振器は、スイッチングトランジスタによる電流消耗と基板損失なしに、優れた位相雑音特性を有しながら4位相の直交信号を出力することができる。  (もっと読む)

(もっと読む)

PLL回路

【課題】複数のVCOを切り替えて使用するPLL回路において、VCOの位相雑音を最適化することである。

【解決手段】PLL回路11の複数のVCO12−1〜12−nの内の1つの選択は、VCO選択データにより行われ、キャパシタの選択はVSBデータにより行われる。バイアス電流設定回路25は、VCO選択データとVSBデータと制御電圧のデジタル変換値VTDをデコードして、予め定めたバイアス設定値を可変電流源I1に出力する。

(もっと読む)

電圧制御発振回路

【課題】発振信号の周波数帯域を広くさせつつ、位相雑音を低減することが可能な電圧制御発振回路を提供することを目的とする。

【解決手段】電圧制御発振器7〜10と、選択信号Vout_SELに対応する発振信号を選択するセレクタ11と、セレクタ11により選択された発振信号の振幅値Vout_Levを検出する検出回路12と、スイッチ13、14と、スイッチ13を介して入力される電圧Vtuneに対応するデジタル値Daを出力するとともに、スイッチ14を介して入力される振幅値Vout_Levに対応するデジタル値Dbを出力するADC回路15と、選択信号Vout_SEL及び選択信号Vout_CAPをデジタル値Daに基づいて出力するとともに、電圧制御発振器に流れる電流値をデジタル値Dbに基づいて制御する制御回路16とを備えて電圧制御発振回路2を構成する。

(もっと読む)

電流源回路

【課題】プロセスによる抵抗のバラツキの影響を受けにくい電流源回路を提供する。

【解決手段】上記課題を解決するために、電流源回路100に、MOSトランジスタQ6とQ7のドレイン電圧を入力としそれらの比較の結果を制御部104に出力するコンパレータ103と、コンパレータ103の出力に応じたデジタル制御信号を可変抵抗R1およびR2に出力して両抵抗値を変更する制御部104と、を有する抵抗値制御回路101を備える。

(もっと読む)

温度補償型圧電発振器

【課題】圧電振動素子を搭載した温度補償型圧電発振器の小型化が進んでも、消費電力が少なく、短時間で立ち上がり、温度補償型圧電発振器の表面に新たに外部接続用電極端子を設けることがない温度補償型圧電発振器を提供することを課題とする。

【解決手段】第1のスイッチは、機能端子から入力された信号により電源電圧端子と増幅回路部の第2のインバータとの間を接続または切断し、第2のスイッチは、切替信号制御回路部からの切替信号により、第1のスイッチ又は可変容量ダイオードのカソードと、機能端子との接続を切り替え、第3のスイッチは、チップセレクト回路部からの切替信号により、メモリ部又は、第2のスイッチと、機能端子との接続を切り替える。

(もっと読む)

発振回路及びテレビジョン信号受信用チューナ

【課題】特別の部品を追加することなく、平衡型の発振回路のC/N特性を改善すること。

【解決手段】VHFローバンド及びVHFハイバンドのテレビジョン信号を受信するための局部発振器を不平衡型の発振回路11,12で構成し、UHFのテレビジョン信号を受信するための局部発振器を平衡型の発振回路13で構成し、VHFバンド用発振回路11,12のC/N特性改善のために設けている抵抗R2の接続点を、UHF用発振回路13に接続した共振回路23のインダクタンス素子23aの一端に接続し、平衡型のUHF用発振回路13に対してラインフィルタ31,32を両側に配置する。

(もっと読む)

発振器

【課題】発振器において、発振周波数可変範囲を狭めることなく位相雑音を低減する。

【解決手段】バイポーラトランジスタTr1のコレクタとベース間にバイアス回路を備える発振器において、電源Vccとコレクタとの間に発振周波数よりも低いベースバンド周波数帯域において十分に高いインピーダンスを示す素子や回路、例えばベースバンドチョークコイル16を接続する。ベースバンド周波数帯域のノイズ信号はチョークコイル16により電源側に漏れることなくバイアス回路を介して負帰還される。チョークコイル16の代わりにカレントミラー回路を設けてもよい。

(もっと読む)

電圧制御発振器

【課題】同調範囲と位相雑音とは、線路共振器への能動回路と同調回路の接続位置に関する値δで関連づけられており、それぞれの特性がトレードオフの関係にあり、設定の自由度が小さい。そこで、同調範囲と位相雑音の設定の自由度を高めた電圧制御発振器を得ることを目的とする。

【解決手段】線路長が基本波周波数において1/2波長となる両端開放線路からなる線路共振器と、反射利得を有する能動回路と、制御電圧によってリアクタンス値が可変である同調回路と、を備え、前記能動回路を前記両端開放線路の前記基本波周波数におけるショート位置から所定の位相雑音に基づいて選定された波長分θ1隔てた位置で前記両端開放線路に接続し、前記同調回路を前記両端開放線路の前記基本波周波数におけるショート位置から所定の周波数同調範囲に基づいて選定された波長分θ2隔てた位置で前記両端開放線路に接続した。

(もっと読む)

半導体集積回路及び電圧制御発振器

【課題】待機状態から任意の容量安定状態への過渡時間の短いMOSバラクタを提供する。

【解決手段】Nウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以上にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。また、Pウェルを有するMOSバラクタ素子の動作待機時に電極の電位からウェル領域の電位を引いた電位差を0以下にする制御回路を備えることにより、動作待機時から任意の容量安定状態への過渡時間を短くすることが可能となる。

(もっと読む)

発振回路

【課題】発振回路の発振周波数の制御が簡単な構成でできるようにする。

【解決手段】所定長の第1及び第2の分布定数線路11,12をほぼ平行に配置し、その第1及び第2の分布定数線路11,12の一端に所定の直流電圧VDDもしくは直流電流を供給する。第1の分布定数線路11の途中と、第2の分布定数線路12の途中との間に、1つ又は複数の容量素子C11,C12,・・・を接続する。第1及び第2の分布定数線路11,12の他端と、接地電位部との間には、スイッチング手段Q11,Q12を相互に接続した発振回路を構成させる。そして、第1,第2の分布定数線路11,12中の容量素子C11,C12,・・・の接続位置の設定で、発振周波数を制御できるようにする。

(もっと読む)

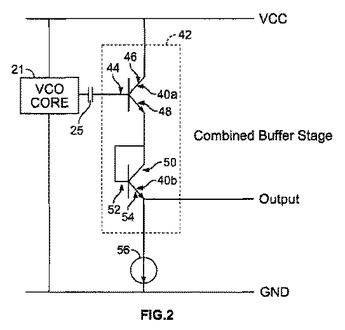

カスケード接続されたエミッタフォロワバッファ段を有する電圧制御発振器

電圧制御発振器(VCO)は出力バッファを有し、これは、第1のトランジスタを含む第1のバッファ段と、第2のトランジスタを含む第2のバッファ段とを備えている。第1および第2のトランジスタはカスケード接続されたエミッタフォロワバッファ回路として配置されている。  (もっと読む)

(もっと読む)

発振装置及びアレイアンテナ装置

【課題】分配器を用いることなく、位相同期した多数の発振信号を供給すること。

【解決手段】複数の発振周波数を同期させた発振器において、複数の発振器と、これらの複数の発振器のゲート/ベースを、全周長が発振周波数の1波長のマイクロストリップ線路から成る閉線路の各ポートに接続した線路で結合したリング共振器と、リング共振器の線路に挿入された励振位相を一方向に固定する励振方向固定装置とから成る発振装置である。閉線路間に配設される共通の発振器は、差動発振器で構成されている。

(もっと読む)

誘電体発振器及び誘電体発振器の制御方法

【課題】発振周波数を所定の範囲で変化させた場合において、負性抵抗回路と誘電体共振器との間の位相ずれを順次補正することにより、低い位相雑音特性とする誘電体発振器とその制御方法を提供する。

【解決手段】誘電体発振器100は、誘電体共振器10と位置検出器21と周波数変換器22と補正値変換器23と負性抵抗回路30とを含み、誘電体共振器10は、誘電体14と調整ねじ11と該ねじのひさし部13の位置を検知する位置検出センサ18と、を有している。位置検出器21は位置検出センサ18からの信号に基づいて、位置情報を周波数変換器22に送る。周波数変換器22は、位置情報と共振周波数との対応情報から共振周波数を補正値変換器23へ送る。補正値変換器23は共振周波数の帯域と帰還容量との対応情報に基づいて帰還容量を設定することで、位相ずれを補正する。

(もっと読む)

改良ハートレー電圧制御発振器

2つのインダクタ(Ld、Lg)と、トランジスタ(Q1)と、バラクタ(C)とを備えるハートレー電圧制御発振器(VCO)回路において、2つのインダクタ(Ld、Lg)は結合インダクタ対として配列され、その間に正の相互インダクタンス(M)を可能にし、VCOのサイズを小さくする。 (もっと読む)

電圧制御発振器

【課題】広い周波数範囲で安定して動作する電圧制御発振器を提供する。

【解決手段】電圧制御発振器11の差動増幅器12の出力を入力側に帰還する帰還キャパシタC1と、帰還キャパシタC1と差動増幅器12の入力端子の接続点に一端が接続され、他端が接地された可変容量素子VCを有する。電圧制御発振器11の発振周波数が変更されると、制御部13は、可変容量素子VCに印加する電圧を制御してその容量値を変化させ、電圧制御発振器11のオープンループゲインがほぼ一定になるようにする。

(もっと読む)

デジタル制御発振回路、周波数シンセサイザ、それを用いた無線通信機器及びその制御方法

【課題】周波数が直線的に変化する範囲が広く且つ占有面積が小さいデジタル発振回路を実現できるようにする。

【解決手段】デジタル制御発振回路10は、複数の第1の可変容量素子からなる第1の容量素子群14及び複数の第2の可変容量素子からなる第2の容量素子群14を含む可変容量部12を有し、可変容量部12の容量値に対応した発振周波数の信号を生成する発振部を備えている。第1の可変容量素子の第1の容量変化量は、第2の可変容量素子の第2の容量変化量に2以上の整数値を乗じた値であり、第2の可変容量素子の個数は、2以上の整数値から1を減じた値以上である

(もっと読む)

電圧制御発振器および発振制御システム

【課題】例えば、さまざまな無線規格に対応するように、利得を変化させることが可能な電圧制御発振器を提供する。

【解決手段】本発明に係る電圧制御発振器1は、第1の電位に一端が接続された第1のMOSトランジスタと、第1の電位に一端が接続され、ゲートが第1のMOSトランジスタの他端に接続され、他端が第1のMOSトランジスタのゲートに接続された第2のMOSトランジスタと、第1の制御電圧に応じてその容量が変化する第1のバラクタと、一端が第1のバラクタの一端に接続された第1のインダクタと、一端が第1のバラクタの他端に接続された第2のインダクタと、第2の制御電圧に応じてその容量が変化する第2のバラクタと、第2のバラクタの一端と第2の電位との間に接続された第3のインダクタと、第2のバラクタの他端と第2の電位との間に接続された第4のインダクタと、を備える。

(もっと読む)

発振周波数制御方法及び発振器

【課題】温度によって変化する発振周波数を、応答性良く、正確に、所定の周波数に調整することができる発振周波数の制御方法及び発振器を提供する。

【解決手段】本発明の発振周波数制御方法は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器の発振周波数制御方法であって、振幅を測定する工程と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する工程を備える。また、本発明の発振器は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器であって、振幅を測定する振幅測定部と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する温度補償部を備える。

(もっと読む)

インダクタ、配線基板、および半導体装置

【課題】 高周波帯域においても寄生抵抗が低く、入出力端子からインダクタを見たときの特性が対称的であり、小型なオンチップ型のインダクタを提供する。

【解決手段】 絶縁層を介した複数の層に亘って入力端子IN1、IN2から出力端子OUT1、OUT2まで螺旋状にそれぞれ延びた偶数個のインダクタ素子L1、L2を有している。インダクタ素子L1、L2は、相互の発生磁界が同じ向きとなるように配置されていると共に、入力端子から見たQ値を含むインダクタ特性と出力端子から見たものとが概ね同じになるように並列接続されている。

(もっと読む)

半導体集積回路装置

【課題】定常電流の変化に起因するVCOの位相雑音を低減し、VCO出力を安定させる。

【解決手段】半導体集積回路装置300は、バイアス電流又は発振周波数を制御して出力信号を出力する電圧制御発振器301と、前記電圧制御発振器301によって出力された出力信号に基づいて周波数制御信号を出力する位相同期回路302と、前記位相同期回路302から出力された周波数制御信号のピーク位置を検出するピーク位置検出回路303と、前記ピーク位置検出回路303によって検出されたピーク位置に基づいてバイアス電流を生成し、前記バイアス電流を出力するバイアス制御回路304と、を備え、前記電圧制御発振器301は、前記位相同期回路302によって出力された周波数制御信号に基づいて、前記バイアス制御回路304によって出力されたバイアス電流又は発振周波数を制御して出力信号を出力する。

(もっと読む)

81 - 100 / 198

[ Back to top ]