Fターム[5J081KK09]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 一次要因 (534) | 容量 (335) | 素子内容量 (235) | バラクタダイオード (198)

Fターム[5J081KK09]に分類される特許

41 - 60 / 198

低雑音電圧制御発振回路

【課題】 電源雑音を除去し、低周波雑音の特性を良好にできる低雑音電圧制御発振回路を提供する。

【解決手段】 駆動用トランジスタQ1 のベースとGNDの間にコンデンサC11を設けることで、そのベースに入力される低周波ノイズを除去でき、駆動用トランジスタQ1 をhFEの低いトランジスタとすることで、電源から入力される低周波ノイズを除去することができ、発振用トランジスタQ2 のエミッタ側に、コイルL3 を設けることで、周波数特性を広域化して位相雑音の周波数特性を良好にでき、発振用トランジスタQ2 のエミッタ側に、コンデンサC7 とコイルL3 で構成される共振回路における共振周波数をVCOの発振周波数帯域の中心辺りに設定することで、ノイズの影響を受けにくい発振周波数にすることができる低雑音電圧制御発振回路である。

(もっと読む)

多重補間LC電圧制御発振器

【課題】周波数が、中心周波数近辺の同調範囲内の周波数で制御される発振信号を形成するLC電圧制御発振器の提供。

【解決手段】位相補間電圧制御発振器は、複数のn個の位相シフトセルA及びn−1レベルの加算セルSを内含する。位相シフトセルAは、共通の入力信号を受理し、各々は、その他の位相シフトセルAとは異なる量だけ入力信号を位相シフトさせる。第1レベルの加算セルSは、少なくとも2つの位相シフトセルAの出力を受信し加算し、残りの加算セルレベルの各々は、加算セルSの先行レベルの出力を受理する。最後のレベルは、位相シフトセルAの共通の入力信号としてフィードバックされる出力信号を生成する単一の加算セルSを含む。

(もっと読む)

VCO周波数チューニングのための、オーバーラップする2セグメントキャパシタバンク

【解決手段】(例えばFM受信機中の)VCOは、LC共振タンクを含む。LC共振タンクは、粗同調キャパシタバンクおよび微同調キャパシタバンクを含む。粗同調キャパシタバンクは複数のデジタル制御粗同調キャパシタエレメントを含み、アクティブな際に各々は第1キャパシタンス値を供給する。微同調キャパシタバンクは複数のデジタル制御微同調キャパシタエレメントを含み、アクティブな際に各々は第2キャパシタンス値を供給する。キャパシタミスマッチの現実的な問題に対処するため、VCOチューニング範囲の全体にわたるキャパシタンスオーバーラップが、微キャパシタバンクのデジタル制御微同調キャパシタエレメントの全てがアクティブな場合に、微キャパシタバンクのキャパシタンス値が第1キャパシタンス値より大きくなるように第1及び第2キャパシタンス値を選択することによって生成される。 (もっと読む)

PLL回路

【課題】高周波動作において、互いに容量が異なる複数のコンデンサの組み合わせを切り替えて電圧制御発振器の発振周波数帯域を切り替える際に、全ての発振周波数帯域同士を重なり合わせることが可能なPLL回路を提供することを目的とする。

【解決手段】互いに容量が異なる複数のコンデンサ51−1〜51−nの組み合わせを切り替えることにより発振周波数帯域を切り替える電圧制御発振器2を備えるPLL回路1において、電圧制御発振器2が高周波動作しているとき、容量が比較的大きなコンデンサ52−4又はコンデンサ52−5が選択されなくなる場合、補正用のコンデンサ5−1又はコンデンサ5−2を選択して電圧制御発振器2の全体の容量を大きくする。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

変圧器をベースとしたCMOS発振器

【解決手段】低電圧源で動作可能な変圧器に基づいたCMOS発振器を提供するための技術である。LCタンクは、トランジスタペアのドレインに設けられ、LCタンクのインダクタンスは、トランジスタペアのゲート間のインダクタンスに相互磁気結合される。分離相補型トランジスタペアはLCタンクにも結合される。典型的な実施形態によって、タンク間の3方向結合、トランジスタペアのゲート間のインダクタンス、及び相補型トランジスタペアのゲート間のインダクタンスだけでなくトランジスタペアのゲートにLCタンクが更に供給される。 (もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、可変インダクタ100が備える複数の円弧が共有する中心点Zが1つ存在する。可変インダクタ100は、点Zを中心点とした第1の円周上の円弧で構成された、Y−Y’に関して線対称な第1のインダクタ部Ind1と、点Zを中心点とした第2の円周上の円弧で構成された、Y−Y’に関して線対称な第2のインダクタ部Ind2とを備える。Ind1は、端子D’から端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、端子E’から第端子E’とY−Y’に関して線対称な端子E’’まで延在する。第1の円周の半径r1は、第2の円周の半径r2よりも短い。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、Y−Y’上の点Bを通るY−Y’に関して線対称なインダクタ部Ind1及びInd2を備える。インダクタ部Ind2は、点B以外でインダクタ部Ind1と交わらず、インダクタ部Ind1及びInd2は共に曲線のみで構成される。インダクタ部Ind1の線路長はInd2の線路長よりも短い。Ind1は、Y−Y’上の点Z1を中心点とした円周上の円弧で構成され、端子D’から点Bを通って端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、Y−Y’上の点Z2を中心点とした円周上の円弧で構成され端子E’から点Bを通って端子E’とY−Y’に関して線対称な端子E’’まで延在する。

(もっと読む)

基準周波数制御回路

【課題】 基準周波数を生成する発振回路の発振周波数の変化を抑制可能な基準周波数制御回路を提供する。

【解決手段】 入力信号のレベルに応じた周波数で発振する発振回路からの発振信号が入力され、前記発振信号の周波数に応じた出力電圧を出力する周波数電圧変換回路と、前記出力電圧が所定レベルとなるよう前記入力信号のレベルを制御する制御回路と、を備えることを特徴とする基準周波数制御回路。

(もっと読む)

差動出力発振器

【課題】位相雑音を良好にする。

【解決手段】共振回路11として、第1のトランジスタ2aのコレクタにそれぞれ一端が接続された共振周波数f1の第1の直列共振器5aおよび共振周波数f2(f2≠f1)の第2の直列共振器8aと、第2のトランジスタ2bのコレクタにそれぞれ一端が接続された共振周波数f1の第3の直列共振器5bおよび共振周波数f2の第4の直列共振器8bを用い、第1の直列共振器5aの他端と第3の直列共振器5bの他端を互いに接続するか接地し、また第2の直列共振器8aの他端と第4の直列共振器8bの他端を互いに接続するか接地したものである。

(もっと読む)

バッファ回路

【課題】可変容量ダイオードの最小サイズに制限を有する半導体集積化プロセスによる複数のバッファ回路を用いたVCOにおいて、制御電圧の変化に対する発振周波数の変化を必要に応じて小さくできるようにしたバッファ回路を提供すること。

【解決手段】カスコード接続されたトランジスタQ1〜Q4とL1、L2 インダクタL1、L2により形成されているバッファ回路において、時定数回路素子を構成する可変容量ダイオードD1、D2をトランジスタQ3、Q4のソース端子側に接続したもの。基本動作上でトランジスタQ3、Q4のソース端子の電圧変動が小さくなるので、電圧制御端子Vcont1に印加する電圧を変化させたときの可変容量ダイオードD1、D2による静電容量の変化が小さくなる。制御電圧の変化に対して静電容量の変化が小さくなれば、VCOに適用したときに制御電圧の変化に対する発振周波数の変化が抑制され、安定度が向上する。

(もっと読む)

電圧制御発振回路およびクロック信号生成回路

【課題】制御電圧に対する可変容量の容量値の変化の線形性を向上して位相ノイズを低減した電圧制御発振回路の実現。

【解決手段】制御電圧に応じて発振周波数が変化する発振信号OUT,OUTXを出力する電圧制御発振回路において、印加電圧に応じて容量値が変化する複数の可変容量VAC1-VAC4と、制御電圧を分圧して複数の可変容量に印加する分圧電圧VT,VT1-VT3を生成する分圧電圧生成部R1-R4と、を備える。

(もっと読む)

発振回路

発振回路10は、プッシュ−プッシュ型発振器12と、差動出力部14,15と、第1、第2の出力回路16,18とを備える。プッシュ−プッシュ型発振器12は第1、第2の分岐回路20,22を有する。第1、第2の分岐回路20,22の各々は共通のブリッジ回路28にそれぞれの分圧分岐回路24,26を備える。第1、第2の分圧分岐回路24,26の各々は、直列に接続された一対のマイクロストリップライン30,32;34,36をそれぞれ備える。第1、第2の分圧分岐回路24,26の各々は、それぞれのタップC,Dを有する。両方のタップC,Dは、第1の容量性部材42およびマイクロストリップラインのうちの少なくとも一方によって互いに接続されている。差動出力部は、第1、第2の出力端子14,15を備える。第1の出力端子14は第1の出力回路16を介して第1のノードAに接続されている。第2の出力端子15は第2の出力回路18を介して第2のノードBに接続されている。プッシュ−プッシュ型発振器12の第1、第2のノードA,Bの各々は、第1、第2の分岐回路20,22の両方の共通のノードA,Bである。  (もっと読む)

(もっと読む)

電圧制御発振回路

【課題】製造コストの追加なく一般的に用いられる可変容量素子を利用し、位相雑音特性に優れたRTW形式の電圧制御発振回路を実現できるようにする。

【解決手段】電圧制御発振回路は、ループ状の伝送線路15と、信号線路と接続されたアクティブ回路17と、信号線路と接続され複数の可変容量ユニット23を有する可変容量部21とを備えている。各可変容量ユニット23は、可変容量素子31と、可変容量素子31に制御電位を印加する制御端子41と、可変容量素子31に基準電位を印加する基準電位端子43とを有している。少なくとも2つの可変容量ユニット23は、基準電位が互いに異なっている。

(もっと読む)

発振器

【課題】周波数を高くしても分布定数線路の線路長を長くできてQ値を向上できるとともに、製造誤差を小さく抑えることができる発振器を提供する。

【解決手段】1波長の線路長であって、両端をグランドに接地した分布定数線路16を有し、この分布定数線路16の一端から1/4波長の位置に設けた第1の中間タップに発振トランジスタ27のべースを接続するようにした。これにより、分布定数線路16の線路長が従来の1/4波長の線路長の分布定数線路より長くなり、その分Q値の向上が図れるとともに、製造誤差を小さく抑えることが可能となる。分布定数線路16の長さを1/2波長としても従来の1/4波長の長さの分布定数線路に比べて2倍長くできる。このようにしてもQ値の向上が図れ、また製造誤差を小さく抑えることが可能となる。

(もっと読む)

発振器

【課題】高い発振周波数で動作する場合であっても、十分なストリップライン長を確保することができ、製造誤差によるバラつきを防止すると共に、Qの低下を防止すること。

【解決手段】発振器10は、発振トランジスタ2と、前記発振トランジスタ2のベース−エミッタ間に設けられる第1の帰還コンデンサ4と、前記発振トランジスタ2のコレクタ−エミッタ間に設けられる第2の帰還コンデンサ5と、前記発振トランジスタ2のベースに一端が接続される共振用ストリップライン13と、前記発振トランジスタ2のエミッタ−グラウンド間に設けられるトラップ回路20と、を備え、前記共振用ストリップライン13は、発振周波数において高次共振モードとなる長さを有し、前記トラップ回路20は、前記高次共振モードより低次側の低次共振モードに相当する周波数の信号を減衰させるものである。

(もっと読む)

良好な雑音耐性を有する広帯域電圧制御発振器

【課題】広いレンジに対してその動作周波数を同調させる能力を有し、雑音特性に優れた電圧制御発振器を実現する。

【解決手段】第1及び第2のコイル422、424と第1及び第2の結合コンデンサ402、404は共振回路入力端子から見た時に2極ハイパスフィルタを構成し、共振回路の入力端子上に誘導される低周波数雑音はこの2極ハイパスフィルタにより減衰される。第1の同調ダイオード432は第1の可変容量ダイオード442と同じ可変容量ダイオードを使用し、第1の同調コンデンサ432と第1の可変容量ダイオード442のカソードを接続する。AC雑音は第1の可変容量ダイオード442に渡って現れるのと逆の極性で第1の同調コンデンサ432に渡って現れるので、AC雑音が第1の同調コンデンサ432上の逆バイアス電圧を増加させると、第1の可変容量ダイオード442上の逆バイアス電圧はそれに対応して減少する。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

電圧制御発振回路

【課題】発振周波数を制御するPLL回路で生成可能な制御電圧の最大値を低電圧化しても、可変容量ダイオードに印加される電圧の可変範囲を広げることができ、しかも簡単な回路構成で実現でき、発振器の小型化を図ること。

【解決手段】この電圧制御発振回路1は、発振用トランジスタ2と、可変容量ダイオード16を有し発振用トランジスタ2に接続された共振回路13と、電源電圧が印加される電源端子T2とグラウンドとの間に介挿されると共に可変容量ダイオード16に対して並列に接続されたコレクタ抵抗RCと、コレクタ抵抗RCのグラウンド側の端部とグラウンドとの間に介挿され発振周波数を制御する制御電圧が印加される制御用トランジスタ21とを具備する。

(もっと読む)

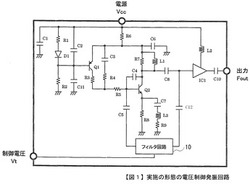

フィルタ回路及び電圧制御発振回路

【課題】双方の信号線路の遅延を容易に一致させることができると共に、不要信号を相殺することができる。

【解決手段】この電圧制御発振回路は、発振回路部1と、発振信号を分岐すると共に互いに位相の反転した第1及び第2の信号を別々に出力する出力分波回路2と、出力分波回路2の出力段に並列に接続され同一構成を有し、トラップ周波数が異なるトラップ回路3、4と、トラップ回路の出力を合成する出力再合成回路とを備える。発振回路部1の電圧制御信号をトラップ回路3、4のバラクタダイオード32,34に印加してトラップ回路3、4のトラップ周波数を発振周波数に連動させる。

(もっと読む)

41 - 60 / 198

[ Back to top ]