Fターム[5J081LL04]の内容

LC分布定数、CR発振器 (9,854) | 改善手段(発明内容) (679) | 部品の追加・削除・変更 (198) | 半導体 (48)

Fターム[5J081LL04]に分類される特許

1 - 20 / 48

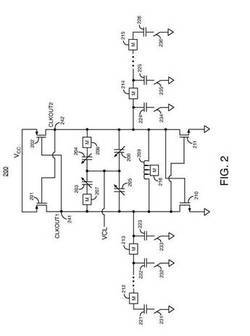

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

アンテナとそれを用いた発振器

【課題】所望の周波数、特に100GHz以上のテラヘルツ帯において共振特性を良好とする新規なアンテナ及びそれを用いた発振器を提供する。

【解決手段】スロットアンテナは、スロットアンテナ本体2となる空隙と、この空隙に対して十字となるように空隙の長手方向に対して垂直方向に一つ以上設けたスリットリフレクタ部3となる空隙とが、導電性平板5に形成されて成り、所望されるインピーダンス又はアドミタンスの周波数特性が得られるようにスリットリフレクタ部3の配置場所、長さ及び幅が定められている。

(もっと読む)

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

電子回路

【課題】負性抵抗回路において反射特性を向上させること。

【解決手段】制御端子、第1端子および第2端子を有する第1トランジスタとQ1、前記第1トランジスタの前記第2端子に接続された制御端子、第1端子およびDC電源が接続される第2端子を有する第2トランジスタQ2と、前記第1トランジスタの前記第1端子と前記第2トランジスタの前記第1端子との信号を前記第1トランジスタの制御端子に共通に帰還させる正帰還回路22と、前記第2トランジスタの前記第1端子と前記正帰還回路との間に接続された第1キャパシタC1と、前記第1トランジスタの前記第2端子と前記第2トランジスタの前記制御端子との間の第1ノードN1と、前記第2トランジスタの前記第1端子と前記第1キャパシタとの間の第2ノードN2と、をDC的に接続する経路12と、を具備する電子回路。

(もっと読む)

発振回路及び半導体装置

【課題】周波数可変範囲の広い発振回路及び発振回路を備えた半導体装置を提供する。

【解決手段】第1の端子と第2の端子との間に接続されたインダクタンス素子と、インダクタンス素子と並列に第1の端子と第2の端子との間に接続された増幅回路と、第1の端子及び第2の端子に接続された第1の容量素子と、を備えた共振型発振回路であって、インダクタンス素子の配線の途中に2箇所以上の引き出し部を設け、2箇所以上設けた引き出し部の間にオンしたときに当該引き出し部間を短絡するスイッチ素子と第2の容量素子とが並列に接続されている。

(もっと読む)

増幅器および発振器

【課題】MOSトランジスタの高周波領域におけるトランスコンダクタンスの劣化を招くことなく、低消費電力化を図ることが可能な増幅器などの提供。

【解決手段】この発明は、MOSトランジスタQ1などを含む増幅器である。MOSトランジスタQ1のゲートには第1の入力信号が入力され、MOSトランジスタQ1のバルクには第2の入力信号が入力され、MOSトランジスタQ1のソースから出力信号が出力される。そして、第1の入力信号と第2の入力信号とは同相の信号である。

(もっと読む)

半導体回路

【課題】安定した動作を行うことができる半導体回路を提供することを課題とする。

【解決手段】ソースが第1の電位ノードに接続される第1のpチャネルトランジスタ(201)と、ソースが第2の電位ノードに接続される第1のnチャネルトランジスタ(202)と、ゲートが第1のnチャネルトランジスタのドレインに接続され、ドレインが第1のnチャネルトランジスタのゲートに接続される第2のpチャネルトランジスタ(203)と、ゲートが第1のpチャネルトランジスタのドレインに接続され、ドレインが第1のpチャネルトランジスタのゲートに接続される第2のnチャネルトランジスタ(204)と、第1のpチャネルトランジスタ及び第1のnチャネルトランジスタのドレイン間に接続される第1の抵抗(301,302)と、第2のpチャネルトランジスタ及び第2のnチャネルトランジスタのドレイン間に接続される第2の抵抗(303,304)とを有する。

(もっと読む)

ウイーンブリッジ発振回路の自動利得制御回路

【課題】ウイーンブリッジ発振回路の自動利得制御回路を、低コストで実現する。

【解決手段】ウイーンブリッジ発振回路を構成するオペアンプの出力を、抵抗3により電流に変換してNPN型バイポーラトランジスタ1のベースに入力し、NPN型バイポーラトランジスタ1のコレクタとエミッタ間の抵抗値を増減することにより、抵抗2と抵抗4とNPN型バイポーラトランジスタ1による合成抵抗を増減し、オペアンプの利得を増減する。

(もっと読む)

バッファ回路

【課題】可変容量ダイオードの最小サイズに制限を有する半導体集積化プロセスによる複数のバッファ回路を用いたVCOにおいて、制御電圧の変化に対する発振周波数の変化を必要に応じて小さくできるようにしたバッファ回路を提供すること。

【解決手段】カスコード接続されたトランジスタQ1〜Q4とL1、L2 インダクタL1、L2により形成されているバッファ回路において、時定数回路素子を構成する可変容量ダイオードD1、D2をトランジスタQ3、Q4のソース端子側に接続したもの。基本動作上でトランジスタQ3、Q4のソース端子の電圧変動が小さくなるので、電圧制御端子Vcont1に印加する電圧を変化させたときの可変容量ダイオードD1、D2による静電容量の変化が小さくなる。制御電圧の変化に対して静電容量の変化が小さくなれば、VCOに適用したときに制御電圧の変化に対する発振周波数の変化が抑制され、安定度が向上する。

(もっと読む)

半導体集積回路

【課題】チップ占有面積が小さく低消費電力の広帯域RF信号処理回路を提供すること。

【解決手段】半導体集積回路は、第1制御端子101の第1制御信号Vc1により制御可能なキャパシタンスCRを有する第1キャパシタ1と、第2制御端子102の第2制御信号Vc2により制御可能なキャパシタンスCLを有する第2キャパシタ3を含み等価的にインダクタLをエミュレートするジャイレータ2、5とからなる共振回路を半導体チップに具備する。キャパシタンスCRとインダクタLは、並列共振回路を構成する。並列共振周波数を変更する際に、第1と第2のキャパシタ1、3のキャパシタンスを協調的に変更する。並列共振回路は増幅素子Q1の出力電極に接続されるアクティブ負荷に好適である。

(もっと読む)

CR発振回路

【課題】 MOSトランジスタ(以下、トランジスタを省略して、単にMOSと表記)のスレッシュホールド電圧が変動しても、正確な発振周波数のCR発振回路を提供する。

【解決手段】 電源端子Vccとアース間に抵抗1とキャパシタ2とが接続され、その接続点にゲートが並列接続されたPMOS3、4と、NMOS6、7のドレインおよびソースが電源端子Vccとアース間に直列に接続され、さらに、PMOS5のソースが、PMOS3、4のドレイン・ソースの接続点に、ゲートがPMOS4とNMOS6のドレインの接続点に、ドレインがNMOS8のゲートにそれぞれ接続され、NMOS8のドレインは電源端子Vccに、ソースはNMOS6、7のソース・ドレインの接続点にそれぞれ接続されている。その出力がインバータ10を介して、キャパシタ2の両端にドレイン・ソースが接続されたNMOS9のゲートに接続されている。

(もっと読む)

発振器の製造方法、及び発振器

【課題】共振状態における電磁波損失が低減され、出力を向上させることが可能な発振器の製造方法、及びその発振器を提供することである。

【解決手段】発振器の製造方法により、発振電磁波に対して利得を有する利得媒質202と電磁波を共振させるための共振器構造を備え、共振器構造が電磁波の伝播方向と垂直な方向を閉じ込めるための導波管構造を有する発振器が製造される。第1の基板200に、利得媒質202を含む半導体多層膜をエピタキシャル成長する。第1の基板200、または第1の基板とは別の第2の基板209に、当該溝205の断面形状で規定されるカットオフ周波数が電磁波の周波数より小さくなる様な形状の溝205を形成する。第1の基板200と第2の基板209によって溝205が挟まれて導波管構造を構成する様に第1の基板と第2の基板を貼り合わせる。

(もっと読む)

電圧制御発振器

【課題】広い範囲の発振周波数において温度補償を行うことができる電圧制御発振器を得る。

【解決手段】本発明に係る電圧制御発振器は、可変容量素子17の両端に印加する電圧により発振周波数を制御するものである。そして、この電圧制御発振器は、制御電圧に応じた周波数制御用の電圧を可変容量素子17の一端に印加する周波数制御バイアス回路21と、制御電圧に応じた第1電流を発生させる第1電流源25と、制御電圧とは独立に温度に応じた第2電流を発生させる第2電流源26と、第1,第2電流を足し合わせた電流を電圧に変換する変換用抵抗27と、変換用抵抗27により変換された電圧に応じた温度補償用の電圧を可変容量素子17の他端に印加する温度補償バイアス回路23とを備える。

(もっと読む)

発振器

【課題】小型で低コストであり、かつ負荷変動、高調波レベルおよびC/N比を改善することが可能な発振器を提供する。

【解決手段】発振器は、第1発振周波数の第1発振信号を第1中間ノードN1を介し出力端子Toutに出力する第1発振部10と、絶縁層を有し、第1発振部10を実装する実装部と、絶縁層に設けられ、第1中間ノードN1とグランドとの間に結合された第1線路S11と、絶縁層に設けられ、第1中間ノードN1と電源端子Tbとの間に結合された第2線路S21と、絶縁層に設けられ、第1中間ノードN1と出力端子Toutとの間に結合された第3線路S31と、を具備する。

(もっと読む)

発振器

【課題】発振周波数変更機能を備えた発振器において、不揮発性メモリからデータを読み出す際に発振周波数が変更されることなく安定的に読み出すことができる。

【解決手段】LSIの外部に設けられた不揮発性メモリ15に、発振回路13から発振されるクロック信号の周波数を変更するための周波数設定値が記憶されており、その周波数設定値が、発振回路13から発振される初期設定された周波数のクロック信号によって読み出されると、ダミーレジスタ11に格納される。不揮発性メモリ15からデータが全て読み出されてロード動作完了信号が出力されると、ダミーレジスタ11から記憶レジスタ12へ周波数設定値が格納され、発振回路13の発振周波数が周波数設定値とされる。

(もっと読む)

電圧制御発振器

【課題】LC共振器の容量を電圧制御発振器に印可される制御電圧によって自動的に変化させることにより広帯域な可変容量範囲を得え、その結果従来より広帯域な発振周波数領域を得ることができる電圧制御発振器を提供する。

【解決手段】電圧制御発振器は、電流源回路部1と、電流源回路部1に接続されたLC共振器回路部2と、LC共振器回路部2に接続された増幅器回路部3とを具備している。LC共振器回路部2は、インダクタンス部L1、L2と、容量部と、制御電圧端子ctrlとを有し、容量部は、直列接続されたバラクタ素子D1、D2及びMOSFET(M1、M2)を含み、制御電圧端子ctrlは、MOSFETの制御電極(ゲート)及びバラクタ素子のカソードに接続され、制御電圧端子ctrlに印加される制御電圧は共振器回路を構成する容量を従来より大きく変化させることができる。

(もっと読む)

水晶発振回路

【課題】CMOSインバータで構成される発振回路の閾値電圧VTの温度変動に起因する消費電流や、負性抵抗などのさまざまな特性変動を大幅に改善することができる水晶発振回路を提供する。

【解決手段】水晶振動子を備えたCMOSインバータ型発振回路4の電源電圧に温特付き電源回路31の出力部を接続し、前記温特付き電源回路31はアンプ2とダイオード20と抵抗11で構成され、前記アンプ2の出力端V2はダイオード20のアノードに接続され、前記ダイオード20のカソード側は前記アンプ2の負入力端V3と抵抗11の一端に接続され、前記抵抗11の他端は接地され、アンプ2の正入力端V1にはVCC変動の少ない電圧源1に接続される。

(もっと読む)

電圧制御発振回路

【課題】ICへの集積化が容易で、かつ、ノイズの発生を低減することも可能な電圧制御発振器を提供する。

【解決手段】抵抗R1,R2と、クロスカップルされた発振用のペアトランジスタM1,M2による正帰還回路と、可変容量ダイオードD1,D2と、可変容量ダイオードD1,D2に対して固定のバイアス電圧を与えるバイアス回路M4,M5とを備え、可変容量ダイオードD1,D2の容量値を同調電圧VTによって可変させることで発振周波数を制御できるようにすることにより、IC化に向かないインダクタや大きな電流性ノイズを出しやすい定電流源を用いずに電圧制御発振器を構成する。

(もっと読む)

電圧制御発振器

【課題】ICへの集積化も容易で、かつ、浮遊容量の発振周波数への影響も効果的に低減することが可能な電圧制御発振器を提供する。

【解決手段】バリキャップVC3,VC4のアノード共通接続点に設けられた第1のスイッチ回路P1と、第1の制御電圧Vtの供給配線上に設けられた第2のスイッチ回路P2と、バリキャップVC3,VC4の各アノードと第2の制御電圧VCONTの入力端子との間にそれぞれ接続された複数の抵抗R1,R2とを備え、バリキャップVC3,VC4を切り離すために第1のスイッチ回路P1をオフにしたときは、バリキャップVC3,VC4が抵抗R1,R2を介して第2の制御電圧VCONTの入力端子に接続されるようにし、バリキャップVC3,VC4を使用するときは第1および第2のスイッチ回路P1,P2をオンとし、同調電圧Vtによって発振周波数を制御できるようにする。

(もっと読む)

1 - 20 / 48

[ Back to top ]