Fターム[5J081MM02]の内容

LC分布定数、CR発振器 (9,854) | 図面情報 (928) | 波形図 (48)

Fターム[5J081MM02]に分類される特許

1 - 20 / 48

半導体装置

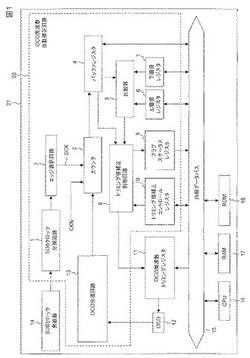

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

発振回路及び発振器

【課題】発振子と発振回路とのインピーダンス整合を容易にとることができる発振回路及び発振器を提供する。

【解決手段】発振回路100が、第1の入力端子4と、第1の出力端子5と、第1の入力端子4に接続される信号調整部10と、第1の入力端子4及び第1の出力端子5に接続される信号形成部20と、を含み、該信号調整部は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有し、第1の素子13は、一方端が第1の入力端子4に接続され、他の一方端が第1の抵抗11の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源2に接続され、第2の抵抗は、他の一方端が第2の電源3に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続され、該信号形成部において、第1の出力端子から出力される信号は、第1の入力端子から入力された信号を基に形成される。

(もっと読む)

発振器

【課題】簡単な構成で高速立ち上げが可能であり、さらに従来のリング型電圧制御発振器に比べて安定な周波数の信号を生成することができる発振器を提供する。

【解決手段】制御電圧入力端子に印加された制御電圧に従って発振周波数が変化するリング型電圧制御発振器10と、リング型電圧制御発振器10の出力信号を一定時間幅のパルス信号に変換して出力するパルス整形回路20と、参照電圧からパルス整形回路20が出力する周波数が変化するパルス信号の平均電圧を差し引いた電圧を積分してリング型電圧制御発振器10の制御電圧入力端子に出力する積分回路30とを備える。

(もっと読む)

発振器、および発振を開始する方法

【課題】休止期間は消費電力を削減すると共に起動特性のよい発振器を提供する。

【解決手段】発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路412と、前記発振回路に第1の電流を供給する第1の制御可能電流源404と、発振回路に第2の電流を供給する第2の制御可能電流源408と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

プッシュプッシュ発振器及び位相ずれ監視方法

【課題】位相ずれを確認する技術を提供する。

【解決手段】プッシュ・プッシュ発振回路100は、相互に逆位相で動作する、2つの発振器1、2と、2つの発振器1、2から出力された第1出力信号を合成する合成器101と、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を監視するための基本波監視回路102と、を備えている。即ち、基本波監視回路102を用いることで、合成器101から出力された第2出力信号に含まれる第1出力信号の基本波を確認することができる。第1出力信号の基本波を確認することで、合成器101に入力された2つの第1出力信号が逆位相であったか確認することができる。

(もっと読む)

発振回路

【課題】小型かつノイズ抑制に優れる発振回路を提供すること。

【解決手段】本発明にかかる発振回路100は、インバータ1及び2、タンク回路3を有する。タンク回路3は、出力ノードOUTTと出力ノードOUTBとの間に並列に接続される。インバータ1は、ドレインが出力ノードOUTBに接続されたn型MISトランジスタM1及びp型MISトランジスタM3を有する。インバータ2は、ドレインが出力ノードOUTTに接続されたn型MISトランジスタM2及びp型MISトランジスタM4を有する。p型MISトランジスタM3及びM4のゲート端子は、それぞれ出力ノードOUTT及びOUTBと直接的に接続される。n型MISトランジスタM1及びM2のゲート端子は、それぞれ結合容量CG1及びCG2を介して出力ノードOUTT及びOUTBと接続され、抵抗CG1及びCG2を介してバイアス電圧VBIASが印加される。

(もっと読む)

発振器

【課題】後段にフィルタを挿入しなくても、低歪みの発振波形を得ることが可能な発振器を提供する。

【解決手段】発振器100は、MOSFETである第1トランジスタM1および第2トランジスタM2を有するクロスカップルドインバータ10を備える。この発振器100は、発振動作中に、第1トランジスタM1、第2トランジスタM2それぞれのゲートソース間電圧Vgs1、Vgs2、ドレインソース間電圧Vds1、Vds2、ゲートソース間しきい値電圧Vth1、Vth2の間に、

Vds1≧Vgs1−Vth1

Vds2≧Vgs2−Vth2

なる関係が成り立つよう構成される。

(もっと読む)

発振回路

【課題】従来の発振回路では、出力信号のジッタを抑制できない問題があった。

【解決手段】本発明の発振回路は、発振周波数設定電流に基づき蓄積された電荷量に応じて発振周波数制御電圧Vcpを生成するフィルタコンデンサCpumpと、発振周波数制御電圧Vcpに応じて出力する発振信号Foutの周波数を変動させる発振器30と、発振信号Foutの周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する制御回路40と、タイミング制御信号に基づき発振信号Foutの周期の長さに応じて連続的に電圧レベルが変化する周波数検出電圧Vcapを生成する周波数検出回路10と、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて発振周波数設定電流を連続的に可変してフィルタコンデンサCpumpに出力する差動増幅器20と、を有する。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

電圧制御発振器及びそれを備えた無線通信装置

【課題】バイアス抵抗の抵抗値を大きい値に維持して省電力化及び発振効率の向上を図りつつ、広帯域の変調信号に対応することができる電圧制御発振器及びそれを備えた無線通信装置を提供すること。

【解決手段】

印加される電圧に応じて静電容量値が変化するバラクタM1,M2を有し、当該バラクタM1,M2に制御端子T2を介して印加される制御信号に応じて共振周波数が変化する共振回路30と、共振回路30と並列に接続された負性抵抗回路40とを備え、制御信号の逆相信号が制御端子T3を介して印加されるキャパシタC3、C4をバラクタM1,M2に接続した。

(もっと読む)

MOSFETのソースバルク電圧を用いた信号処理ASIC用の温度補償RC発振器

温度補償CMOS RC発振回路は、抵抗と温度相関バイアス電流とを用いてソースバルク電圧を変化させて、温度に対するMOSFETの閾値電圧の変動を安定させる。この温度層間バイアス電流はまた、抵抗を流れる。温度が上昇すると、バイアス電流も増え、MOSFETのソースバルク電圧を上昇させる。上昇したソースバルク電圧は、高い温度にてMOSFETの閾値電圧を安定させるのを補助する。この発振器には省電力ロジックも組み込まれており、低い電力消費で高い周波数が得られる。本発明では、得られる発振器が低出力設計となってしまう高利得オペアンプや高速比較器はなく、他のシステムとともにシングルチップに組み込むことができる。 (もっと読む)

半導体回路

【課題】安定した動作を行うことができる半導体回路を提供することを課題とする。

【解決手段】ソースが第1の電位ノードに接続される第1のpチャネルトランジスタ(201)と、ソースが第2の電位ノードに接続される第1のnチャネルトランジスタ(202)と、ゲートが第1のnチャネルトランジスタのドレインに接続され、ドレインが第1のnチャネルトランジスタのゲートに接続される第2のpチャネルトランジスタ(203)と、ゲートが第1のpチャネルトランジスタのドレインに接続され、ドレインが第1のpチャネルトランジスタのゲートに接続される第2のnチャネルトランジスタ(204)と、第1のpチャネルトランジスタ及び第1のnチャネルトランジスタのドレイン間に接続される第1の抵抗(301,302)と、第2のpチャネルトランジスタ及び第2のnチャネルトランジスタのドレイン間に接続される第2の抵抗(303,304)とを有する。

(もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

電圧制御発振器

【課題】低電源電圧の条件下にあっても、安定した発振の起動及び持続を保証しつつ低位相雑音化を達成することができる電圧制御発振器を提供する。

【解決手段】制御入力電圧に応じてインピーダンスが変化するLC並列共振回路と、該LC並列共振回路に負性抵抗を導入する負性抵抗回路と、を含む電圧制御発振器において、該負性抵抗回路が、該LC並列共振回路に並列に設けられ、キャパシタを介してクロスカップリングされた第一のトランジスタ対を有し、該第一のトランジスタ対の各トランジスタのゲートが第一のバイアス電圧にバイアスされて、C級増幅動作をする第一の増幅回路と、同様の回路構成を有し、各トランジスタのゲートが該第一のバイアス電圧と異なる第二のバイアス電圧にバイアスされて、C級増幅動作をする第二の増幅回路と、を少なくとも含む。

(もっと読む)

自動調整発振器

【課題】チャージポンプを用いずに、出力周波数の精度を高くすることのできる自動調整発振器を提供する。

【解決手段】発振器10は、発振回路11、第1電圧供給回路13、第2電圧供給回路14及び調整値生成回路16を備えている。第1電圧供給回路13は、基準時間で第1電圧V1が基準電圧Vrefに到達するような時定数となる抵抗値の抵抗器R1とキャパシタン

スのキャパシタC1とを備える。第2電圧供給回路14は、発振回路11の周波数に応じたパルス信号S1,S2によってスイッチングを行なう第1及び第2スイッチング手段SW1,SW2によって第2電圧V2を上昇させる。調整値生成回路16は、第2電圧V2が第1電圧V1よりも先に基準電圧Vrefになった場合には、周波数を低くする調整値を

発振回路11に供給し、第2電圧V2が第1電圧V1よりも遅れて基準電圧Vrefになっ

た場合には、周波数を高くする調整値を発振回路11に供給する。

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

発振回路

【課題】従来の発振回路は、発振信号を増幅させる電流等の影響で発振周波数の高速化が制限されるという問題があった。

【解決手段】本発明にかかる差動発振回路は、帰還ループ回路を備えた差動型の発振回路であって、帰還ループ回路上に縦続接続され、入力された一対の差動入力信号を遅延させて一対の差動出力信号として出力する遅延回路2〜5と、発振回路が発振起動状態か安定状態のいずれかにあるかを検出し、検出結果を示す検出信号VSTPを出力する発振起動検出回路7と、を備える。さらに遅延回路2〜5は、発振起動検出回路7から出力された検出信号VSTPに基づいて、差動出力信号の出力電流値を制御する。このような回路構成により、発振周波数の高速化が可能である。

(もっと読む)

1 - 20 / 48

[ Back to top ]