Fターム[5J098AA11]の内容

能動素子を用いた回路網 (5,588) | 回路素子 (1,159) | 抵抗 (319)

Fターム[5J098AA11]の下位に属するFターム

Fターム[5J098AA11]に分類される特許

1 - 20 / 267

信号等化器

スプリッタ回路およびチューナーシステム

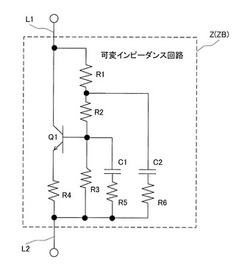

ポジショナ

【課題】低周波のノイズの影響に強いポジショナを提供する。

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

フィルタ回路及び受信装置

【課題】低雑音かつ低カットオフ周波数のフィルタ回路をより小面積で実現する。

【解決手段】フィルタ回路(1〜5)は、入力端子(Iinp、Iinm、(Vinp、Vinm))に供給された入力信号を受け、信号を増幅して出力端子(Voutm、Voutp)に出力する第1回路(10、11)と、第1容量素子(Ch_A、Ch_B)を介して前記第1回路の出力信号を入力する第1差動増幅回路(OP2)と、前記第1差動増幅回路(OP2)の入出力間に負帰還経路を形成する第1抵抗素子(Rh_A、Ch_B)と、前記第1差動増幅回路の出力と前記第1回路の入力との間に負帰還経路を形成する第2抵抗素子(R3_A、R3_B)とを有する。

(もっと読む)

アクティブインダクタ

【課題】アクティブインダクタを提供する。

【解決手段】ソース、ドレイン、及びゲートを含むpMOSトランジスタであって、前記pMOSトランジスタの前記ソースが電源Vddと接続し、抵抗Rの一端が前記pMOSトランジスタの前記ゲートに接続し、前記抵抗Rの他端が前記pMOSトランジスタの前記ドレインに接続している回路において、電源からの直流バイアスの略フルレンジに対して、インダクテイブインピーダンスを生成し、インダクタの特性を有する。

(もっと読む)

フィルタ装置およびその制御方法

【課題】フィルタのノッチ周波数を調整する機能を持ったフィルタ装置を提供する。

【解決手段】入力信号を抵抗109と可変容量110、アクティブインダクタ111を備えたフィルタコア部102にて分圧し、フィルタコア部102のフィルタ特性信号Vfの振幅と基準振幅とを比較する振幅比較回路101、振幅比較回路101での比較結果に基づいてアクティブインダクタ111の位相を制御する位相制御部108、フィルタコア部102のフィルタ特性信号Vfの周波数と基準周波数とを比較する周波数比較回路103、周波数比較回路103の比較結果に基づいて可変容量110の容量を制御する可変容量制御部117によってフィルタ装置を構成し、アクティブインダクタ111の位相、可変容量11の容量が制御される間、アクティブインダクタ111の位相制御部108が、フィルタコア部102を発振させる。

(もっと読む)

直交信号生成回路、直交信号生成回路の調整方法、及び無線通信装置

【課題】高周波の広い範囲で周波数が高速で切り替わり、正確に位相が90度異なる直交信号を消費電力が少ない回路で生成する。

【解決手段】可変利得アンプ9によって増幅した信号を、ポリフェイズフィルタ1を通すことで、大まかに位相差が90度となる直交信号を生成する。ディジタル制御回路8からのディジタル信号で制御された可変利得アンプ2,3により、直交信号を増幅する。可変利得アンプ2,3の出力信号の振幅を振幅検出器4,5によって検出し、可変利得アンプ2,3の出力信号の振幅が等しくなるように、可変利得アンプの利得をディジタル制御回路8によって疎調整する。この疎調整に加えて、後述する微調整を行うことで、可変利得アンプ2,3の出力信号の振幅を等しくする。

(もっと読む)

バンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路

【課題】センター周波数を実質的に変化させずに帯域幅を可変することが可能なバンドパスフィルタ回路を備えた集積回路、バンドパスフィルタ回路の制御方法、その制御プログラム及びその制御方法を実行するロジック回路を提供すること

【解決手段】本発明にかかる集積回路106は、楕円関数型のバンドパスフィルタ回路100及び制御部105を備える。バンドパスフィルタ回路100は、センター周波数f1を設定する第1LCフィルタ回路部101及び第4LCフィルタ回路部104、共振周波数f2、f3をそれぞれ設定する第2LCフィルタ回路部102、第3LCフィルタ回路部103を備える。前記制御部105は、第2LCフィルタ回路部102が設定するインダクタンス値L2、容量値C2及び第3LCフィルタ回路部103が設定するインダクタンス値L3、容量値C3を可変させて、共振周波数f2及びf3を、互いに増減が逆になるように変化させる。

(もっと読む)

半導体装置

【課題】省面積化されたローパスフィルタを備える半導体装置を提供する。

【解決手段】第1のノードと第2のノードとの間に接続され、印加される電圧に応じて内部容量が変化する可変容量素子と、第1のノードと第2のノードとの間に可変容量素子と並列に接続される電圧増幅部とを備え、電圧増幅部は、第1のノードと電気的に接続される増幅器と、増幅器の出力の電圧をシフトさせるレベルシフト回路とを含み、レベルシフト回路の出力は第2のノードと電気的に接続される。

(もっと読む)

オーディオ用GIC回路

【課題】オーディオ用アクティブ型フィルター、特にGICフィルターにおいて遮断周波数以降で発生する特性劣化(遮断特性の跳ね返り)を2次LCフィルターの追加により補償する事、およびGICフィルターのピーキング特性を維持しながらGIC遮断限界以上で所定の遮断特性を実現する事。

【解決手段】2次LCフィルターの終端抵抗としてFDNR(Frequency Dependent Negative Resistors)を用いる事、およびLCフィルターと直列に制動抵抗(1)を接続する事で共振特性を備えた2次LCフィルターを実現しGIC遮断限界以上で所定の遮断特性を実現する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

バンドパスフィルタ及びバンドパスフィルタのキャリブレーション方法

【課題】BPFを構成するOTAの個数を削減し,低消費電力で高次のバンドパスフィルタを提供する。

【解決手段】バンドパスフィルタは,入力信号が入力されるハイパスフィルタ(14)と,ハイパスフィルタの出力が反転入力端子に入力され,反転入力端子と非反転入力端子間の入力電圧を増幅して出力信号を出力端子に出力するアンプ(10)と,アンプの非反転出力端子と反転入力端子との間に接続された第1抵抗(R2)と,反転入力端子に第1端子が接続された第1キャパシタ(C2)と,アンプの非反転出力端子の出力信号の極性を反転し,当該反転した信号をキャパシタの第2端子に出力する反転アンプ(12)とを有する。

(もっと読む)

差動単相変換回路

【課題】温度やプロセス条件のばらつきの影響を受けず,高いCMRR特性を有する差動単相変換回路を提供する。

【解決手段】差動単相変換回路は,逆相関係にある一対の差動信号のうちの第一の差動信号を増幅するとともに,第一の差動信号を同相で出力する第一の増幅回路と,差動信号のうちの第二の差動信号を増幅するとともに,第二の差動信号の位相を反転させて出力する第二の増幅回路と,第一の増幅回路からの出力信号と第二の増幅回路からの出力信号を合成して出力する出力端子とを備え,第二の増幅回路は,複数のトランジスタをカスコード接続したカスコード回路である。

(もっと読む)

半導体集積回路およびその動作方法

【課題】半導体集積回路に集積化された内蔵フィルタの周波数特性を正確に設定すること。

【解決手段】半導体集積回路は、フィルタ回路(1)と、カットオフ周波数補償回路(2)と、Q値補償回路(3)とを具備する。カットオフ周波数補償回路(2)は、フィルタ回路(1)の容量成分(C1、C2)を調整することによってフィルタ回路のカットオフ周波数を所望の値に調整する。Q値補償回路(3)は、カットオフ周波数補償回路(2)によるフィルタ回路(1)のカットオフ周波数の調整の後に、フィルタ回路(1)の抵抗成分(R3)を調整することによってフィルタ回路(1)のQ値を所望の値に調整する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DCオフセットキャンセル動作の動作期間を短縮する。

【解決手段】フィルタ処理と増幅機能を有するアクティブローフィルタ300の差動出力端子に2個の校正抵抗R22の一方の端子が接続され、2個の校正抵抗R22の他方の端子に電圧比較器CMPの2個の入力端子と切り換えスイッチSWIOの2個の端子が接続される。DCオフセット電圧低減のデジタル制御信号DACS、DAC2…DAC0を算出する算出期間で、デジタルアナログ変換器DAC0のアナログ電流による一方の校正抵抗R22の電圧降下に依存する校正電圧を電圧比較器CMPが検出する。DCオフセット電圧を低減する校正期間では、デジタル制御信号に応答したデジタルアナログ変換器の校正アナログ電流が切り換えスイッチSWIOを介してフィルタ300の入力側に流される。

(もっと読む)

インピーダンス整合回路、インピーダンス整合方法及び双方向伝送回路

【課題】オープンドレイン出力バッファ間で双方向の伝送を行う際のインピーダンスを整合させて、誤動作することなく高速通信すること。

【解決手段】インピーダンス整合回路は、第1の端子にオープンドレイン出力バッファ、第2の端子に双方向伝送線路が接続され、オープンドレイン出力バッファからの第1の出力信号及び双方向伝送線路からの第2の出力信号を検出する検出回路と、第1の出力信号の電圧の変化が第1の方向であると検出された場合、当該第1の出力信号に負荷抵抗を接続して双方向伝送線路へ出力し、第1の出力信号の電圧の変化が第1の方向とは逆の第2の方向であると検出された場合、当該第1の出力信号にダンピング抵抗を接続して双方向伝送線路へ出力し、第2の出力信号の電圧の変化が検出された場合、当該第2の出力信号に負荷抵抗及びダンピング抵抗のいずれも接続せずにオープンドレイン出力バッファへ出力する抵抗接続回路とを有する。

(もっと読む)

可変減衰器

【課題】状態切替時の通過位相差を抑えつつ、回路サイズを小さくすることができる可変減衰器を提供する。

【解決手段】可変減衰器は、第1の入出力端子1aと、第2の入出力端子1bと、第1のスイッチング素子としての第1のFET2aと、第2のスイッチング素子としての第2のFET2bと、第1の抵抗3aと、第2の抵抗3bと、第3の抵抗3cと、第1のインダクタ4aと、第2のインダクタ4bとを有している。第1のインダクタ4aのインダクタンスは、動作周波数において第1のFET2aのオフ容量と共振するような値に予め設定されている。第2のインダクタ4bのインダクタンスは、動作周波数において第2のFET2bのオフ容量6bと共振するような値に予め設定されている。

(もっと読む)

アクティブフィルタ

【課題】フィルタのQ値が変動することがないアクティブフィルタを提供する。

【解決手段】位相容量素子を含む演算増幅器、フィルタ用抵抗素子、フィルタ用容量素子、バイアス回路を含むアクティブフィルタにおいて、バイアス回路を、ゲート同士が接続されるMOSTr41、42、MOSTr41とドレイン同士が接続されるMOSTr43、MOSTr44とゲート同士が接続され、MOSTr42とドレイン同士が接続されるMOSTr44、MOSTr41またはMOSTr42のうちのいずれか1つのソースに接続される抵抗素子45、MOSTr41のドレインに接続される出力端子46またはMOSTr44のドレインに接続される出力端子47によって構成し、抵抗素子45を、フィルタ用抵抗素子と同じプロセス条件で製造し、位相補償容量素子をフィルタ用容量素子と同じプロセス条件で製造する。

(もっと読む)

位相調整回路、検出装置及び電子機器

【課題】信号の位相を高精度に調整可能な位相調整回路、検出装置及び電子機器等を提供すること。

【解決手段】位相調整回路は、位相主調整用のローパスフィルター210と、位相微調整用のハイパスフィルター230を含む。ローパスフィルター210は、周波数finの第1の信号が入力され、その周波数finにおける位相遅れ角度がX度(X≧0)となる周波数特性を有する。ハイパスフィルター230は、ローパスフィルター210からの出力信号LQに基づく第2の信号GQが入力され、周波数finにおける位相進み角度がY度(Y≧0)となる周波数特性を有する。Y度はX度よりも小さい値に設定される。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

1 - 20 / 267

[ Back to top ]