Fターム[5J098AC06]の内容

能動素子を用いた回路網 (5,588) | 回路特性を可変するための構成 (1,170) | 可変対象 (381) | インピーダンス (80)

Fターム[5J098AC06]に分類される特許

1 - 20 / 80

ポジショナ

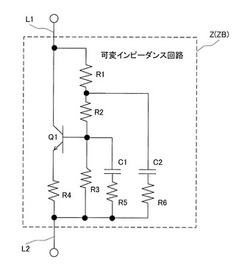

【課題】低周波のノイズの影響に強いポジショナを提供する。

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

無線通信装置、マッチング制御回路、マッチング制御方法

【課題】RSSI(受信信号強度)を用いたパワーマッチングではノイズが反映されておらず最適な受信感度を実現することができなかった。

【解決手段】本発明の無線通信装置は、アンテナで受信した受信信号に対してインピーダンスマッチングを行うマッチング手段と、前記インピーダンスマッチングが行われた受信信号のノイズが反映された品質指標を算出する品質指標算出手段と、前記ノイズが反映された品質指標に基づいて前記マッチング手段が行うインピーダンスマッチングのマッチング定数を制御する制御手段と、を具備する。当該構成によれば、ノイズを考慮した上でのマッチング制御を行うことができるため、受信感度の最良化を図ることができる。

(もっと読む)

アクティブインダクタ

【課題】アクティブインダクタを提供する。

【解決手段】ソース、ドレイン、及びゲートを含むpMOSトランジスタであって、前記pMOSトランジスタの前記ソースが電源Vddと接続し、抵抗Rの一端が前記pMOSトランジスタの前記ゲートに接続し、前記抵抗Rの他端が前記pMOSトランジスタの前記ドレインに接続している回路において、電源からの直流バイアスの略フルレンジに対して、インダクテイブインピーダンスを生成し、インダクタの特性を有する。

(もっと読む)

オーディオ機器

【課題】入力端子に接続されたソース機器に合わせて入力インピーダンスやゲインを設定可能なオーディオ機器を提供する。

【解決手段】ホット端子およびコールド端子を有しソース機器が接続される入力端子と、インピーダンス素子と、キャパシタと、テスト信号発生部と、リターン信号解析部と、通常動作時にインピーダンス素子を入力端子に並列に接続し、ソース機器のインピーダンス検出時にコールド端子にテスト信号発生部を接続するとともにホット端子にキャパシタおよびリターン信号解説部を接続する切替スイッチとを備え、ソース機器のインピーダンス検出時に、テスト信号発生部はテスト信号を発生し、リターン信号解析部はホット端子に戻ってきたテスト信号であるリターン信号に基づいてソース機器のインピーダンスを検出する。

(もっと読む)

可変容量回路

【課題】キャパシタが破壊されずAC信号が歪まないようにした可変容量回路を提供する。

【解決手段】可変容量回路は,基準電位を中心とする交流信号が印加される所定ノードと,所定ノードに接続される第1のキャパシタと,第1のキャパシタと基準電位との間に接続された第2のキャパシタと,第2のキャパシタと第1のキャパシタとの間の第1のノードと基準電位との間に設けられた第3のキャパシタ及び容量制御用のトランジスタと,第3のキャパシタとトランジスタとの間の第2のノードに第1のバイアス電圧を印加するバイアス回路とを有する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

インピーダンス整合回路、インピーダンス整合方法及び双方向伝送回路

【課題】オープンドレイン出力バッファ間で双方向の伝送を行う際のインピーダンスを整合させて、誤動作することなく高速通信すること。

【解決手段】インピーダンス整合回路は、第1の端子にオープンドレイン出力バッファ、第2の端子に双方向伝送線路が接続され、オープンドレイン出力バッファからの第1の出力信号及び双方向伝送線路からの第2の出力信号を検出する検出回路と、第1の出力信号の電圧の変化が第1の方向であると検出された場合、当該第1の出力信号に負荷抵抗を接続して双方向伝送線路へ出力し、第1の出力信号の電圧の変化が第1の方向とは逆の第2の方向であると検出された場合、当該第1の出力信号にダンピング抵抗を接続して双方向伝送線路へ出力し、第2の出力信号の電圧の変化が検出された場合、当該第2の出力信号に負荷抵抗及びダンピング抵抗のいずれも接続せずにオープンドレイン出力バッファへ出力する抵抗接続回路とを有する。

(もっと読む)

半導体装置

【課題】半導体装置は、必要に応じてダイナミックレンジを確保し、且つ低消費電流化に資するフィルタ回路を備える。

【解決手段】半導体装置は、トランスコンダクタンス増幅器(103a〜103d、203a〜203d)とキャパシタ(104a、104b)から構成されるフィルタ回路(10、20)を有し、前記フィルタ回路は、妨害信号の電界強度を検出し、検出結果に基づいて、前記トランスコンダクタンス増幅器の差動入力段トランジスタのソース側のインピーダンスと前記トランスコンダクタンス増幅器のバイアス電流の双方を調整するための制御を行う。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

可変減衰器

【課題】 従来の可変減衰器では、高周波信号を損失少なく通過させる基準状態と、所望の減衰量を得る減衰状態との間で、通過位相差を生じてしまうという課題があった。

【解決手段】 入出力間FET3と並列、定位相可変減衰器4と直列に位相補正用FET5を設置することで、入出力間FET3がオン状態のときは位相補正用FET5をオフ状態とし、入出力間FET3がオフ状態のときは位相補正用FET5をオン状態とすることによって、基準状態と減衰状態との間で通過位相を等しくすることができる。

(もっと読む)

可変抵抗制御回路及び可変抵抗器

【課題】抵抗を広い範囲で変化させることができる可変抵抗制御回路及び可変抵抗器を提供すること

【解決手段】本発明にかかる可変抵抗制御回路は、電源10と、電源10よりも低い電位を有する電源11との間に設けられ、電源10と接続される抵抗21と、電源10と、電源11との間に設けられ、前記抵抗21と直列に接続されるMOSトランジスタ31と、電源10と、電源11との間に設けられ、前記MOSトランジスタ31と直列に接続されるMOSトランジスタ32と、抵抗21とMOSトランジスタ31との節点における電圧と、制御電圧とに基づいて、MOSトランジスタ32にゲート電圧を出力するオペアンプ41とを備え、オペアンプ41は、ゲート電圧に基づいて抵抗値が制御される外部の可変抵抗に対してゲート電圧を出力するものである。

(もっと読む)

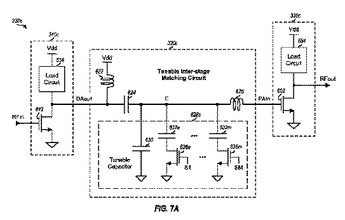

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

抵抗増倍回路

【課題】チップ面積の増大を招くことなく、半導体材料に起因するhfeのばらつきなどに影響されることのない安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に抵抗器3の一端が接続され、抵抗器3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、抵抗器3の他端に接続されて、信号入力端子8から見た抵抗器3の見かけ上の抵抗値が1/(1+N)倍に見えるものとなっている。

(もっと読む)

終端抵抗調整回路

【課題】入力差動信号のコモン電圧が変化しても、終端抵抗を一定に保持でき、かつ、簡易な回路構成の終端抵抗調整回路。

【解決手段】抵抗値を調整可能な第1の終端抵抗回路と、第1の終端抵抗回路と並列に接続され、抵抗値を調整可能な第2の終端抵抗回路と、第1及び第2の終端抵抗回路の抵抗値を調整するための調整用抵抗回路と、調整用抵抗回路により定まる第1の電圧と、外部に接続された基準抵抗により定まる第2の電圧とが入力され、両電圧が等しくなるように動作するとともに、第1及び第2の終端抵抗回路に対し抵抗調整信号を出力する第1の増幅回路と、第1の終端抵抗回路が接続された第1の端子と、第2の終端抵抗回路が接続された第2の端子と、第1及び第2の端子に与えられる差動信号のコモン電圧に基づく電圧と、第1又は第2の電圧とが入力され、両電圧が等しくなるように動作する第2の増幅回路と、を備える終端抵抗調整回路。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

寄生容量により誘導される誤差が減少されたセンサデバイス

デバイス110は、駆動ノード34,36および感知ノード42,44を有する感知素子26を備えている。駆動ノード34および感知ノード42との間には寄生容量22が存在する。同様に、駆動ノード36と感知ノード44との間には寄生容量24が存在する。駆動信号56が駆動ノード34、36との間に印加されると、駆動ノード34と感知ノード42との間の寄生電流70および駆動ノード36と感知ノード44との間の寄生電流72が寄生容量22,24のおかげで生成される。容量性ネットワーク112を介して寄生電流70を打ち消す補正電流134を生成するために、駆動ノード36と感知ノード42との間に容量ネットワーク112が接続される。同様に、容量性ネットワーク112を介して寄生電流72を打ち消す補正電流138を生成するために、駆動ノード34と感知ノード44との間に容量性ネットワーク114が接続される。  (もっと読む)

(もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

アクティヴインダクタ

【課題】出力電流雑音の変動しない可変型アクティヴインダクタを提供すること。

【解決手段】トランジスタのゲート−ソース間に並列に容量素子とスイッチを直列接続した素子を接続する。すなわち、PMOSトランジスタM2のドレインとキャパシタC1の一方の端子を接続する。また、端子VinとキャパシタC1のもう一方の端子にスイッチS1の一方の端子を直列接続し、スイッチS1のもう1方の端子をPMOSトランジスタM2のゲートと接続する。スイッチS1を開閉する事で見かけ上のトランジスタのゲート−ソース間容量を変化させてインダクタンス値を変動させるが、MOSトランジスタM1・M2の相互コンダクタンスは変化せず、そのため出力電流雑音は変らない。

(もっと読む)

半導体装置

【課題】高い精度のインピーダンス調整回路を有する半導体装置を提供する。

【解決手段】可変抵抗回路と外部抵抗素子との分圧電圧と、基準電圧とを比較する差動増幅回路にオフセット調整回路を設ける。オフセット調整回路は、第1と第2オセット調整信号によりそれぞれオン/オフ制御されて上記差動増幅回路の第1と第2負荷抵抗に流れる電流を形成し、それぞれ並列形態にされた複数からなる第2と第3MOSFET群を有する。上記差動増幅回路の両入力に基準電圧を供給した状態にし、上記第2と第3MOSFET群に供給される第1オフセット調整信号による電流を変化させて上記差動増幅回路及びデジタル変換段を通した出力信号が変化した時点での第1オフセット調整信号又は上記第2オフセット調整信号をオフセット調整設定信号とする。

(もっと読む)

周波数可変フィルタ回路

【課題】簡素な回路構成で実現でき、小型化可能な周波数可変フィルタ回路を提供すること。

【解決手段】インダクタ12と可変容量素子14(第2の並列容量素子)とが並列に接続された並列共振回路20と、複数の可変容量素子10、11及び13からなるインピーダンス調製回路21と、2つのエミッタフォロワ回路16、18からなるインピーダンス調整回路22と、を備えて周波数可変フィルタ回路1を構成し、可変容量素子10の容量値と可変容量素子11(及び可変容量素子10と可変容量素子13)の容量値との比を調整することにより、並列共振回路20の入力側のインピーダンスを所望値に調整し、エミッタフォロワ回路16及び18によって並列共振回路20の出力側のインピーダンスを所望値に調整することにより、簡素な構成で小型化可能の周波数可変フィルタ回路を構成した。

(もっと読む)

1 - 20 / 80

[ Back to top ]