Fターム[5J098AD14]の内容

能動素子を用いた回路網 (5,588) | 目的と効果 (843) | 調整可能、制御可能 (185)

Fターム[5J098AD14]の下位に属するFターム

調整の簡素化、容易な調整 (24)

調整精度の向上 (39)

調整幅の拡大 (12)

特性の自動調整 (55)

Fターム[5J098AD14]に分類される特許

1 - 20 / 55

制御回路および位相変調器

可変減衰器

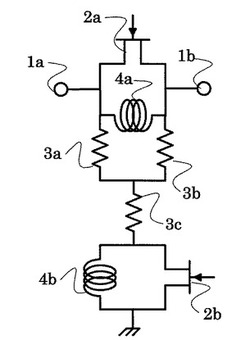

【課題】状態切替時の通過位相差を抑えつつ、回路サイズを小さくすることができる可変減衰器を提供する。

【解決手段】可変減衰器は、第1の入出力端子1aと、第2の入出力端子1bと、第1のスイッチング素子としての第1のFET2aと、第2のスイッチング素子としての第2のFET2bと、第1の抵抗3aと、第2の抵抗3bと、第3の抵抗3cと、第1のインダクタ4aと、第2のインダクタ4bとを有している。第1のインダクタ4aのインダクタンスは、動作周波数において第1のFET2aのオフ容量と共振するような値に予め設定されている。第2のインダクタ4bのインダクタンスは、動作周波数において第2のFET2bのオフ容量6bと共振するような値に予め設定されている。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

フィルタ

【課題】従来に比して格段的に特性のばらつきを小さくすることができるフィルタを提供する。

【解決手段】入力信号Vinの周波数特性を補正して出力するフィルタ部22と、フィルタ部22の特性を制御する制御部23とを備えるようにする。フィルタ部22は、制御電流ICNTにより相互コンダクタンスを可変して入力電圧に応じた電流を出力するトランスコンダクタンス回路24を使用したジャイレータ方式のフィルタ回路であり、制御部23は、制御用のクロック信号CLKを周波数電流変換して制御電流ICNTを生成する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の中心周波数を調整する機能を備えたフィルタ回路を提供する。

【解決手段】入力信号とフィードバック信号(信号Vf)の加算信号を出力するカプラー109、加算信号を増幅した増幅信号を生成するAGC回路110、増幅信号の位相をシフトさせて信号Vfを生成する移相器111を備えたフィルタコア部102と、基準信号(信号Vr)を取得する基準信号生成部119、信号Vr、信号Vfの振幅を比較する振幅比較回路101、比較の結果に基づいてAGC回路110の増幅率を制御するゲイン制御電圧生成部108、信号Vrの位相と信号Vfの位相とを比較する移相比較回路103、比較結果に基づいて移相器111の位相のシフト量を制御する移相器制御電圧生成部117によってフィルタ回路を構成し、増幅率、シフト量が制御される間、カプラー109には信号Vfに代えて基準信号が入力される。

(もっと読む)

可変減衰器

【課題】 従来の可変減衰器では、高周波信号を損失少なく通過させる基準状態と、所望の減衰量を得る減衰状態との間で、通過位相差を生じてしまうという課題があった。

【解決手段】 入出力間FET3と並列、定位相可変減衰器4と直列に位相補正用FET5を設置することで、入出力間FET3がオン状態のときは位相補正用FET5をオフ状態とし、入出力間FET3がオフ状態のときは位相補正用FET5をオン状態とすることによって、基準状態と減衰状態との間で通過位相を等しくすることができる。

(もっと読む)

フィルタ回路

【課題】フィルタ特性の可変幅が細かく且つ範囲が広い場合であっても、回路の増大を抑制できると共に、コストを抑制し得るフィルタ回路を提供する。

【解決手段】フィルタ回路2のフィルタ特性を決定する少なくとも1種の素子3の素子値を、動作クロックCLKに基づきデジタルコード入力Codeをシグマデルタ変調するΣΔ変調器1の出力、或いは該ΣΔ変調器1の出力をコード変換するデコーダ4を介した信号に基づき変化させる。

(もっと読む)

ローパスフィルタ設計

高い品質係数(Q)を有するローパスフィルタリングのための手法。 例示的な実施形態では、入力電流は第1のトランジスタのドレインに接続される。 1のトランジスタのドレインとゲートとは抵抗器R1によって一緒に結合され、そして、ドレインは第1キャパシタC1によって基準電圧に結合される。ゲートは第2のキャパシタC2により、基準圧に結合される。ゲートはさらに第2のトランジスタのゲートに結合され、出力電流が第2のトランジスタのドレインに接続される。別の例示的な実施形態では、さらに受動素子が奇数次のローパス伝達特性を発生するために結合されることができる。 複数のフィルタは、任意のオーダーを有するフィルタを合成するために、直列にカスケード接続することができる。  (もっと読む)

(もっと読む)

フィルタ回路

【課題】フィルタ回路における信号のロスが生じても、通過すべき周波数の信号と他の周波数の信号との十分な強度比が得られるフィルタ回路を提供する。

【解決手段】信号線110に接続され、信号線110を伝搬する信号をフィルタリングするフィルタ回路を、信号線110ラインから信号を入力し、バッファリングするアンプ回路101と、アンプ回路101によってバッファリングされた信号をフィルタリングするノッチフィルタ108と、ノッチフィルタ108から出力された信号を入力し、入力された信号の周波数分布を反転させて信号線110に出力する−gm回路102と、によって構成する。

(もっと読む)

回路公差を調節するための回路と方法

【課題】周波数に敏感な回路のための周波数応答調節器、及び回路の周波数応答を調節する方法を提供する。

【解決手段】周波数に敏感な回路の充電状態を第1の電圧として測定し出力する時定数センサと、第1の電圧をサンプルし、第1の電圧を変換して得られる結果である第2の電圧を出力する変換器と、トリミング要素アレイと、トリミング要素アレイから少なくとも1つのトリミング要素を選択するために第2の電圧を利用するセレクタとを含んでいる。この方法は、回路の時定数を感知することと、この感知を第1の電圧として出力することと、第1の電圧を、固定された間隔にわたってサンプルすることと、サンプルした第1の電圧を、第2の電圧に変換することと、第2の電圧を使ってトリミング要素アレイから、少なくとも1つのトリミング要素を選択する。

(もっと読む)

フィルタユニット及び移動体通信端末試験システム

【課題】移動体通信用の周波数帯域おいて、仕様の追加・変更に柔軟に対応可能な帯域阻止フィルタフィルタを提供する。

【解決手段】それぞれ互いに直列に接続され、かつそれぞれがYIG素子を有して同調周波数を可変可能にされ、それぞれの該同調周波数(f1,f2)を中心とした所定帯域幅(ΔBW1,ΔBW2)内にある所望の信号を減衰させるための、第1の可変フィルタ(102)及び第2の可変フィルタ(103)とを備え、前記所望の信号が低周波数帯域側にある場合、前記同調周波数(f1)と前記同調周波数(f2)とが互いに同一又は近傍に設定するように制御され、高周波数帯域側にある場合、前記所定帯域幅(ΔBW1)と前記所定帯域幅(ΔBW2)とを、いずれか一方の周波数帯域幅より広くなるように連結させかつ連結した帯域が前記所望の信号を包含するように前記同調周波数(f1)及び前記同調周波数(f2)が制御される。

(もっと読む)

可変利得トランスコンダクタンスステージと同調可能な適応フィルタ

例示的な実施形態では、アナログフィルタ(400)を備えている通信デバイスを提供する。所望の値で、または、所望の範囲内でフィルタの極の位置を管理するために、デジタル信号プロセッサ(410)は、アナログフィルタの利得(420、440)と、フィルタの極の位置(430、480)とを同時に設定する。さらなる実施形態では、フィルタの、利得と極の位置とを同時に設定する方法論も与える。 (もっと読む)

可変利得増幅器及びそれを用いた移相器

【課題】 増幅素子の電流特性の非線形性を改善し、振幅設定精度を向上させた可変利得増幅器及びそれを用いた移相器を提供する。

【解決手段】 第2定電流源16からの電流を入力電流とし、この入力電流に比例した電流を第2カレントミラー回路17を介してエミッタ電流とする第7バイポーラトランジスタ18と、この第7バイポーラトランジスタ18の前記エミッタ電流に相応する第7バイポーラトランジスタ18のベース電流を入力電流とし、この入力電流に比例した電流を出力電流として第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれのベースに入力する第3カレントミラー回路20とを備え、第3バイポーラトランジスタ7及び第4バイポーラトランジスタ8のそれぞれの入力電流に対する出力電流を線形とし、第2定電流源16からの電流に比例した利得を可変するようにした。

(もっと読む)

抵抗増倍回路

【課題】チップ面積の増大を招くことなく、半導体材料に起因するhfeのばらつきなどに影響されることのない安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に抵抗器3の一端が接続され、抵抗器3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、抵抗器3の他端に接続されて、信号入力端子8から見た抵抗器3の見かけ上の抵抗値が1/(1+N)倍に見えるものとなっている。

(もっと読む)

フィルタ回路及び通信装置

【課題】電荷の移動に伴う過渡現象が出力に与える影響を抑止すること。

【解決手段】入力端に入力された電圧信号を電流信号に変換するトランスコンダクタンスアンプ102と、複数のキャパシタから構成され、トランスコンダクタンスアンプ102から出力された電流信号が周期毎に各キャパシタへ順次に入力されるキャパシタ集合体と、電流信号が入力された1群のキャパシタを互いに接続し、当該1群のキャパシタに蓄積された電荷を加算するシェアスイッチS1aS〜S4aS,S1bS〜S4bSと、シェアスイッチS1aS〜S4aS,S1bS〜S4bSにより電荷が加算された後、1群のキャパシタのうちの少なくとも1つのキャパシタを出力端に接続するダンプスイッチS1aD〜S4aDと、を備える。

(もっと読む)

寄生容量により誘導される誤差が減少されたセンサデバイス

デバイス110は、駆動ノード34,36および感知ノード42,44を有する感知素子26を備えている。駆動ノード34および感知ノード42との間には寄生容量22が存在する。同様に、駆動ノード36と感知ノード44との間には寄生容量24が存在する。駆動信号56が駆動ノード34、36との間に印加されると、駆動ノード34と感知ノード42との間の寄生電流70および駆動ノード36と感知ノード44との間の寄生電流72が寄生容量22,24のおかげで生成される。容量性ネットワーク112を介して寄生電流70を打ち消す補正電流134を生成するために、駆動ノード36と感知ノード42との間に容量ネットワーク112が接続される。同様に、容量性ネットワーク112を介して寄生電流72を打ち消す補正電流138を生成するために、駆動ノード34と感知ノード44との間に容量性ネットワーク114が接続される。  (もっと読む)

(もっと読む)

フィルタ回路

【課題】入力信号の大きさの広い範囲にあっても良好な線形性を有する高域通過フィルタ及びノッチフィルタを提供する。

【解決手段】 PMOSトランジスタ(Tr)1、Tr1とドレイン同士が接続されるTr2、ドレインがTr1のソースに接続されるTr3、Tr3がTr2のソースに接続されるTr4を有し、Tr3のゲートがTr4のドレインに接続し、Tr4のゲートがTr3のドレインに接続し、Tr3、Tr4のソースに接続される電流源5、6、Tr1、Tr2のソース間に接続されるコンデンサ8、Tr3、Tr4のソース間に接続されるコンデンサ7を含む回路29、Tr1、Tr2のゲートからTr3、Tr4のソースまでの経路において分岐された信号を出力信号に重畳し、回路29によって減衰される周波数帯域と異なる周波数帯域が減衰される信号を生成する回路100とによってフィルタ回路を構成する。

(もっと読む)

フィルタ回路および通信装置

【課題】フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能なフィルタ回路を提供すること。

【解決手段】フライングキャパシタと、フライングキャパシタの入力端と出力端との間に、フライングキャパシタと並列に設けられるキャパシタと、を備えるフィルタ回路は提供される。フライングキャパシタの入力端と出力端との間に所定の容量を有するキャパシタを設けることで、フライングキャパシタを備えるフィルタ回路において、急峻な減衰特性を備えることが可能となる。

(もっと読む)

位相同期回路におけるループフィルタ

【課題】C/Nを改善することができる位相同期回路におけるループフィルタを提供する。

【解決手段】本発明の位相同期回路におけるループフィルタ1は、増幅回路2、第1のローパスフィルタ3、第2のローパスフィルタ4、電圧供給回路17、スイッチング素子5を備える。第2のローパスフィルタ4は、増幅回路2の出力端子2aと第1のローパスフィルタ3との間に接続され、バイアス電圧を供給する電圧供給回路17にも接続される。スイッチング素子5は、第2のローパスフィルタ4の接続状態を制御し、増幅回路2から出力された制御電圧が所定の電圧以下に降下したときに自動的にオンとなるように形成される。

(もっと読む)

フィルタ回路及びフィルタ回路の補正方法

【課題】フィルタ回路で、製造ばらつきに対応して容易に特性周波数のずれを補正すること。

【解決手段】フィルタ回路10はgm値が制御可能なセルと、少なくとも2つのコンデンサを含むフィルタ部11を有し、2つのコンデンサの容量差を検出し、その容量差に応じて生成した制御電圧VCをフィルタ部11のgmセルに供給し、gmセルのコンダクタンス値とコンデンサの容量値との比をそれぞれ等しくする。

(もっと読む)

1 - 20 / 55

[ Back to top ]