Fターム[5J106CC15]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | 基準発振回路 (165)

Fターム[5J106CC15]に分類される特許

1 - 20 / 165

高安定発振器

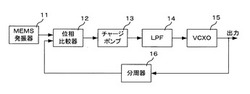

【課題】小型化が容易であり、低コストで製造可能であって、発振出力周波数における短期安定度と長期安定度とを両立させた高安定発振器を提供する。

【解決手段】一定の周波数の信号を出力する高安定発振器は、出力発振器として電圧制御型水晶発振器15を備えるPLL回路と、MEMS振動子を有するMEMS発振器11と、を備える。MEMS発振器11の出力を基準信号としてPLL回路の位相比較器12に供給する。MEMS発振器11によって出力周波数の長期安定度が維持され、電圧制御型水晶発振器15によって出力周波数の短期安定度が維持されるようにする。

(もっと読む)

電子機器

【課題】局所的な温度上昇が発生した場合であっても、温度センサによる補正値と水晶振動子の周波数ドリフトとの追従ができる電子機器を提供する。

【解決手段】温度センサ素子で計測された温度を用いて水晶振動子の振動に対する補正を行う電子機器1は、基板上に配置された水晶振動子13と、温度を計測する温度センサ素子14とを備え、前記主表面のうち前記水晶振動子13で覆われた部分領域の基板内部に前記温度センサ素子14の少なくとも一部が配置される。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号が「断」となった場合には、SW3に可変電圧供給回路12からの出力電圧にループフィルタ4に出力させる切替信号を出力し、更にループフィルタ4からの出力電圧を1/N分圧器13で分圧した電圧を微調制御電圧とし、オフセット電圧供給回路15からの電圧を粗調電圧として加算器14で加算してOCXO5の制御電圧として出力する周波数シンセサイザである。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。更に前記温度検出値に基づいて、OCXOの設定周波数を補正し、雰囲気温度が基準温度からずれたことによる周波数の変動分を補償するようにする。

(もっと読む)

レベル調整装置

【課題】 基準発振器、VCO、位相比較器の純度が低くても位相雑音特性を良好にする。

【解決手段】 基準発振器28aが発振する基準周波数frefをBS放送波のチャンネル間隔とされる38.36MHzに設定する。そして、中間周波数を282.28(=7×38.36+13.76)MHzとした場合は、1049.48MHzのチャンネル周波数とされるBS−1チャンネルがアサインされるBS−IFレベル調整ユニット10では、局部発振器28の出力周波数foutが767.2MHzになり、分周器28eの分周数Nを20とすればよい。基準周波数frefを38.36MHzと高くすることができるため、局部発振器28の位相雑音特性が良好になる。

(もっと読む)

発振器およびPLL回路

【課題】半導体集積回路上に小面積で形成でき、かつ、適切な周波数の発振信号を生成できる発振器と、これを用いたPLL回路を提供する。

【解決手段】発振器は、第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子とを備える。前記半導体素子は、半導体基板と、前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有する。前記第1のノードまたは前記第2のノードから発振信号を出力する。

(もっと読む)

水晶発振器の温度制御装置及び温度制御方法

【課題】風による水晶発振器の出力周波数特性への影響を抑える。

【解決手段】少なくとも恒温槽10と恒温槽10内に設けられた水晶振動子11を内部に有する水晶発振器100と、水晶発振器100の外部に設けられた風速センサー20と、水晶発振器100の外部に設けられた補助ヒーター回路21を有する水晶発振器100の温度制御装置である。風速センサー20により一定値以上の風速を検出したときに、補助ヒーター回路21により水晶発振器100に対して熱を加える。

(もっと読む)

発振器

【課題】PLL回路を有する発振器であって、小型化を図ることができる発振器を提供する。

【解決手段】発振器100は、基板110の上方に配置された第1MEMS振動子12を含み第1発振信号を出力する基準発振回路と、基板110の上方に配置された第2MEMS振動子52を含み制御信号で発振周波数が制御され第2発振信号を出力する電圧制御発振回路と、前記第2発振信号を分周して分周信号を出力する分周回路と、前記分周信号と前記第1発振信号との位相差に基づいた前記制御信号を出力する位相比較回路と、を含み、第1MEMS振動子12および第2MEMS振動子52の各々は、第1電極と、第2電極と、を有し、第2電極は、第1電極と対向配置された可動部を有し、基板の平面視において第1MEMS振動子12の可動部の面積は、第2MEMS振動子52の可動部の面積よりも大きい。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

クロック発生装置及びクロック信号生成方法

【課題】CPUに供給するクロック信号の周波数に関わらず、周辺回路に所定の周波数のクロック信号を供給することができるクロック信号生成回路及びクロック信号生成方法を提供する。

【解決手段】本発明にかかるクロック信号生成回路は、CPUに入力される第1クロック信号から、周辺回路に入力される所定の周波数を有する第2クロック信号を生成する。外部から入力される逓倍比及び分周比のうち少なくとも1に基づき、発振子が出力するクロック信号から入力される第1クロック信号を生成する第1クロック生成部と、第1クロック信号から第2クロックを作成するための基準値を算出する基準値算出部と、第1クロック信号のカウント値と基準値との比較結果に基づき、第2クロックを生成する第2クロック生成部とを有し、基準値算出部は、逓倍比及び分周比のうち少なくとも1つが変更され第1のクロック信号の周波数が変更されると、基準値を再度算出する。

(もっと読む)

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

多周波発振器

【課題】発振周波数の安定性及び周波数の過渡応答性において従来よりも優れた多周波発振器を提供する。

【解決手段】水晶振動子を少なくとも備え、変調信号発生器5から入力された変調信号によって水晶振動子の発振周波数を調整する基準信号発生器12と、位相比較器6、ループフィルタ7及び電圧制御発振器8を少なくとも備え、基準信号発生器11の出力と電圧制御発振器8の出力とを位相比較器6で位相比較するPLL11とを具備する。

(もっと読む)

原子発振器および原子発振器の製造方法

【課題】 優れた特性を発揮することのできる原子発振器および原子発振器の製造方法を提供すること。

【解決手段】原子発振器1は、ガス状の金属原子を封入したガスセル3が収納された第1パッケージ21と、ガスセル3中の金属原子を励起する励起光LLを出射する光出射部6が収納された第2パッケージ22と、少なくとも1つの光学部品8が設けられた第3パッケージ23とを有している。また、第2パッケージ22の一方側に第3パッケージ23が固定され、第3パッケージ23の第2パッケージ22と反対側に第1パッケージ21が固定されている。光出射部6から出射した励起光LLが、光学部品8を通過したのちガスセル3内に入射するよう構成されている。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュールであって、所定の波長を有する基本波F、当該基本波Fの側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光L1が入射し、当該入射した光L1のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、波長選択部20は、ファイバーブラッググレーティング20aと、ファイバーブラッググレーティング20aに電圧を印加する電圧印加部20bと、を有する。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュールであって、所定の波長を有する基本波F、当該基本波Fの側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光L1が入射し、当該入射した光L1のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、

波長選択部20は、ファイバーブラッググレーティング20aと、ファイバーブラッググレーティングの温度を制御する温度制御部20bと、を有する。

(もっと読む)

発振装置

【課題】環境温度の検出結果に基づいて出力周波数を補正する発振装置において、出力周波数の温度補償を高精度に行うこと。

【解決手段】共通の水晶片により第1及び第2の水晶振動子を構成すると共に、これら水晶振動子に夫々接続される第1及び第2の発振回路の発振出力をf1、f2とし、基準温度における第1及び第2の発振回路の発振周波数を夫々f1r、f2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分である周波数差をそのときの温度として取り扱う。そしてこの周波数差に基づいて多項式近似により周波数補正値を求める。

(もっと読む)

GPSジッタ低減装置

【課題】後段側の装置を軽量に設計することのできるGPSジッタ低減装置を得る。

【解決手段】位相比較調整処理部105は、GPS11が出力する1PPSと、出力パルス生成部104から出力される平滑化された1PPSとの位相差をカウントし、位相差目標値と比較して、固定値にて調整を実施する。出力パルス生成部104は、移動平均処理部103の出力と、位相比較調整処理部105の調整値に基づいて平滑化した1PPSを生成する。

(もっと読む)

同期回路

【課題】基準信号に異常が発生した場合でも大きな位相ずれ量が発生しない同期信号(タイミング信号)を出力する同期回路を提供する。

【解決手段】同期回路1は、発振器クロック信号を発生する電圧制御発振器16と、第1の基準クロック信号及び第2の基準クロック信号を含む複数の基準クロック信号と前記発振器クロック信号との間のそれぞれの位相ずれ量を検出する位相ずれ量検出部12と、前記複数の基準クロック信号の状態に応じた制御信号に基づいて同期信号を出力する同期信号処理部13,14と、前記同期信号と前記発振器クロック信号との間の位相ずれ量に応じて電圧制御発振器16のコントロール電圧を生成するコントロール電圧生成部15とを備える。

(もっと読む)

1 - 20 / 165

[ Back to top ]