Fターム[5J106DD37]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | コード変換器 (37)

Fターム[5J106DD37]に分類される特許

1 - 20 / 37

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

分周回路およびそれを備えたPLL回路並びに半導体集積回路

【課題】回路規模および消費電力を増大させることなく、回路全体の分周比の可変範囲をより拡大することのできる分周回路を実現する。

【解決手段】周期信号(s5)を2種類の分周比で分周して第1の分周信号(c1)を出力する可変分周器(2)と、第1の分周信号(c1)のサイクル数のカウント値(c2)を出力し、リセットされるとカウント動作を初期値から再開するカウンタ回路(3)と、カウント値(c2)が比較基準値(a)と一致する度にHighとLowとを反転させたパルス信号(s1)を、第2の分周信号として出力するとともに分周比の切替信号として可変分周器(2)に供給し、カウント値(c2)が比較基準値(a)と一致する度にカウンタ回路(3)にリセット信号(r)を出力する比較器(4)と、比較器(4)に比較基準値(a)を供給する制御回路(5)とを備えている。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

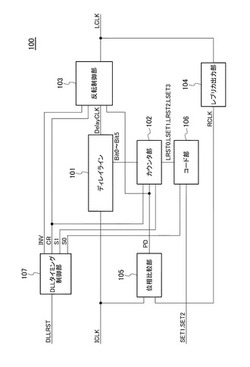

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

半導体装置

【課題】出力ドライバのスイング能力を変化させた場合に生じるリードデータのスキューをキャンセルする。

【解決手段】リードデータDQを外部に出力する出力ドライバ90と、出力ドライバ90のスイング能力を設定するモードレジスタ53とを備える。出力ドライバ90によって駆動されるリードデータDQの遷移開始タイミングは、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に大きく設定されている場合には相対的に早められ、モードレジスタ53に設定された出力ドライバ90のスイング能力が相対的に小さく設定されている場合には相対的に遅らせる。これにより、出力ドライバ90のスイング能力に関わらず、リードデータDQがしきい値レベルを超えるタイミングを所望のタイミングに一致させることが可能となる。

(もっと読む)

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

デジタル制御発振器

【課題】TDCに関する冗長構成を削減可能なDCOを提供する。

【解決手段】DCOは、デジタル制御信号によって遅延量が制御される3以上の奇数個の単相インバータ101〜105を環状に接続したリングオシレータと、単相インバータの各々の出力信号をバッファリングし、第1の差動信号として夫々出力する奇数個のバッファ111〜115と、基準信号の立ち上がりエッジまたは立ち下がりエッジにおける第1の差動信号の値を保持して第2の差動信号として夫々出力する奇数個のフリップフロップ121〜125と、奇数個のフリップフロップから出力される奇数組の第2の差動信号を入力し、奇数組の第2の差動信号を位相の進み順に配列したときの、連続する高レベル値または連続する低レベル値の末尾を示す情報を出力するエッジ検出器130とを具備する。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

改善された分解能を有する時間デジタル変換器(TDC:TIME−TO−DIGITALCONVERTER)

【解決手段】一つのインバータ遅延より小さいインバータ遅延の高分解能を含む時間デジタル変換器(TDC)が記載されている。デザイン例において、TDCは、第1及び第2の遅延パス、遅延ユニット、及び位相演算ユニットを含んでいる。第1の遅延パスは、第1の入力信号及び第1の参照信号を受信し、第1の出力を供給する。第2の遅延パスは、第2の入力信号及び第2の参照信号を受信し、第2の出力を供給する。遅延ユニットは、例えば半分のインバータ遅延によって、第1の入力信号に対して第2の入力信号を遅延する、または第1の参照信号に対して第2の参照信号を遅延する。位相演算ユニットは、第1及び第2の出力を受信し、入力信号及び参照信号間の位相差を供給する。構成は、前記第1及び第2の遅延パスについての正確なタイミングを得るために実行され得る。 (もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

デジタル位相ロック・ループ(DPLL)、デジタル位相ロック・ループ(DPLL)内のジッタを制御するための方法、デジタル制御発振器(DCO)内のディザを最適化するための方法、および自己ディザリング・デジタル制御発振器(DCO)回路

【課題】 デジタル位相ロック・ループ(DPLL)および方法を提供する。

【解決手段】 デジタル位相ロック・ループ(DPLL)および方法は、入力として基準クロックを受け取り、ディザリングした基準クロック信号を出力するように構成された調整可能遅延線を含む。位相周波数検出器(PFD)は、ディザリングした基準クロック信号をフィードバック・クロック信号と比較して、ディザリングした基準クロック信号とフィードバック・クロック信号との位相および周波数の差を決定するように構成される。デジタル制御発振器(DCO)は、PFDから早遅判断を受け取り、それに応じて出力を調整するように構成され、ディザリングした基準クロック信号はDPLLの全体的な動作を強化するためにジッタ応答を分散する。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

遅延クロック発生装置

【課題】多数段の遅延ステップで遅延時間を選択可能としながら、遅延ステップの直線性を確保し得る遅延クロック発生装置を提供する。

【解決手段】複数種類の遅延クロック信号を発生させる遅延クロック発生装置において、平行して配置された複数列の遅延素子列16a〜16dと、遅延素子列を構成する各遅延素子に設けられ、クロック信号CLKを往復方向に転送する往路側及び復路側転送線と、各遅延素子にそれぞれ設けられ、前後に連なる遅延素子の往路側転送線同士と復路側転送線同士を接続する第一の転送経路と、各遅延素子の往路側転送線と復路側転送線とを接続する第二の転送経路を選択する選択回路と、入力コードicodeに基づいて遅延素子列のいずれか一つの遅延素子でのみ選択回路で第二の転送経路を選択させるデコーダー12,13,14を備えた。

(もっと読む)

ループ設定調整回路

【課題】ループ回路において、フィードバック遅延やPVT変動を自動的に検出して、ループ設定を調整し最適化することができるループ設定調整回路を提供する。

【解決手段】ループ設定調整回路は、クロックツリーシンセシスがフィードバック経路に挿入されたループ回路のループ特性を決定するループ設定を調整する。ループ設定調整回路は、クロックツリーシンセシスによる遅延時間を検出する検出回路と、検出回路によって検出される遅延時間に相当する時間、遅延時間よりも短い周期の発振クロックを出力する発振回路と、発振回路から出力される発振クロックのクロック数をカウントし、カウント値に対応する制御信号を出力する制御回路とを有し、制御回路から出力される制御信号により、クロックツリーシンセシスによる遅延時間に応じて、ループ設定を調整する。

(もっと読む)

位相補間制御装置

【課題】位相補間制御装置中のノイズフィルタ帯域幅を動的に調整し、位相補間制御装置を広く応用することができる上、CDRのロック時間を短縮させることができる位相補間制御装置を提供する。

【解決手段】位相補間制御装置400は、第1の信号と第2の信号との位相関係を表す指示を受信し、複数の双方向シフトレジスタを含む。複数の双方向シフトレジスタは、互いに直列接続され、位相補間制御装置が受信した指示が、第1の信号の位相が第2の信号の位相より進んでいることを表すとき、直列接続された複数の双方向シフトレジスタをそのうちの1方向でシフトさせる。位相補間制御装置400が受信した指示が、第1の信号の位相が第2の信号の位相より遅れていることを表すとき、直列接続された複数の双方向シフトレジスタを他の方向でシフトさせる。

(もっと読む)

1 - 20 / 37

[ Back to top ]