Fターム[5J106JJ01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | 発振回路、VCO (253)

Fターム[5J106JJ01]に分類される特許

41 - 60 / 253

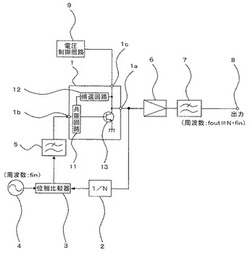

位相同期発振装置

【課題】 小さいばらつきで電圧制御回路から供給される温度補償された電圧によって制御される電圧制御発振器を介して接続された増幅器の出力電力を、精度良く増減させ出力端子から出力する位相同期発振装置を得る。

【解決手段】 発振周波数を制御する周波数制御電圧入力端子と発振電力を制御する電圧入力端子とを有する電圧制御発振器と、この電圧制御発振器から出力される高周波信号を増幅して出力する温度特性を有する増幅器と、温度センサを有し、この温度センサの出力信号で基準電圧から変化する電圧を前記電圧制御発振器の電圧入力端子に入力し、前記電圧制御発振器を介して前記増幅器の電力非飽和領域の電力を増減する電圧制御回路とを備えている。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

ジッタ除去回路

【課題】従来では、基準クロック生成回路が生成するクロックにジッタが発生するという問題があった。

【解決手段】本発明にかかるジッタ除去回路は、基準クロック51のジッタを除去するジッタ除去回路であって、サンプリングクロック52に同期して基準クロック51のエッジを検出するラッチ回路12と、基準クロック51のエッジ間隔をカウントするカウンタ13と、各エッジ間隔のカウント数に基づいて基準クロック51の位相を調整する位相調整回路14と、を備える。

(もっと読む)

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

原子発振器の製造方法

【課題】製造工程を短縮してユニットコストの低減を図ることができる原子発振器の製造

方法を提供する。

【解決手段】この原子発振器50は、半導体基板上に形成された受光部を有する受光素子

(PD)6と、受光素子6上に積層され、受光部の上部に開口部8aを有する空洞8bが

形成されたセル層8と、空洞8bに封入された気体状のアルカリ金属原子5と、開口部8

aを閉止するカバーガラス(透明部材)4と、カバーガラス4を介してアルカリ金属原子

5に共鳴光を出射する発光素子(VCSEL)1と、を備えて構成されている。尚、受光

素子(PD)6には電極7が備えられ、カバーガラス4上には発光素子1用の電極3が形

成されている。そして発光素子1のバンプ2を介して発光素子1用の電極3と接続される

。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

発振回路

【課題】 起動直後から安定した振動波形を有する出力信号を得ることができる発振回路を提供する。

【解決手段】 発振回路1Aは、入力電圧に基づいて振動波形を有する振動出力電圧を出力する主発振回路2Aと、主発振回路2Aの振動出力電圧に応じた出力信号と予め定められた周波数を有するクロック同期信号SYNCとが入力され、出力信号及びクロック同期信号SYNCの位相差に応じた電圧を出力する位相比較器3と、位相比較器3の出力電圧を平滑化する第1ローパスフィルタ4と、第1ローパスフィルタ4の出力電圧が基準電圧Vref1以上の場合、第1ローパスフィルタ4の出力電圧を主発振回路2Aに入力し、第1ローパスフィルタ4の出力電圧が基準電圧Vref1より低い場合、基準電圧Vref1を主発振回路2Aに入力する切替回路5Aとを備えている。

(もっと読む)

双方向無線通信システム、無線通信装置及び双方向無線通信方法

【課題】PLL回路を含んだ回路に比べて周波数同期回路等を簡単な回路によって構成できるようにする。

【解決手段】入力信号を変調した変調信号に所定の搬送周波数の基準搬送信号を重畳して送信信号を送信する双方向用のTRX1と、通信許可信号を生成するTRX2とを備える。TRX2は自走発振周波数の信号を発振する発振器を有している。TRX2は、TRX1から受信した受信信号を発振器23に注入する。これと共に、発振器23の自走発振周波数を可変制御しながら受信信号を受信し、発振器23の信号の自走発振周波数が注入同期に至る周波数範囲に入って注入した受信信号の搬送周波数に周波数同期したか否かを検出する。TRX2は、発振器23の信号の自走発振周波数が、注入した受信信号の搬送周波数に周波数同期したことを検出したときに、通信許可信号をTRX1に送信するものである。

(もっと読む)

通信ネットワークにおける使用のための発振器、周波数シンセサイザ及びネットワークノード

本開示は、周波数シンセサイザ内での周波数の生成における使用のための発振器であって、少なくとも1つの巻きを伴って金属線ループを形成する第1の誘導素子と、前記第1の誘導素子との間で第1の共振回路を形成するように構成され、少なくとも1つの第1の接続端子を通じて前記第1の誘導素子と接続される第1の容量回路と、を備え、前記第1の容量回路は、少なくとも1つの容量素子、並びに、発振を確立し及び維持するように構成される電子コンポーネント配置を含む、発振器に関する。当該発振器は、少なくとも1つの容量素子と電子コンポーネントの配置とを含む第2の容量回路が、前記第1の誘導素子との間で第2の共振回路を形成するように構成され、前記第1の容量回路の前記第1の接続端子に対して前記第1の誘導素子の反対側に位置する少なくとも1つの第2の接続端子を通じて前記第1の誘導素子と接続されることと、前記第1及び第2の共振回路が実質的に同等の周波数にチューニングされることと、を特徴とする。本発明は、周波数シンセサイザ及び通信ネットワーク内での使用のためのネットワークノードにも関する。 (もっと読む)

原子発振器及び原子発振器の制御方法

【課題】最大強度のEIT信号が検出でき、S/Nを向上して周波数の安定化を図ること

ができる原子発振器を提供する。

【解決手段】この原子発振器100は、アルカリ金属原子に電磁誘起透過現象(EIT現

象)を発生させるための共鳴光対を生成する光源1と、光源1からの光の波長により光の

吸収量を変化させるアルカリ金属入りセル2と、光源1に高周波信号を供給して共鳴光対

を生成するサイドバンド発生手段5と、光源1に直流信号を供給して共鳴光対の中心周波

数を可変する中心波長可変手段4と、アルカリ金属原子を透過した共鳴光対を検出し、透

過した共鳴光対の強度に応じた検出信号を出力する光検出手段3と、共鳴光対の中心周波

数を可変したときの検出信号の最小値を検出する吸収検出手段6と、サイドバンド発生手

段5から出力される高周波信号の供給又は停止を制御する信号処理手段8と、を備えて構

成されている。

(もっと読む)

PLL回路

【課題】 エージング特性を自動補正し、外部基準信号の未接続又はアンロック時に出力周波数変動を小さくできるPLL回路を提供する。

【解決手段】 基準信号が適正範囲内でロック状態の場合に、初期調整時に、チャージポンプ出力電圧(A)の初期電圧を温度情報Tと共に読み取り、自走周波数設定用電圧(B)が電圧(A)となるようのDAコンバータ又はPWM出力回路9の設定値を調整し、温度特性初期テーブルを生成し、運用中に、温度情報Tにおける電圧(A)の最新電圧に対応する設定値を、温度特性初期テーブルを参照して特定し、初期電圧と最新電圧の設定値の差分で当該テーブルをオフセット補正して自走用温度補正テーブルを生成し、アンロック状態等になると特定された設定値による自走周波数設定用電圧(B)で自走するPLL回路である。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

クロック信号分配装置

【課題】高品質のクロック信号を分配することができるクロック信号分配装置を提供することを課題とする。

【解決手段】第1のインダクタ及び第1の容量に応じた周波数で共振して信号を発振する複数のLC共振発振器(302,303)と、第2のインダクタ及び第2の容量に応じた周波数で共振し、入力クロック信号に同期した信号を発振する注入同期型LC共振発振器(301)と、前記複数のLC共振発振器及び前記注入同期型LC共振発振器の発振ノードを接続する伝送線路(311,312)とを有することを特徴とするクロック信号分配装置が提供される。

(もっと読む)

PLL装置及び不要周波数回避方法

【課題】PLL装置において、不要周波数の影響を、無線性能に影響を与えることなく回避できるようにする。

【解決手段】電圧制御発振器3、4と、基準信号に基づく第1信号及び電圧制御発振器の出力信号に基づく第2信号の両位相を比較し、位相差を示す位相差信号を出力する位相比較器1と、位相差信号に基づき、両位相を同期させる制御電圧を電圧制御発振器に印加するループフィルタ2とを備え、所定の目的周波数を得るPLL装置において、目的周波数を中心とする所定の周波数範囲内に不要周波数が存在する場合に、不要周波数を該周波数範囲外のものとするために基準信号の周波数を変更する基準周波数変更手段5と、基準信号の周波数の変更にも拘わらず目的周波数の出力が維持されるように、第1信号又は第2信号を生成する際の分周比を変更する分周比変更手段5とを設ける。

(もっと読む)

PLL周波数シンセサイザ

【課題】電圧制御発振器のゲイン特性の変動を抑制する。

【解決手段】電圧制御発振器11は、インダクタ100と、微調整コンデンサ101pと、粗調整コンデンサ102pとを含み、発振クロックCKoutを生成する。分周器12は、発振クロックCKoutを分周して分周クロックCKdivを生成する。直流電圧供給回路13は、粗調整モードにおいて、直流電圧V13を制御ノードNiに供給するとともに発振電圧VPの直流値に応じて直流電圧V13の電圧値を変化させる。周波数帯域選択回路14は、粗調整モードにおいて、電圧制御発振器11の発振周波数帯域が目標周波数に対応する発振周波数帯域に設定されるように、基準クロックと分周クロックとの周波数差に基づいて粗調整コンデンサ102pの容量値を切り替える。発振制御回路15は、微調整モードにおいて、基準クロックと分周クロックとの位相差に応じて制御電圧VTを増減させる。

(もっと読む)

温度安定化された電圧制御発振器

【課題】温度安定化された電圧制御発振器を提供する。

【解決手段】セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a、310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370、380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b、320a、320bを含んでいる。

(もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】再生クロックを出力する第1の発振回路と、第1の発振回路と同一周波数のクロックを出力する第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Cを入力する端子と、周波数制御信号Aと回路間ばらつき調整信号Cを加算する加算器とを備え、第1〜第2の発振回路はそれぞれ1つの制御端子を備え、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に加算器の出力信号を入力する構成とする。

(もっと読む)

クロックデータ再生回路

【課題】プロセスばらつきによる発信周波数ずれを調整する。

【解決手段】入力データと周波数および位相が同期した再生クロックを出力する発振回路と、発振回路が出力する再生クロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、発振回路のプロセスばらつきによる発振周波数のずれを調整するプロセスばらつき調整信号Bを入力する端子を備え、発振回路は2つの制御端子を備え、その一方の制御端子に周波数制御信号Aを入力し、他方の制御端子にプロセスばらつき調整信号Bを入力する構成である。

(もっと読む)

41 - 60 / 253

[ Back to top ]