Fターム[5J106JJ01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | 発振回路、VCO (253)

Fターム[5J106JJ01]に分類される特許

121 - 140 / 253

発振回路

【課題】高精度な発振回路を提供する。

【解決手段】例えば、奇数段のインバータ回路IVを含んだ複数のリングオシレータ部RO1,RO2と、このRO1,RO2の出力ノードRO_O1,RO_O2の信号を加算する加算部ADDを設ける。そして、このADDの加算結果をクロック信号として出力ノードOSC_Oから出力すると共に、この出力ノードOSC_OをRO1,RO2の入力ノードRO_I1,RO_I2に帰還する。これによって、例えばRO1,RO2の遅延時間がそれぞれ標準偏差σの正規分布に基づいてばらつく場合に、OSC_Oから得られるクロック信号のばらつきをσ/√2とすることが可能となる。

(もっと読む)

デジタル制御発振回路、周波数シンセサイザ、それを用いた無線通信機器及びその制御方法

【課題】周波数が直線的に変化する範囲が広く且つ占有面積が小さいデジタル発振回路を実現できるようにする。

【解決手段】デジタル制御発振回路10は、複数の第1の可変容量素子からなる第1の容量素子群14及び複数の第2の可変容量素子からなる第2の容量素子群14を含む可変容量部12を有し、可変容量部12の容量値に対応した発振周波数の信号を生成する発振部を備えている。第1の可変容量素子の第1の容量変化量は、第2の可変容量素子の第2の容量変化量に2以上の整数値を乗じた値であり、第2の可変容量素子の個数は、2以上の整数値から1を減じた値以上である

(もっと読む)

発振周波数制御方法及び発振器

【課題】温度によって変化する発振周波数を、応答性良く、正確に、所定の周波数に調整することができる発振周波数の制御方法及び発振器を提供する。

【解決手段】本発明の発振周波数制御方法は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器の発振周波数制御方法であって、振幅を測定する工程と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する工程を備える。また、本発明の発振器は、発振周波数及び出力信号の振幅が温度に依存して変化し、所定の発振周波数制御信号を用いて発振周波数の変更が可能な発振器であって、振幅を測定する振幅測定部と、振幅に基づき発振周波数制御信号を制御し、発振周波数を変更する温度補償部を備える。

(もっと読む)

電圧制御発振器及びこれを用いた位相同期回路

【課題】インバータセルを構成するMOSトランジスタが飽和領域のみならず、線形領域で動作する場合にも位相雑音を低減する。

【解決手段】ダミーインバータセル110からの信号と、基準信号との電位差を増幅した増幅信号を出力する演算増幅器120と;第2MOSトランジスタ102に接続され、増幅信号を受ける第1MOSトランジスタ101と、インバータ入力部及びインバータ出力部として機能する第2MOSトランジスタ102及び第3MOSトランジスタ103と、第3MOSトランジスタ103に接続され、発振信号の周波数を制御するための制御信号を受ける第4MOSトランジスタ104とを含むインバータセル100を環状に接続したリング・オシレータと;インバータセル100と同一の構造を備え、インバータ出力部がインバータ入力部に短絡されたダミーインバータ110と;を具備する。

(もっと読む)

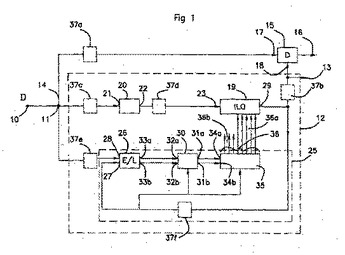

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

PLL回路の電圧制御発振器における漏洩電流を補償する回路構成

【課題】PLL回路の電圧制御発振器内の漏洩電流を補償する回路構成を得る。

【解決手段】ループフィルタ(20)により発振器へ加えられる制御電圧は、基準信号と電圧制御発振器(12)の出力信号との位相差の関数として位相検出器(16)により発生される。発振器(12)は、制御線(34)を介して制御電圧が加えられるバリキャップダイオード(28,30)を含み、同じ構成のバリキャップダイオード(36,38)を有する補償回路(K)が一方の出力(44)において制御電圧を再生して補償回路(K)内のバリキャップダイオード(36,38)へ加え他方の出力(46)からはバリキャップダイオード(36,38)の漏洩電流に等しい電流を供給する。電流分路分岐が制御線(34)から延びており、それを介して演算増幅器(40)により供給される電流に対応する電流が制御線(34)から流れる。

(もっと読む)

ガスセル型原子発振器

【課題】 原子発振器の出力する安定な周波数の信号を使う場所が離れている場合に、その信号を長い同軸ケーブルで搬送していた。外部環境が同軸ケーブルに影響して発生する信号の周波数の揺らぎを削減する。

【解決手段】金属原子に対する励起光を出力する光源部1を設置する。その場所から離れて設置された原子共鳴部30には、該光源部1からの出射光を伝播させる光ファイバ33,34から出射される励起光と共鳴マイクロ波とを入力する。原子共鳴部30は、光マイクロ波二重共鳴を起し、その際に生じる共鳴周波数を出力する。

(もっと読む)

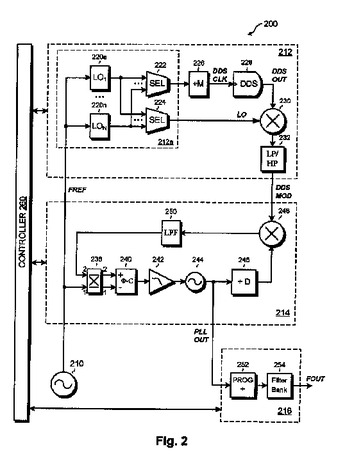

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

CDR回路

【課題】再生データに含まれるジッタを簡易且つ正確にモニタ可能にする。

【解決手段】入力データDinを入力して第1再生クロックCLK1を出力する第1クロック再生部10と、前記入力データDinと前記第1再生クロックCLK1を入力して再生データDoutを出力するデータ再生部20と、前記再生データDoutを入力して第2再生クロックCLK2を出力する第2クロック再生部30と、前記第2再生クロックCLK2を入力してジッタ量を検出するジッタ検出部とを備える。ジッタ検出部は、ゲーティング回路40、積分回路50およびジッタ算出回路60からなる。

(もっと読む)

高周波発振回路、位相同期ループ回路、半導体装置及び通信装置

【課題】より大きなQのインダクタを必要とせず、従来技術に比較してより小さいサイズでかつより高い発振周波数で発振させることができる高周波発振回路を提供する。

【解決手段】帰還型高周波発振回路は、短絡スタブ用伝送線路に接続されたゲートと、発振出力端子に接続されたドレインとを有する電界効果トランジスタ1と、電界効果トランジスタ1のソースに接続されたドレインを有するソース接地の電界効果トランジスタ2とを含み構成され、短絡スタブ用伝送線路11及び電界効果トランジスタ2を帰還回路として発振する。また、電界効果トランジスタ2のゲートと、電界効果トランジスタ1のドレインとの間に帰還用キャパシタを接続する。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】より容易に広い制御電位の範囲にわたって発振周波数の線形性が高い電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路、n個の可変容量回路、及び負性抵抗回路と、電源電位からn個の基準電位を生成する基準電位発生部114とを備える。n個の可変容量回路の可変容量素子の一方端子には、n個の基準電位のいずれかがそれぞれ入力される。n個の可変容量回路の可変容量素子の他方端子には、発振周波数をフィードバック制御するための制御電位Vtが共通入力される。そして、第1〜第3の可変容量回路A〜Cの一方端子には、第1〜第3の基準電位Vref1〜3がそれぞれ入力される。この第1〜第3の基準電位Vref1〜3はそれぞれ固定で、かつ、第1の基準電位Vref1と第2の基準電位Vref2の電位差と、第2の基準電位Vref2と第3の基準電位Vref3との電位差が異なっている。

(もっと読む)

可変遅延回路、可変遅延装置およびVCO回路

【課題】入力信号に対して小さな遅延時間の制御を行うことができる可変遅延回路、可変遅延装置及びVCO回路を提供する。

【解決手段】可変遅延回路は、入力信号を遅延させるトランスファゲートTG1およびトランスファゲートTG3と、トランスファゲートTG1およびトランスファゲートTG3と入力信号との間に設けられるトランスファゲートTG2およびトランスファゲートTG4と、を備えている。

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

位相調整回路および位相調整方法

【課題】 VCOの出力に生じている周波数変動を動的に補正し、これによりロングタームジッタを削減することが可能な位相調整回路の提供。

【解決手段】 周波数比較部12において、基準クロックRIN1の分周クロックREF1の周波数とフィードバッククロックFIN1の分周クロックFB1の周波数を測定および比較し、位相調整部13において、周波数比較部12の比較結果により、FB1の周波数がREF1より高ければカウンタ13−1をカウントアップして可変遅延回路13−2の遅延量を増やし、FB1の周波数がREF1より低ければカウンタ13−1をカウントダウンして可変遅延回路13−2の遅延量を減らす。

(もっと読む)

移動無線機

【課題】基地局を介した通信と、基地局を介さずに直接、他の移動無線機と通信をおこなう二つのモードにより通信する移動無線機において、直接通信のときであっても、環境の温度変化や発信器の経年変化によらず、安定して送信周波数を生成する

【解決手段】基地局の圏内で通信では、AFC部は、受信周波数に基づいて、電圧制御発信器に印加する電圧制御値を調整する。中央処理装置は、その電圧制御値と温度センサーによって検知される温度を対にしてメモリに記憶する。基地局の圏外で他の無線機と通信するときには、中央処理装置は、メモリに記憶された電圧制御値と温度センサーのデータと、現在検知されている温度により、最適な電圧制御値を計算し、その電圧制御値に従って電圧制御発信器に制御電圧を印加して、基準周波数を生成し、それによる送信周波数により、他の移動無線機と通信する。

(もっと読む)

クロック再生装置

【課題】安定した高速動作が可能なクロック再生装置を提供する。

【解決手段】クロック再生装置1は、受信データD1からデータ受信用の再生クロックCK1を得るものであって、受信データD1のレベルが所定のレベルである場合に、受信データD1に同期した所定周波数の信号S1を出力する発振器21と、発振器21に直列に接続され、信号S1のレベルが所定のレベルである場合に、信号S1に同期した所定周波数の信号S1を再生クロックCK1として出力する発振器22とを備える。

(もっと読む)

位相同期回路

【課題】キャリブレーションを高速化する。

【解決手段】VCO16は、入力された制御電圧Vcntに応じた周波数foscで発振し、ある制御電圧Vcntに対する発振周波数foscを可変とするための調節用キャパシタ50a、50bを含む。分周器18は、VCO16の出力信号OUTを、所定の基準クロックREFの周波数と一致するように分周する。位相比較部2は、分周器18の出力信号OUT2と、基準クロックREFの位相を比較し、位相差に応じた電圧を制御電圧VcntとしてVCO16に出力する。容量調節部30は、所定のキャリブレーション期間中に、周波数がロック状態した状態で、制御電圧Vcntが所定の電圧範囲に含まれるように、調節用キャパシタ50の容量値を調節する。ループ制御部40は、キャリブレーション期間中と、通常動作期間中とで、当該位相同期回路100のループ特性を変化させる。

(もっと読む)

周波数合成回路、通信装置、周波数制御方法、周波数制御回路、周波数制御システム、およびコンピュータ読取可能な記録媒体

【課題】周波数合成器(200)の可変発振器(202)の出力信号の周波数を制御するシステムを提供する。

【解決手段】可変発振器(202)と周波数制御回路(208)を有する。可変発振器(202)は予め定められた周波数を有する出力信号を生成するために構成される。また可変発振器(202)は周波数制御回路(208)によって制御される複数の動作状態によって構成される。可変発振器(202)の動作状態のそれぞれは、可変発振器(202)の出力信号のための別個の周波数を決定する。周波数制御回路(208)は、可変発振器(202)の出力信号を受信し、予め定められた周波数に最も近い出力信号のための別個の周波数を決定する。また、周波数制御回路(208)は、可変発振器(202)へ、予め定められた周波数に最も近い別個の周波数に対応する動作状態へ、可変発振器(202)を移行するために構成される制御信号を供給する。

(もっと読む)

PLL回路

【課題】低電源電圧で高速動作すると共に温度及びプロセス条件の変動の影響を受けにくいPLL回路を提供する。

【解決手段】位相比較器101は、入力される基準クロック信号及び帰還される発振信号の位相を相互に比較した結果に基づいて上昇信号または下降信号を出力する。チャージポンプ102は、入力される信号に応じた大きさの制御電圧を出力する。ループフィルタ103は、入力される制御電圧をフィルタリングする。電圧制御発振器100は、負電圧発生回路105から基準電圧として入力される接地電圧よりも低い電圧と、ループフィルタ103から出力される電圧とに応じた発振周波数の発振信号を出力する。

(もっと読む)

121 - 140 / 253

[ Back to top ]