Fターム[5J106JJ01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | 発振回路、VCO (253)

Fターム[5J106JJ01]に分類される特許

81 - 100 / 253

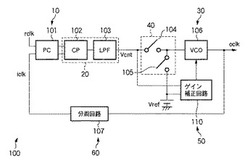

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部と、を有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記生成部から出力された前記制御電圧と前記参照電圧とを比較し、前記生成部から出力される制御電圧が前記参照電圧に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

オシレータ及びオシレーティング信号を生成する方法

【課題】位相同期ループクロック発生器等に好適に使用できるオシレータ及びオシレーティング信号を生成する方法を提供する。

【解決手段】オシレータであって、第1スターブドインバータ(current−starved inverter)と、前記第1スターブドインバータの内部インバータとクロスカップルされる内部インバータを含む第2スターブドインバータと、前記第1スターブドインバータの内部インバータの出力と接続される第1インバータと、前記第2スターブドインバータの内部インバータの出力と接続される第2インバータとを具備し、前記第1インバータの出力は、前記第2スターブドインバータの外部インバータの入力に供給され、前記第2インバータの出力は、前記第1スターブドインバータの外部インバータの入力に供給されることを特徴とする。

(もっと読む)

PLL回路および通信用半導体集積回路装置

【課題】スプリアス特性の向上が実現可能なPLL回路およびそれを搭載した通信用半導体集積回路装置を提供する。

【解決手段】例えば、PLL回路を含む高周波ICチップRF_CP3において、PLL回路内に複数の電圧制御発振回路ブロックVCO_BK1〜VCO_BK3を設ける。そして、ループフィルタの一部となる2次のループフィルタFLT_Aを位相検出等を行うシンセサイザブロックSYNに配置し、他の一部となる1次のループフィルタFLT_BをVCO_BK1〜VCO_BK3のそれぞれに配置する。さらに、VCO_BK1〜VCO_BK3のそれぞれにおいては、インダクタL1,L2をRF_CP3の内側でなく外側(外周の一辺)に近くなるような向きにレイアウトする。

(もっと読む)

位相同期ループ回路

【課題】出力周波数レンジの広いPLL回路を提供すること。

【解決手段】本発明の一態様は、入力パルス信号と出力側からフィードバックされたフィードバックパルス信号との位相差に基づいて生成された電圧を、制御電流Icへ変換する電圧電流変換回路104と、制御電流Icに応じた周波数のパルス信号を生成する電流制御発振器105と、制御電流Icを検出する電流検出部108と、検出された前記制御電流に基づいて、電流制御発振器105から発振される出力パルス信号の周波数レンジを切り替える周波数レンジ切替回路106と、を備えた位相同期ループ回路である。

(もっと読む)

正確で安定したLC型基準発振器のための方法、システム、および装置

【課題】周波数の安定性およびジッタの要件を満たしつつ、CMOS技術における既存の最適化プロセスの手順に依拠した集積化の解決手法を利用した、温度に対して非依存型のLC型発振器を提供する。

【解決手段】実質的に温度に非依存のLC型発振器は、温度ヌル位相に実質的に等しい位相でタンク発振を生成するLC発振器タンク10を用いて達成される。該温度ヌル位相は、LC型発振器の出力発振の周波数の温度変化に伴う変動が最小化されるときの、LC発振器タンク10の位相である。該LC型発振器はさらに、該LC発振器タンク10に接続されて、該温度ヌル位相に実質的に等しい位相で該LC発振器タンク10を発振させる周波数安定化回路を含む。

(もっと読む)

FM受信装置

【課題】ノイズの少ないFM受信装置を提供する。

【解決手段】アンテナと、発振回路と、位相比較回路と、チャージポンプ回路と、ループフィルタと、VCOと、VCO発振信号を所定の周波数ごとに分周し分周発振信号を生成する第1の分周回路と、VCO発振信号を所定の周波数ごとに分周し局部発振信号を生成する第2の分周回路とを備え、VCOはLC共振回路を含まない構成のものであり、分周発振信号を位相比較回路の入力信号とするものであって、局部発振信号と電波の信号より、複数の中間周波数信号を生成するミキサと、中間周波数信号をA/D変換するA/D変換器と、A/D変換器より出力された信号のうち、複数の中間周波数信号に対応するいずれか一つを選択し復調するデジタル復調器と、を備えたことを特徴とするFM受信装置を提供することにより上記課題を解決する。

(もっと読む)

位相同期ループの出力VCOにおいて50%デューティサイクルを達成するための方法および装置

【課題】PLLの出力において所望のデューティサイクルを達成するための方法および装置を提供する。

【解決手段】本方法は、制限差動増幅器214を使用して、差動コモンモードクロック信号からデューティサイクルを有するシングルエンドクロック信号を発生させるステップと、シングルエンドクロック信号213のデューティサイクルに応じて差動バイアス電流信号229、230を発生させるステップと、差動バイアス電流信号を制限差動増幅器に与えることによって、シングルエンドクロック信号のデューティサイクルを所望のデューティサイクルに修正するステップとを含む。CML−CMOS変換器回路は、制限差動増幅器214と、シングルエンドクロック信号のデューティサイクルの測定値を発生するための低域フィルタと、(i)測定値を基準電圧と比較し、(ii)比較に応じて差動バイアス電流信号を発生するための第2の差動増幅器とを含む。

(もっと読む)

基準信号発生装置

【課題】外部環境による精度低下への影響を低下させ、且つ、ユーザに必要以上の手間を掛けることなく、安定して高精度な基準周波数信号を継続的に出力し続ける。

【解決手段】制御部10は、位相差の平均が、監視閾値未満であるかどうかによって、較正の有無を判定する。ここで、監視閾値は、当該基準周波数信号発生装置1が搭載される通信機器に求められる精度の仕様を満たすとともに、この仕様の限界に対して所定の余裕を持てるような値に設定されている。監視閾値未満の場合、制御部10は、自身で生成した維持用制御電圧信号を電圧制御発振器14へ与え、監視閾値に達する場合、ループフィルタ12からの制御電圧信号を電圧制御発振器14に与え、電圧制御発振器14はこの制御電圧信号に基づいて較正を行う。

(もっと読む)

リング発振器及びこれを用いるマルチ位相クロック補正回路

【課題】クロスカップル構造を有する複数のバッファを備えて発振し、CMLレベルのクロック信号を生成することのできるリング発振器を提供し、また、基準位相クロック信号を補正して希望の周波数、及び互いに予め定められた位相差を有するマルチ位相クロック信号を生成することのできるマルチ位相クロック補正回路を提供する。

【解決手段】 本発明のリング発振器は、各々クロスカップル構造を有し、予め定められた電圧レベルのバイアス電圧が印加されて複数のクロック信号を生成するための複数のバッファ手段を備え、前記複数のクロック信号が、前記バイアス電圧に対応するスイング幅を有する。

(もっと読む)

PLL方式発振回路、ポーラ送信回路及び通信機器

【課題】VCO101の変調感度のばらつきを低減し、高速、高精度に所望の出力振幅を得ることができるPLL方式発振回路を提供する。

【解決手段】振幅検出器103は、VCO101の出力振幅を検出する。振幅制御部105は、振幅検出器103が検出したVCO101の出力振幅が所望の振幅になるように可変電流源109の電流値を制御する。LPF108は、振幅制御部105と可変電流源109との間に接続される。スイッチ107は、LPF108を振幅制御部105と可変電流源109との間に接続するか否かを切り替える。振幅制御部105は、LPF108又は切り替えスイッチ107のいずれか一方を介して、可変電流源109と接続される。

(もっと読む)

クロック及びデータ復元回路

【課題】入力データ論理判定用クロックとして、周波数の安定したクロックを得ることができ、しかも、消費電力を低減することができるCDR回路を提供する。

【解決手段】入力データの論理判定に使用する内部クロックRCKの発生源として電圧制御発振器15を設ける。電圧制御発振器15は、CMOSインバータをリング接続して構成し、常に電流を消費することがないものとする。両エッジ検出部13は、PLL12内の電圧制御発振器21の出力クロックVCO_CKの遷移タイミングを検出し、電圧制御発振器15の発振周波数がPLL12内の電圧制御発振器21の発振周波数と同一となるように電圧制御発振器15を制御する。

(もっと読む)

原子発振器およびその制御方法

【課題】光情報の検出精度の劣化を抑えながら、ガスセルの温度制御を量子レベルで制御する原子発振器およびその制御方法を提供する。

【解決手段】本実施形態の原子発振器の光学系の要部である物理部50は、ガス状の金属原子を封入したガスセル10およびそれを保持するガスセル保持部材21からなるセルユニット20、ガスセル10を所定の温度に加熱するヒータ15、ガスセル10中の金属原子を励起するコヒーレント光の光源である光源30、ガスセル10を透過した励起光を検出するフォトセンサ40、フォトセンサ40により検出された励起光の強度に基づいてヒータ15を制御する温度制御手段、を有する。ガスセル10は、円筒部11と、該円筒部11の両端の開口部をそれぞれ封鎖して励起光の光路の入射面および出射面を形成する窓部12と、を有し、ヒータ15が、窓部12の前記光路と異なる領域に設けられている。

(もっと読む)

電圧制御発振器、並びにそれを用いたPLL回路及び無線通信機器

【課題】C結型の可変容量回路と直結型の可変容量回路とを上手く混在させて構成し、発振周波数の線形性及び可変範囲のバランスがとれた電圧制御発振器を提供する。

【解決手段】本発明の電圧制御発振器は、並列接続されたインダクタ回路110、C結型可変容量回路120及び140、直結型可変容量回路130、及び負性抵抗回路160と、基準電位Vref1及びVref2を生成する基準電位発生部180とを備える。各可変容量回路120、130、及び140の可変容量素子121、122、131、132、141、及び142のバックゲート端子には、発振周波数をフィードバック制御するための制御電位Vtが印加される。C結型可変容量回路120及び140の可変容量素子121、122、141及び142のゲート端子には、基準電位Vref1及びVref2がそれぞれ印加される。

(もっと読む)

電圧制御発振装置

【課題】高いC/N及び周波数安定度を確保できると共に、周波数可変幅を広くしても帯域外の不要信号の漏れ出しを抑制でき、かつ同時にインピーダンスマッチングもとることができるようにすること。

【解決手段】この電圧制御発振装置は、制御電圧信号に応じて発振周波数が制御される電圧制御発振回路1と、電圧制御発振回路に供給する制御電圧信号を生成するPLL回路2と、電圧制御発振回路1の出力する発振信号を逓倍する逓倍回路3と、逓倍回路3の出力する逓倍信号のうち所定逓倍数の信号を通過させる通過帯域と逓倍回路3に入力した発振信号と同一周波数をトラップするトラップ周波数とが設定された帯域通過フィルタ兼トラップ回路4とを備える。制御電圧信号を分岐して段間結合兼トラップ回路15へ入力し、発振周波数に同期させて段間結合兼トラップ回路15の通過帯域及びトラップ周波数を可変させると共に段間結合量を調整する。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

無線装置

【課題】本発明は、基準発振部から出力される基準信号を用いて、演算部の設定で無線通信の送受信周波数を生成する無線通信機器において、基準発振部の温度特性を補正するためのデータを効率的かつ、高精度な補正を実現する構成を提供することを目的とする。

【解決手段】本発明の無線通信機器300は、送信処理を行う際に、温度検出部305で基準発振部303の雰囲気温度を検出し、該当の温度に対する第1補正データを外部記憶部304より読み出した上で、演算設定部311で、内部記憶部312に記憶されている第2補正データ、基準チャネル設定データを用い送信周波数を演算し、高周波部301から、あらかじめ決められたデータを変調し送信をおこなう。

(もっと読む)

電圧制御型可変周波数発振回路および信号処理回路

【課題】可変容量素子の容量可変域に応じた広い周波数可変域を確保することができる電圧制御型可変周波数発振回路を提供する。

【解決手段】コイルL1,L2および可変容量素子111,112を有する共振回路101と、負性抵抗回路102とを含む発振回路部103を備える電圧制御型可変周波数発振回路である。発振回路部103と電源電位VDDとの間に第1の抵抗301を設ける。また、発振回路部と接地電位端との間には第2の抵抗302を接続するとよい。

(もっと読む)

温度補償のための補助バラクタ

電圧制御発振器(VCO)周波数に対する温度変化の影響を補償するための技法が、開示される。一実施形態においては、補助バラクタが、VCOのLCタンクに結合される。補助バラクタは、温度に伴ってVCO周波数の全体の変化を最小にする、温度依存制御電圧(Vaux)によって制御されるキャパシタンスを有する。デジタル手段とアナログ手段とを使用して制御電圧を生成するための技法が、さらに開示される。補助バラクタ(Caux)は、LCタンクの電圧制御キャパシタ(C)と直列に、または並列にのいずれかで結合されることができる。一実施形態においては、制御電圧は、絶対温度に比例した第1の電流と、温度にわたって一定の第2の電流、例えば、バンドギャップ電流、との間の差を得ることによって生成される。  (もっと読む)

(もっと読む)

容量切り換え回路、VCO、およびPLL回路

【課題】 PLLおよびVCOの発振特性を改善できる容量切り換え回路を提供する。

【解決手段】 端子P1と端子P2との間に、コンデンサC1k(k=0〜n)と、FET(Q1k)と、コンデンサC2kとを直列接続する。FET(Q1k)のソースにFET(Q3k)のドレインを接続する。FET(Q1k)のドレインにFET(Q4k)のドレインを接続する。FET(Q3k、Q4k)のゲートは互いに接続し、それらのソースも互いに接続する。FET(Q1k)のゲートに、このFET(Q1k)をオンオフ制御する制御データbkを供給する。FET(Q4k)のソースに、少なくともFET(Q1k)がオフのときには、FET(Q3k、Q4k)をオフにするソースバイアス電圧VSkを供給する。

(もっと読む)

クロック発生機能付き装置、基準周波数等設定方法、および基準周波数等調整方法

【課題】クロックに関する設定を簡単に行う。

【解決手段】VCXOと、基準周波数とこの基準周波数のクロックをVCXOに発生させる電圧のレベルである基準レベルとを記憶するメモリと、必要な周波数のクロックを、メモリに記憶されている基準周波数および基準レベルを基準に求められる電圧をVCXOに与えて発生させるD/Aコンバータ制御部およびD/Aコンバータと、を有する装置において、下記の処理を行う。試験時レベルを適宜変化させながら、各試験時レベルに応じた電圧をVCXOに与えて試験用クロックを発生させる。試験用クロックを周波数カウンタに出力する。試験用クロックの周波数と目標周波数との差が所定の範囲内であることが周波数カウンタによって確認できたら、メモリに、この試験用クロックがVCXOによって発生された際の試験時レベルを基準レベルとして記憶させ、この試験用クロックの周波数を基準周波数として記憶させる。

(もっと読む)

81 - 100 / 253

[ Back to top ]