Fターム[5J106JJ01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | 発振回路、VCO (253)

Fターム[5J106JJ01]に分類される特許

101 - 120 / 253

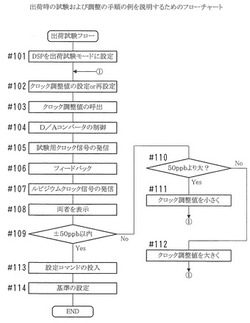

クロック発生機能付き装置、基準周波数等設定方法、および基準周波数等調整方法

【課題】クロックに関する設定を簡単に行う。

【解決手段】VCXOと、基準周波数とこの基準周波数のクロックをVCXOに発生させる電圧のレベルである基準レベルとを記憶するメモリと、必要な周波数のクロックを、メモリに記憶されている基準周波数および基準レベルを基準に求められる電圧をVCXOに与えて発生させるD/Aコンバータ制御部およびD/Aコンバータと、を有する装置において、下記の処理を行う。試験時レベルを適宜変化させながら、各試験時レベルに応じた電圧をVCXOに与えて試験用クロックを発生させる。試験用クロックを周波数カウンタに出力する。試験用クロックの周波数と目標周波数との差が所定の範囲内であることが周波数カウンタによって確認できたら、メモリに、この試験用クロックがVCXOによって発生された際の試験時レベルを基準レベルとして記憶させ、この試験用クロックの周波数を基準周波数として記憶させる。

(もっと読む)

パルス発生回路及び通信装置

【課題】簡単な回路で低消費電力で帯域制限された正確な短パルスの発生回路を具現。

【解決手段】起動信号に基づき所定形状のパルスを出力端子から出力するパルス発生回路において、起動信号の位相が変化した時点からから所定量の時間差で位相が順次変化するn個の信号(nは2以上の整数)を発生するタイミング発生回路10と、起動信号から発生しようとするパルスの継続時間に相当するパルス幅のパルス幅信号を発生するパルス幅信号発生回路30と、パルス幅信号の帯域を制限するフィルタ回路142,143と、所定の電位を供給する第1の電源147及び第2の電源146と、フィルタ回路142,143の出力値によってそのインピーダンス値が制御される可変インピーダンス回路144,145と、n個の信号の少なくとも一部の信号の論理関数値によって出力端子と第1の電源または第2の電源とを可変インピーダンス回路を介して交互に切り替えて接続する。

(もっと読む)

発振器制御装置

【課題】安定した位相雑音特性を高速に得ることができる発振器制御装置を提供する。

【解決手段】動作電流制御信号に基づく動作電流を供給する可変電流源14を含み、発振器調整ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器1と、前記発振信号と基準信号との間の位相差を算出し、位相差信号を出力する位相差算出部(2,3,4)と、前記デジタル制御発振器の発振周波数を設定するための周波数命令ワードと前記位相差信号との差分を平滑化して、前記発振器調整ワードを出力するフィルタ6と、前記発振器調整ワードを測定し、前記動作電流制御信号を出力する制御部7と、を備え、前記制御部は、前記動作電流の値を変化させるように前記動作電流制御信号を出力し、前記発振器調整ワードが極大値となる前記動作電流の値を抽出し、前記可変電流源が供給する動作電流がこの抽出した値となるように前記動作電流制御信号を出力する。

(もっと読む)

フラクショナル−N方式位相同期ループ形周波数シンセサイザ

【課題】 位相比較器の位相差に対する検波電圧特性の非線形性によって、F−N方式PLL周波数シンセサイザ出力に発生するスプリアスの抑圧を実現することを目的とする。

【解決手段】 高周波信号を生成する電圧制御発振器と、前記高周波信号より同期信号を生成する可変分周器と、基準信号を生成する基準発振源と、前記基準信号より位相差を有する2つの基準信号を生成する基準信号生成手段と、前記それぞれの基準信号と前記同期信号を入力とし、第1と第2の位相比較信号を出力する第1の位相比較器と、第3と第4の位相比較信号を出力する第2の位相比較器と、前記第1と第2の位相比較信号を差分した差分結果と、前記第3と第4の位相比較信号を差分した差分結果を合成して平滑化した合成信号を出力するループフィルタとを備え、前記合成信号に応じて電圧制御発振器を制御することにより前記高周波信号を生成する。

(もっと読む)

周波数補償回路

【課題】感温部品を用いることなく、温度変動やデバイス自体に個体差がある場合でも、高精度で安定した掃引周波数又は変調信号を得ることが可能となるようにする。

【解決手段】制御電圧発生器から出力された掃引波(又は変調波)の制御電圧を入力し、所定幅の周波数を発生するためのVCO14、このVCO14の出力を入力し、任意に設定した校正周波数に位相ロックした電子同調電圧をVCO14へ帰還させるPLL−IC回路20及びループフィルタ21、上記VCO14の前段で、制御電圧発生器側とPLL回路側とを切り替える切替えスイッチ18、この切替えスイッチ18でPLL回路側に切り替えたとき、上記ループフィルタ21から電子同調電圧Vfを取り出し、制御電圧発生器側に切り替えたとき、取り出した電子同調電圧を上記制御電圧発生器からの出力制御電圧Vaに加算する回路(CPU23,DAC26,加算器28)を設ける。

(もっと読む)

電圧制御装置およびクロック出力装置

【課題】電圧制御型水晶発振器(VCXO)から出力される信号の周波数をより高精度に制御することができる電圧制御装置20を提供する。

【解決手段】本発明の電圧制御装置20は、電圧制御型水晶発振器(VCXO)の温度毎の制御電圧値を、異なる条件下で予め2種類測定しておき、実際に温度補正を行う際には、現在のVCXOの温度に対応する制御電圧値を、それぞれの測定条件毎に1つずつ抽出し、抽出した制御電圧値を平均したものを現在の温度における制御電圧としてVCXOに供給する。

(もっと読む)

光学系及び原子発振器

【課題】複数の受光素子を発光素子と同一側に併置し、複数の受光素子を電気的に接続するボンディングワイヤを短くしてモジュール実装を容易とし、且つEIT信号レベルを大きくしてS/Nを改善した光学系を備えた原子発振器を提供する。

【解決手段】この光学系1は、共鳴光3を出射するコヒーレント光源2と、コヒーレント光源2の出射側に配置され共鳴光3を少なくとも2つの光路5、6に導く導光手段4と、導光手段4の出射側に配置されガス状の金属原子を封入すると共に、この金属原子ガス中に導光手段4により導かれた共鳴光5、6を通過させるガスセル7と、ガスセル7を通過した各共鳴光5、6を夫々検出する光検出器(光検出手段)10、11と、光検出器8、9から検出された信号を合成する合成回路10と、合成回路10の出力信号により、発振周波数を制御する周波数制御回路11と、を備えて構成されている。

(もっと読む)

PLL回路

【課題】 高い線形性をもった電圧―電流特性を備え、ゲイン変動を抑えた電圧電流変換回路を有するPLL回路を提供する。

【解決手段】 電圧電流変換回路11は、制御電圧VCを受けるNチャネルMOSトランジスタN1と、NMOSトランジスタN1と直列に接続されたPチャネルMOSトランジスタP1と、PMOSトランジスタP1とミラー回路を構成するPMOSトランジスタP2と、PMOSトランジスタP1と並列に接続された電流源13を備える。PMOSトランジスタP2から出力される制御電流Ioutは、NMOSトランジスタN1に流れる電流から電流源13によって供給される電流の分だけ差し引かれる。

(もっと読む)

PLL回路

【課題】安定かつ最適な位相雑音レベルで動作するPLL回路を提供する。

【解決手段】上記課題を解決するために、PLL回路100は、2つの入力信号の位相差に応じた電圧を出力する位相比較器101と、電流変換利得を調整して入力信号を任意の昇圧率で上昇させる可変チャージポンプ102と、所定の周波数特性を有するループフィルタ103と、VCO104と、ループフィルタ103の出力信号をデジタル値に変換するA/Dコンバータ105と、VCO104を選択するともにA/Dコンバータ105の出力値に応じて可変チャージポンプ102を制御するVCO選択回路106と、VCO104からの出力信号を1/N倍に分周する分周回路107と、を備える。

(もっと読む)

半導体素子、クロック同期化回路、及び、クロック同期化回路の駆動方法

【課題】クロック同期化回路は、インジェクションロッキング方式を使用してジッタピーキング現象と制御電圧にパターンジッタが大きくなる現象なく、所望の位相・周波数ロッキング動作を行う。

【解決手段】クロック同期化回路は、基準クロック信号とフィードバックされるフィードバッククロック信号の位相・周波数差を検出信号として出力する位相・周波数検出手段332と、検出信号に応答してチャージポンプ動作を行うチャージポンプ手段334と、チャージポンプ動作に応答して発振制御電圧を生成する制御電圧生成手段336と、発振制御電圧に対応してフィードバッククロック信号を生成する電圧制御発振手段338と、発振制御電圧に応答して自由発振周波数が設定され、基準クロック信号に同期化した内部クロック信号を生成するインジェクションロッキング発振手段310とを具備する。

(もっと読む)

PLL回路

【課題】 VCOを構成する電流制御発振回路を制御する電流を生成する電圧−電流変換の動作を高速化して、従来に比較して周波数制御の応答特性を向上させるPLL回路を提供する。

【解決手段】 本発明のPLL回路は、電圧−電流変換回路と電流加算器と電流制御発振回路とから構成され、制御電圧及び制御電流に対応した周波数のパルスを出力する電圧制御発振回路と、パルスと、電圧制御発振回路が生成すべき周波数の基準パルスとの位相差により、第1の制御信号及び第2の制御信号を出力する位相検出器と、第1の制御信号により、第1の充電電流または第1の放電電流を出力する第1のチャージポンプ回路と、第1の充電電流または第1の放電電流により制御電圧を生成し、電圧制御発振回路に出力するループフィルタと、第2の制御信号により、第2の充電電流または第2の放電電流である制御電流を生成し、制御電圧発振回路に出力する第2のチャージポンプ回路とを有する。

(もっと読む)

通信装置、及びそのシステムクロック制御方法

【課題】 受信バッファ量を増減させずに、IP網の揺らぎに対処する。

【解決手段】 通信装置であるIP−PBX100は、IP網5からのパケットを一時的に溜める受信バッファ32と、受信バッファに溜まったパケットをシステムクロック信号に同期して順次処理するパケット処理部33と、受信バッファに溜まっているデータ量を検出するバッファデータ量検出部40と、バッファデータ量検出部で検出されたデータ量に応じた周波数のシステムクロック信号を発振するシステムクロック発振部50と、を備えている。

(もっと読む)

位相同期回路およびそれを用いた半導体集積回路装置

【課題】プロセスばらつき、環境変動によらず、所望の特性を満足する自動調整できる位相同期回路を提供すること。

【解決手段】位相同期回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ3、分周器6、セレクタ7、電圧制御発振器8を備えている。分周器6は、出力信号と基準信号を入力して出力信号を分周して帰還信号を出力するとともに出力信号から選択信号とトリミング信号とリミット信号を出力する。電圧制御発振器8は、制御電圧と基準電圧とトリミング信号とリミット信号を入力して制御電圧に応じて出力信号周波数を変え、出力信号の上限周波数を制限できるとともに、トリミング信号によって制御電圧に対して出力する出力信号の周波数感度と、リミット信号によって出力信号の上限周波数を変えることができる。

(もっと読む)

無線送信回路及びそれを用いた送受信機

【課題】 部品点数を削減でき、小型化に適した移動体通信機用の無線送信回路を提供する。

【解決手段】 従来の移動体通信機で必要とされていたTX,RF,IF周波数帯の3つの発振器のうちRF周波数帯PLLと、IF周波数帯PLLとを1つのPLLシンセサイザSSで兼用し、チップ内で大きな面積を専有する必要な発振器の個数を低減して部品点数を削減する。具体的には、RF周波数帯PLLのVCO21の出力を分周することにより、RF,IF周波数帯で用いる局部発振信号を生成する構成とする。

(もっと読む)

クロック発生回路

【課題】高精度な周波数変調が可能なスペクトラム拡散クロック発生回路を提供する。

【解決手段】このスペクトラム拡散クロック発生回路において、PLL回路31は、それぞれ位相の異なるクロック信号CLKV1〜CLKV5を出力する。セレクタ23は、クロック信号CLKV1〜CLKV5のうちのいずれか1つを選択し、制御回路24はセレクタ9の信号選択動作を制御する。入力分周回路1は選択クロック信号を分周して基準クロック信号CLKRを出力する。PLL回路21は、基準クロック信号CLKRを周波数逓倍した発振クロック信号CLKOを生成する。これにより、発振クロック信号CLKOの位相を微調整することができる。したがって、高精度な周波数変調が可能なスペクトラム拡散クロック発生回路が実現できる。

(もっと読む)

位相ロックループ回路

【課題】広周波数範囲で動作可能であり、電圧制御発振器のゲインを低減させることができる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号及びフィードバッククロック信号の位相差を検出する位相差検出器(101)と、制御電圧を保持するコンデンサ(117)と、前記検出された位相差に応じて、前記コンデンサを電源電圧又は基準電位に接続するチャージポンプ回路(102)と、前記制御電圧に応じた発振周波数の出力クロック信号を生成し、前記出力クロック信号又は前記出力クロック信号に応じた信号を前記フィードバッククロック信号として前記位相差検出器に出力する電圧制御発振器(104)とを有し、前記電圧制御発振器は、4段の差動リングオシレータ(131〜134)と、前記4段の差動リングオシレータの異なる段で出力されるクロック信号の排他的論理和信号を出力する第1の排他的論理和回路(127)とを有する。

(もっと読む)

ルビジウム原子発振器

【課題】部品コストの低減と、基板を小型化することができると共に、導体がマイクロ波に与える影響を最小限にして、特性の安定化を図ることができるルビジウム原子発振器を提供する。

【解決手段】キャビティ内にはフォトセンサ7があり、フォトセンサ47の一方の信号線Bはコネクタ15のb端子によりキャビティ外の基板25の表面でグランドに接続され、フォトセンサ7の他方の信号線Aはコネクタ15のa端子に接続されて、インダクタ31を介してI/V変換用IC9に入力されると共に、コンデンサ32を介して同軸端子14に接続されている。そして、同軸端子14には測定器34を接続して、キャビティ内のマイクロ波の強度を測定する。

(もっと読む)

調整可能な周波数を備える信号発生器

発振信号の周波数は、出力信号の位相および/または周波数を調整するために一時的に調整される。例えば、発振信号の周波数は、出力信号の位相を調整するために、極めて短期間で調整されてもよい。加えて、発振信号の周波数は、出力信号の有効周波数を調整するために、反復される手法で一時的に調整されてもよい。いくつかの態様では、発振信号の周波数は、発振回路に関連したリアクタンス回路の再構成によって調整される。  (もっと読む)

(もっと読む)

電圧制御発振回路

【課題】発振周波数を上昇させた場合であっても、電圧制御発振回路のコンデンサの充放電電流の増加を抑制する。

【解決手段】コンデンサの充電電圧を入力電圧に応じた周波数で発振させる電圧制御発振回路であって、コンデンサの充電電圧の最低電圧が第1電圧、充電電圧の最高電圧が第1電圧より高い第2電圧となるよう、コンデンサを繰り返し充放電する充放電回路と、入力電圧に応じて第1電圧と第2電圧との差を制御する制御回路と、を備える。

(もっと読む)

VCO回路及びそれを用いたPLL回路

【課題】VCO回路の最適な発振状態を設定するために、製造されたIC毎にバラツキを評価し且つそのバラツキに応じた設定値を指示しなければならないという問題がある。

【解決手段】VCO回路は、制御電圧に応じ制御電流を流す電圧電流変換器と、その制御電流に応じ所定の周波数で発振する電流制御発振器からなる構成において、制御電圧に応じ電圧電流変換器の変換利得を調節する調節回路を更に備えたことを特徴とし、外部からの制御に依存せずに、製造されたIC毎のバラツキに応じ、VCOをロックアップさせる、いわゆる自己制御性(Self Regulating Characteristics)を有する電圧制御発振器を提供することができる。

(もっと読む)

101 - 120 / 253

[ Back to top ]