Fターム[5J106KK08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 性能の向上 (885) | キャプチャーレンジの拡大 (127)

Fターム[5J106KK08]に分類される特許

21 - 40 / 127

発振器

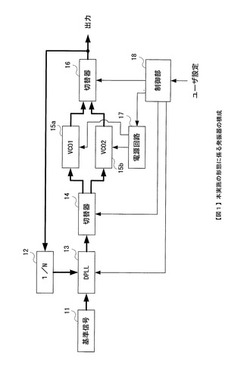

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

高周波発振源

【課題】発振器を広帯域化しても、発振器の全同調帯域に渡って低位相雑音化を図ることができる高周波発振源を得ることを目的とする。

【解決手段】注入同期電圧制御発振器1の出力波を分配する電力分配器2と、その電力分配器2により分配された出力波を遅延して、遅延後の出力波を注入波として注入同期電圧制御発振器1に帰還させる遅延処理部4とを設け、移相量制御部11が注入同期電圧制御発振器1の出力波と注入同期電圧制御発振器1に帰還される注入波の位相差がゼロになるように、移相器7により出力波に与えられる移相量を制御する。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

PLL回路

【課題】VCOのVT端子側から見えるバラクタダイオード数を減少させることによりリファレンスリークを低減するPLL回路を提供する。

【解決手段】PLL回路を構成するループフィルタから出力されるVCO制御電圧とVCOを予め関連付けて設定し、ループフィルタのVCO制御電圧に基づいて対応するVCOを選択し、該VCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を制御する切替信号を生成するVCO切替回路と、切替信号に基づいて、選択されたVCOのみの電圧制御発振器制御電圧端子とループフィルタの出力端子を接続し、他のVCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を解除するVT選択回路と、を備えるVCOの制御電圧端子にバラクタダイオードが接続された、発振周波数帯域の異なる複数のVCOを備えるPLL回路である。

(もっと読む)

PLL回路、送受信器及び携帯情報端末

【課題】長時間使用等の発熱でも周波数ロックが外れないPLL及びその制御方法を提供する。

【解決手段】本発明の基準周波数生成ブロックはPLL5、RF制御回路14及びBB制御回路24の3つから構成される。PLL5のループフィルタ102から引き出す検出信号(VTUNE)131が所定の電圧レンジから外れるとLKDETB信号61がPLL5からBB制御回路14に対して出力される。BB制御回路24はその後、RF制御回路14を介してPLL5の検出信号131の処理を止め、その後RF制御回路14にオートバンドセレクト動作を実行させる。この処理により、送受信を止めることなく実行し続ける無線LAN等の送受信器のVCOの温度特性の調整を行うことが可能となる。

(もっと読む)

対称性負荷遅延セル発振器(symmetricloaddelaycelloscillator)

【解決手段】発振器は、制御回路と、対称性負荷遅延セルのリングとを含む。各遅延セルは、2つの新規な対称性負荷を含む。各負荷は、レベルシフト回路と、電流ソース接続されたトランジスタと並列に結合されたダイオード接続されたトランジスタとを含む。制御回路は、発振器入力信号をバイアス制御信号に変換し、バイアス制御信号は、対称性負荷の実効的な抵抗を、遅延セルの遅延が入力信号の関数であるように制御する。制御回路は、発振遅延セル出力信号が一定の振幅を有するように遅延セルのレベルシフト回路を制御するため、制御ループの対称性負荷レプリカを用いる。第1の有利な側面では、この一定の振幅により、発振器は広い周波数レンジで動作可能である。第2の有利な側面では、発振器入力信号は出力信号発振周波数に対して、実質的に線形の関係を有する。 (もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

PLL回路

【課題】温度変化により電圧制御発振器を制御する制御電圧に変動が発生しても位相同期回路のロックが外れることを最小限の電圧制御発振器により防止する位相同期回路を提供する。

【解決手段】発振周波数帯域の異なる複数の電圧制御発振器を備えるPLL回路であって、ループフィルタから出力される電圧制御発振器制御電圧の温度特性と正の相関関係にある基準電圧を出力する基準電圧源回路と、電圧制御発振器制御電圧と基準電圧とを比較して判定する判定回路と、判定回路の出力信号により複数の電圧制御発振器から1つの電圧制御発振器を選択する選択回路と、を備えるPLL回路である。

(もっと読む)

デジタルPLL回路及びデジタルPLL動作方法

【課題】CLVスピンドル制御のランダムシーク時でもスループット低下を抑え、かつ安価で消費電力を抑えたワイドキャプチャ対応のデジタルPLL回路を提供する。

【解決手段】本発明のデジタルPLL回路10Aは、周波数値fq’に応じてマスタクロックsclkの周波数を切り替えるマスタクロック切り替え手段10Bと、周波数値fq’に一定の倍率を乗じて数値制御発振器6へ出力するとともに、マスタクロックsclkの周波数が切り替わる前後で同期クロックgclkの周波数が一定になるように前記倍率を切り替える倍率切り替え手段10Cと、を備えたことを特徴とする。

(もっと読む)

クロック再生回路及びクロック再生方法

【課題】回路規模を大きくすることなく、広い範囲のクロック周波数を再生することが可能なクロック再生回路を提供する。

【解決手段】クロック信号を生成するクロック信号生成回路11と、入力データ信号とクロック信号との位相比較出力信号を出力する第1及び第2の位相比較器13,14と、位相比較出力信号に基づいて入力データ信号とクロック信号との周波数差信号を出力する周波数比較器15とを備える。クロック信号生成回路11は奇数個の論理反転回路を直列につないで位相の異なる2種のクロック信号を出力し、それぞれを別々の位相比較器13,14に入力して位相を比較して位相比較出力信号を出力し、周波数比較器15は第1及び第2の位相比較器13,14における各位相比較出力信に基づいて周波数を比較する。

(もっと読む)

PLL回路

【課題】電圧制御発振器が発振信号出力動作を停止した場合、自動的に最適消費電流で電圧制御発振器の発振信号出力動作を復帰させることができるPLL回路を提供する。

【解決手段】リセット制御回路7は、電圧制御発振器5の発振信号出力動作の停止を検出し、電圧制御発振器5の発振信号出力動作の停止を検出している間、基準信号Ref_CKを分周してなるリセット信号RESETを生成する。カウンタ8は、リセット信号RESETの立ち上がり変化の回数をカウントする。ローパスフィルタ4は、前記リセット信号RESETがLレベルの間に周波数制御電圧Vcntを初期化する。電圧制御発振器5が有する出力アンプは、前記カウンタ8が出力するカウント値Cnt[1:0]が増加する毎に駆動電流を段階的に増加させることにより出力駆動能力を段階的に増加させ、周波数帯域を段階的に上げる。

(もっと読む)

PLL回路

【課題】PLL回路のロックアップ時間を短縮することである。

【解決手段】VCO・電流切替回路15は、外部から与えられる分周データに基づいて、複数のVCO22a〜22nの内の1つを選択するVCO選択信号を出力する。また、VCOを切り替える際に、可変チャージポンプ20の出力電流を通常(ロック時)より大きな値に変更する切替信号を出力する。VCO・電流切替回路15は、VCOの切り替えが終了したなら、可変チャージポンプ20の出力電流を通常時の小さい値に切り替える切替信号を出力する。

(もっと読む)

位相検出回路

【課題】位相ロックループ周波数シンセサイザ設計における、大きな電圧制御発振器範囲(例えば、487MHz)、(例えば)1.2V電力供給電圧、および低い電力消費の要求を達成する。

【解決手段】位相検出回路は、参照信号を受信するように構成された参照入力と、フィードバック経路においてディバイダ回路からの分周信号を受信するように構成されたフィードバック入力と、参照信号と分周信号の間の周波数及び位相関係に従って位相ロックループ内のチャージポンプを制御するための制御パルスを生成するように構成されたパルス生成回路と、を有し、分周信号は、分周信号の周期の半分よりも短い長さを具備するパルスを有し、且つ、パルス生成回路は、分周信号のエッジ及び参照信号のエッジから制御パルスのエッジを定義するように、分周信号のパルスをマスクとして使用して参照信号をマスキングすることにより、制御パルスを生成するように構成されている。

(もっと読む)

信号処理装置及び信号処理方法

【課題】最大の周波数マージンで、発生させる発振周波数をロック状態にする。

【解決手段】ループフィルタ23は、発振周波数における所定の特性に基づいて、入力される制御電圧に対応して発振周波数を発生させるVCO63であって、所定の特性が粗調整されるVCO63に、制御電圧を入力し、VCO粗調整回路135は、制御電圧が所定の設定範囲を超えた場合に、VCOによる所定の特性を、複数の特性のうちのいずれかに粗調整し、DAC133は、制御電圧が所定の設定範囲内で変化する場合に、発振周波数がロック状態とならないとき、所定の設定範囲を広げる方向に更新する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

位相同期ループ回路

【課題】出力周波数レンジの広いPLL回路を提供すること。

【解決手段】本発明の一態様は、入力パルス信号と出力側からフィードバックされたフィードバックパルス信号との位相差に基づいて生成された電圧を、制御電流Icへ変換する電圧電流変換回路104と、制御電流Icに応じた周波数のパルス信号を生成する電流制御発振器105と、制御電流Icを検出する電流検出部108と、検出された前記制御電流に基づいて、電流制御発振器105から発振される出力パルス信号の周波数レンジを切り替える周波数レンジ切替回路106と、を備えた位相同期ループ回路である。

(もっと読む)

三分周直交位相周波数分周器

【解決手段】局部発振器は、VCOの出力に結合されたプログラム可能な周波数分周器を備える。周波数分周器は、3で周波数分周するためにセットされることができる。除数に関係なく、周波数分周器は、90度で位相が互いに異なる直交位相信号(I、Q)を出力する。3で分周するために、周波数分周器は、三分周周波数分周器を備える。三分周周波数分周器は、三分周回路、遅延回路、及びフィードバック回路を備える。三分周回路は、VCOから信号を周波数分周し、それから、120度で位相が互いに異なる三つの信号C、A´、及びBを生成する。遅延回路は、信号A´の遅延バージョンAを生成するために、信号A´を遅延する。フィードバック回路は、遅延バージョンA(I)が、信号C(Q)に関して90度位相がずれるように遅延回路を制御する。 (もっと読む)

位相同期回路、情報再生装置、電子機器、位相同期回路のゲイン制御方法

【課題】PLLゲインを自動制御してキャプチャ時間の短縮やエラーレートの改善を実現するに当たり、ロック判定の手法として種々の方法を提案する。

【解決手段】媒体再生時のPLL動作時に、PLLロック状態を示す情報を用いてPLLゲインを切り替えることでロバストなPLLを実現する。PLLロック状態の検出は、フレームシンクの検出結果、位相誤差の絶対値の積算量、の何れかを評価指標として測定し、一定区間での当該評価指標の大小を判定し、判定結果に基づき位相同期ループがロックしているか否かを示すRF品質信号RQを生成する。フレーム同期信号の検出間隔を監視し、その監視結果に基づきRF品質信号RQを生成するとよい。RF品質信号RQは、概ねPLLがロック時はH、アンロック時はLとなる。RF品質信号RQがHレベルの区間では低倍率となり、RF品質信号RQがLレベルの区間では高倍率となるように、PLLゲインを制御する。

(もっと読む)

PLL回路

【課題】回路や制御を複雑にすることなく、電圧制御発振回路の発振周波数レンジを広く保持しつつ出力クロックのジッターを低減可能なPLL回路を提供すること。

【解決手段】前段のLPF3から入力される制御電圧信号VCTRLの電位に応じた周波数を有する出力クロックを、制御端子に入力される制御電圧に応じて遅延時間が変化する遅延回路のM個を環状に接続したリングオシレータを用いて発生するVCO回路4aを備えるPLL回路において、VCO回路4aは、制御電圧信号VCTRLから低周波帯域の制御電圧信号VCTRLを抽出する低域通過フィルタを備え、前記リングオシレータは、前記M個の遅延回路のうち、m個(m<M)の各遅延回路の制御端子に制御電圧信号VCTRLが入力され、(M−m)個の各遅延回路の制御端子に制御電圧信号VCTRL2が入力される。

(もっと読む)

21 - 40 / 127

[ Back to top ]