Fターム[5J106KK08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 性能の向上 (885) | キャプチャーレンジの拡大 (127)

Fターム[5J106KK08]に分類される特許

81 - 100 / 127

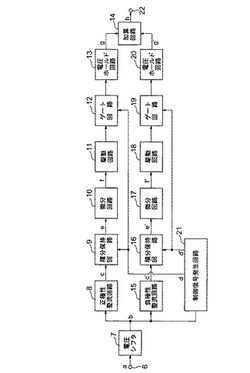

位相比較信号処理回路

【課題】PLLのデジタル位相比較器の出力矩形波信号を処理し、PLLの引き込み可能な周波数幅を拡げ、同期時間を短縮する位相比較信号処理回路を提供する。

【解決手段】矩形波信号を両極性信号に変換する電圧シフタ7と出力端子22間に並列接続され、整流回路8と積分保持回路9と微分回路10とゲート回路12と電圧ホールド回路13と共通の加算回路14とからなる第1信号路、及び、整流回路15と積分保持回路16と微分回路17とゲート回路19と電圧ホールド回路20と前記加算回路14とからなる第2信号路、第1信号路及び第2信号路の積分保持回路9、16とゲート回路12、19を個別制御する制御信号発生器21を備え、第1及び第2信号路で、両極性信号の整流、整流電圧の積分保持、積分保持値の微分、微分出力の保持、保持電圧の加算を行うことにより処理信号を出力する。

(もっと読む)

PLL回路

【課題】複数のVCOを有するPLL回路のチップ上の占有面積を削減でき、且つ、PLL回路に対するマイコンの負担を軽減できる。

【解決手段】本発明の例に関わるPLL回路は、位相差信号を出力する位相比較回路1と、位相差信号に基づくチューニング電圧を出力するチャージポンプ回路2と、チューニング電圧に基づく発振周波数を出力する複数のVCO51〜5nと、複数のVCOの中から1つのVCOを自動的に選択するオートセレクト回路を具備し、オートセレクト回路は、チャージポンプ回路2と接続される比較回路3と、比較回路3とVCO51〜5nと接続されるカウンタ4とを具備し、比較回路3は、チューニング電圧に基づき、カウンタ4をアップカウント、又は、ダウンカウントさせるアップ/ダウン信号を出力し、カウンタ4は、アップ/ダウン信号に基づき、複数のVCO51〜5nの中から1つのVCOを選択するセレクト信号を出力することを備える。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】スイッチオーバーから発生する出力信号における不所望の位相変化を信頼性を持って回避することが可能なフェーズロックループ。

【解決手段】制御可能オシレータDCOが出力信号CKoutを発生し、PLL12入力クロックとして使用するために第一クロック/第二クロックCKin2、CKin1を切り換えることが可能である。使用中のCKin1又はCKin2と、CKoutのプリセットされ、位相シフトされたCK<1:8>間の位相差を決定し、DCOを制御するために使用され、使用されていないCKin2又はCKin1がCKoutを発生するために、位相が調節される。入力クロックの幾つかのCKin1,CKin2,CKin3間の位相差がスイッチオーバーの前に調節されることで、スイッチオーバーから発生するPLL出力信号における不所望の位相変化を高い精度で回避し且つヒットレススイッチングを達成する。

(もっと読む)

PLL回路および記録情報再生装置

【課題】PD出力から微分値を求めると、平均値が“0”の周期関数の微分の平均値はやはり“0”となり、上下バランスが崩れた位相誤差検出特性が得られない。

【解決手段】加算器4203の加算結果ADDである位相誤差絶対値を絶対値比較器4205でしきい値Vthと比較し、当該位相誤差絶対値がしきい値Vthを超えた時点でのPHERR信号の極性と、現時点でのPHERR信号の極性とを不一致検出回路4208で比較する。そして、不一致のときにビットスリップが起きたと判断し、現時点でのPHERR信号の極性を極性反転回路4210で反転し、最終的なPD出力とすることで、上下バランスが崩れた位相誤差検出特性を実現する。

(もっと読む)

PLL回路

【課題】ループフィルタの出力を上限値、下限値と比較して、PLL回路がロックしているかどうかを判定するロック判定回路の上限値、下限値が固定されているので、入力信号の周波数のずれや部品特性のばらつきによっては、キャプチャーレンジがこの上下限値から外れてロックしなくなるという課題を解決する。

【解決手段】ロックしたときのループフィルタの出力の上限値と下限値を上限値/下限値検出回路で検出して保持し、この保持した上下限値をリミット回路に入力し、このリミット回路でループフィルタの出力を前記上下限値の間の値に規制するようにした。ループフィルタの出力電圧が常にキャプチャーレンジ内に規制されるので、入力信号の周波数のずれや部品特性のばらつきに関わらず、確実にロックさせることができる。

(もっと読む)

DLL回路

【課題】ジッタを小さくする、ロックレンジを広くする、最高動作周波数を上げる及び消費電力を下げることを同時に満たすDLL回路を提供する。

【解決手段】n個(nは2以上の整数)の直列に接続された遅延素子を有し、1段目の遅延素子に同期基準信号が入力され、k(kは1≦k<nをみたす整数)段目の遅延素子により遅延された前記同期基準信号がk段目の遅延素子より遅延量の大きいk+1段目の遅延素子へそれぞれ出力される遅延回路2と、前記遅延素子がそれぞれ出力する遅延された前記同期基準信号のうちの1つを選択し出力する選択回路3と、選択回路3が出力する信号を所定時間遅延して出力する調整回路4と、前記同期基準信号及び調整回路4より出力される信号の位相を比較し、比較結果を出力する位相比較回路5と、前記比較結果が入力され、それに基づいて選択回路3の制御を行う制御回路6と、を備える。

(もっと読む)

周波数推定方法、広帯域周波数弁別器及び無線位置測定用受信機

【課題】 サンプリング周波数の2倍の周波数における回転因子の集合に対応する、DFT演算子と1/2DFT演算子の組み合わせにもとづく周波数弁別器である。

【解決手段】 周波数弁別器は、ゼロ又は不連続点を持たないように選定される。そのため、この発明の弁別器は、拡張された動作範囲において、より安定的かつ良好に動作する。この発明の弁別器は、GPS受信機に適用された場合、初めに大きな誤差が有っても、より確実にキャリヤ周波数にロックすることが可能であるとともに、誤ってロックする問題を防止するものである。

(もっと読む)

発振回路とこれを用いたPLL発振回路とこのPLL発振回路を用いた高周波受信装置

【課題】所定の周波数変化範囲を確保しながら、位相雑音特性を改善する。

【解決手段】差動タイプの増幅器54,55で構成された発振部52と、この発振部52の出力端子52b,52cに入力端子53a,53bがそれぞれ接続された同調部53からなる発振回路51において、同調部53は、可変容量素子74,75とインダクタンス72,73からなる並列接続回路とを備え、可変容量素子74に制御電圧を供給する制御端子53cと可変容量素子75に制御電圧を供給する制御端子53dとをそれぞれ独立に設け、制御端子53dに供給する制御電圧による発振周波数の変化量の方が、制御端子53cに供給する制御電圧による発振周波数の変化量より小さく設定した。

これにより、所期の目的を達成することができる。

(もっと読む)

電圧制御型装置のためのハイブリッド電流枯渇型位相補間型回路

【課題】調整回路を提供する。

【解決手段】調整回路は、第1のタイプの信号差を調整するように構成された電流飢餓電圧制御型回路を含む。位相補間電圧制御型回路は、第2のタイプの信号差を調整するように構成される。この電流飢餓回路と位相補間回路とは、調整回路の改善された動作特性を提供するように協力する。

(もっと読む)

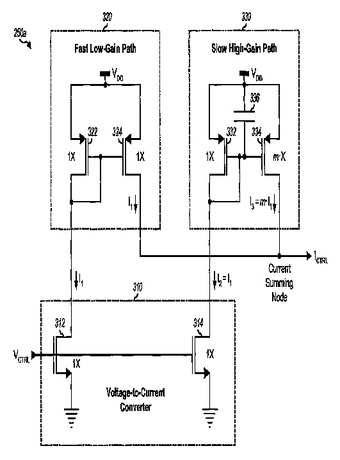

電流−モード利得分割デュアル−パスVCO

大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術が記載される。本技術は、(1)VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び(2)通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ、電流増幅器、総和器、及び電流制御オシレータ(ICO)を含む。電圧−電流コンバータは、制御電圧を受け取り、そして第1電流と第2電流とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流を受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。  (もっと読む)

(もっと読む)

広い周波数範囲で動作可能なプログラマブルトランシーバ

【課題】非常に広範囲な周波数にわたり動作し得るFPGAトランシーバを提供すること。

【解決手段】FPGAは、広範囲な可能性ある周波数またはデータ転送速度における任意の周波数またはデータ転送速度で、データを受信および/または送信するように改造されたデータ受信機および/または送信機回路網を含み得る。PLL回路網は、そのような受信機および/または送信機回路網の動作に必要であり得る。広い周波数範囲にわたり満足のいく動作のために、複数のPLL回路が備えられる。これらのPLL回路は、全周波数において動作する能力があり、その範囲のある部分ではその範囲のその他の部分よりおそらく良いジッタ性能を持って動作し得る。特に最初に述べたPLLのジッタ性能がある可能性あるニーズを満たすには適当でない場合、広い範囲の特定の部分に焦点をあてた1個以上のPLL回路を備えられ得る。

(もっと読む)

電子回路及び電子回路を動作するための方法

【課題】第1の位相比較器(PC1)及び第1の制御可能な発振器(VCO1)を有する第1のPLL回路(PLL1)と、第2の位相比較器(PC2)及び第2の制御可能な発振器(VCO2)を有する第2のPLL回路(PLL2)とが設けられた電子回路において、入力信号(IN)が、第1のPLL回路(PLL1)の入力端に供給される形式のものを改良して、入力信号にロックすることを可能にし、低いジッタを伴う出力クロック信号を形成し、同時に大きいロックレンジを示す回路を形成する。

【解決手段】入力信号(IN)又は第1のPLL回路(PLL1)の出力信号が、選択的に第2のPLL回路(PLL2)の入力端に供給され、該第2のPLL回路(PLL2)の出力が、回路の唯一の出力であるようにした。

(もっと読む)

同期装置、同期方法及び同期プログラム並びにデータ再生装置

【課題】本発明は、周波数誤差の引込範囲を広げて位相同期の能力を向上できるようにする。

【解決手段】本発明は、周波数誤差検出回路33において位相検出器54により補間信号pkにおける位相誤差Δτ(k)を検出し、差分算出器55により当該位相誤差Δτ(k)と1クロック前の位相誤差Δτ(k−1)との差分を基に周波数誤差Δf(k)及びその移動平均である平均周波数誤差Δfa(k)を算出し、位相同期部8において周波数収束ループ又は周波数初期値ループを形成して周波数誤差Δf(k)に基づく周波数補正値DF又は平均周波数誤差Δfa(k)に基づく平均周波数補正値DFAをLPF25の積分項に加算することにより、当該位相同期部8における周波数誤差Δf(k)を高速に且つ安定してほぼ0に収束させることができる。

(もっと読む)

位相調整回路

【課題】データレートの高低にかかわらずデータ信号と遅延クロック信号との位相関係を最適に調整する位相調整回路を実現する。

【解決手段】離散的にデータ信号Dataとクロック信号CLKとの位相を調整する位相調整回路は、クロック信号CLKを遅延させて遅延クロック信号Rclkを生成する遅延線(10A)、データ信号Dataと遅延クロック信号CLKとの位相を比較する位相比較器(20)、位相比較器(20)の比較結果に基づいて、遅延制御信号SSxを出力する遅延制御部(30)、クロック信号CLKの周波数に基づいて、遅延制御信号RSxを出力する遅延制御部(40A)を備えている。ここで、遅延線(10A)は、制御信号に基づいて、クロック信号に対する遅延クロック信号の遅延量を決定する。

(もっと読む)

デジタルとアナログ制御を用いた電圧制御遅延ラインの遅延セル

【課題】デジタル制御方法とアナログ制御方法を混合して動作範囲を極大化する、デジタルとアナログ制御を用いた電圧制御遅延ラインの遅延セル回路を提供する。

【解決手段】本発明は、差動入力クロック信号が印加される差動入力トランジスタと、電源供給端に一方端が接続され、アナログ制御電圧に応答してファイン遅延量を調節するためのアナログ制御トランジスタ部と、前記アナログ制御トランジスタ部と前記差動入力トランジスタとの間に接続され、デジタルコードに応答してコース遅延量を調節するためのデジタル制御トランジスタ部とを備える。

(もっと読む)

位相同期ループ回路、位相同期ループ回路のループフィルタゲイン制御方法並びに再生装置

【課題】 ディジタルPLLのループフィルタゲインを自動制御することで、キャプチャ時間の短縮、エラーレートの改善を実現する位相同期ループ回路を提供する。

【解決手段】 ロックモード生成回路29は、イコライザ10からの周波数調整再生信号(e)とビタビ復号器12からのSAM値と補間フィルタ24からのフィルタ出力である同期がとれた再生信号(f)とに基づいて、上記ループフィルタ19の自動調整ゲインKp_auto及びKi_autoを出力する。

(もっと読む)

半導体集積回路

【課題】 トリミングを行わずに電圧制御発振回路の発振周波数を調整すること。制御回路の面積を抑え、調整誤差の少ない発振回路を内蔵した半導体集積回路を提供すること。

【解決手段】 電圧制御発振回路(VCO)の周波数を調整する可変容量素子を、プロセスや素子のばらつき調整用可変容量素子群と、周波数選択用可変容量素子群との2系統に分離して調整を行い、可変容量素子の切り替えスイッチの数と回路面積の増大を小さくする。調整誤差については、調整期待値との差分を記憶素子で記憶し、その差分値が最小となる容量素子値を求めることにより影響を最小限に押さえることが可能となる。

(もっと読む)

広範囲かつダイナミックに再構成可能なクロックデータ回復アーキテクチャ

【課題】広範囲のデータレートに渡って動作可能なCDRアーキテクチャを提供する。

【解決手段】広範囲およびダイナミックにリプログラミング可能なCDRアークテクチャは、広範囲の動作周波数でシリアル入力データから埋め込まれたクロック信号を回復する。広範囲のデータレートをサポートするために、CDRアーキテクチャは、複数の動作パラメータを含む。これらのパラメータは、様々な先行/後行の分割器設定、チャージポンプ電流、ループフィルタおよび帯域幅選択、および、VCOギアを含む。パラメータは、回路またはPLDのパワーダウンなしに、ダイナミックにリプログラミングされ得る。これは、CDR回路が、様々な規格とプロトコルとの間を迅速に切り替えることを可能にする。

(もっと読む)

自動周波数制御ループ回路

【課題】高い精密度を有しながら周波数を広帯域で発振させることができる自動周波数制御ループ回路を提供すること。

【解決手段】基準周波数を発生させるクロック発振部と、基準周波数を第1分周比で分周する第1分周器、発振周波数を第2分周比で分周する第2分周器、第1分周器によって分周された第1分周周波数と第2分周器によって分周された第2分周周波数との間の位相差を検出する位相検出器、位相差に対応して発振周波数を発生させる電圧制御発振器と、入力周波数と発振周波数に対応して出力周波数を出力する周波数変換器を含む周波数合成部と、出力周波数を設定周波数と比較して誤差を検出する誤差検出器、誤差を積分する積分器と、積分器の積分値に対応する制御信号を計算する演算器を含む復調部とを含み、制御信号に応じて第1分周比及び第2分周比を変更して誤差を補正することを特徴とする。

(もっと読む)

PLL周波数シンセサイザおよびこれを用いた集積回路ならびに通信装置

【課題】 PLL周波数シンセサイザの小型化を実現する。

【解決手段】 本発明のPLL周波数シンセサイザは、電圧制御発振器と、分周器と、位相比較器と、ローパスフィルタとを備えるPLL周波数シンセサイザにおいて、ロック検出器をさらに備え、基準電圧選択回路は、ロック検出信号ならびに制御電圧から基準電圧ならびに切替信号を出力し、電圧制御発振器は、基準電圧、切替信号、ならびに、ローパスフィルタからの上記制御電圧を元に出力された発振周波数の可変範囲である上限値および下限値およびに発振周波数可変範囲の中央値である中心周波数を決定するので、発振周波数の広い可変範囲と、狭い可変範囲を同じ回路を共用して切り替えることができ、発振周波数の可変範囲の中心周波数を電圧制御によって変更することで、同種の回路を複数構成する場合にくらべて設置面積が少なくて済む。

(もっと読む)

81 - 100 / 127

[ Back to top ]