Fターム[5J106KK08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 性能の向上 (885) | キャプチャーレンジの拡大 (127)

Fターム[5J106KK08]に分類される特許

61 - 80 / 127

信号分配装置

【課題】分周器の広帯域かつ低電圧動作を保障する。

【解決手段】信号分配装置は、第2制御信号に従って動作し、参照周波数に従って発振周波数を調整する調整部を有する位相同期ループ回路101と、電流源負荷を有し、前記調整部によって調整された発振周波数を分周してI/Q信号を生成する分周器102と、第1制御信号に従って自走発振周波数を生成する自走発振周波数生成器105と、前記参照周波数と前記自走発振周波数を比較する比較部103A及び前記比較部103Aの比較結果に従って前記第1制御信号又は前記第2制御信号を生成する制御部103Bを有する自走発振周波数制御回路103と、前記分周器102によって生成された前記I/Q信号を用いて送信又は受信を行う通信回路104と、を備えている。

(もっと読む)

従属同期クロック信号生成装置

【課題】従属同期クロック信号生成装置に関し、従属同期用クロック信号の系切替え時に瞬断なくクロック信号を供給し、擾乱の無い装置供給用クロック信号を供給する。

【解決手段】外部から2系統の従属同期クロック信号を入力し、該従属同期クロック信号の1周期分の信号の開始部分を検出してハイレベル信号を出力し、該従属同期クロック信号の1周期未満のタイミングでローレベル信号を出力する2系統のクロック信号生成部(#0)1−1,(#1)1−2と、該クロック信号生成部から出力される信号の論理和信号をクロック信号としてPLO部6−7出力する論理和信号出力部1−3を備える。クロック信号生成部は、内部自走クロック源1−4のクロックをカウントして従属同期クロック信号の1周期未満のタイミングでローレベル信号をフリップフロップ回路1−12,1−22のリセット端子に入力して強制的にローレベル信号を出力させる。

(もっと読む)

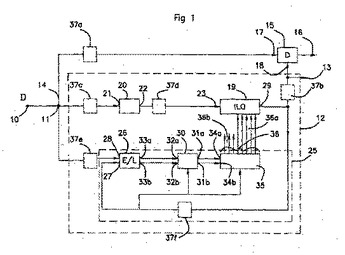

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

シンボル同期回路

【課題】同期回路が1系統で、温度変化等によるクロック位相ずれの増大を防止できるシンボル同期回路を提供すること。

【解決手段】シンボル同期回路は、戻し段数決定部104を有し、可変遅延器101から左端信号109及び右端信号110を取り出す。左端信号109と右端信号110は、クロック信号107をそれぞれ異なる遅延段数により遅延させた信号である。遅延段数とは、クロック信号107を遅らせるために通過させた遅延素子の個数を意味する。戻し段数決定部104は、左端信号109と右端信号110の位相差がクロック周期の自然数倍の時間に最も近くなるときの、左端信号109と右端信号110のそれぞれの遅延段数の差を、戻し段数として算出する。巡回制御部103は、戻し段数決定部104から指示される段数に基づいて戻し処理を行なう。

(もっと読む)

位相同期回路

【課題】 簡易な手段で、PLL回路の入力信号と出力信号との位相差(定常位相誤差)を小さくし、同期範囲を拡大すること。

【解決手段】 PLL回路は、基準信号と比較信号との位相差を検出する位相比較器と、ループフィルタと、制御電圧に応じた周波数の出力信号を生成する電圧制御発振器と、出力信号から生成した比較信号を位相比較器にフィードバックする比較信号生成回路とを有している。さらに、PLL回路は、基準信号と比較信号との周波数が同期しているときに、基準信号の位相に対する比較信号の位相の遅延量を検出する誤差検出回路を有している。例えば、比較信号生成回路は、誤差検出回路により検出された遅延量に応じて、出力信号を遅延させ、出力信号から遅延させた信号を比較信号として位相比較器にフィードバックする。

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

PLL回路

【課題】低ジッターを維持しつつ、発振周波数範囲を拡大できるPLL回路を提供する。

【解決手段】PLL回路は、レギュレータ21と、位相周波数比較器22と、チャージポンプ23と、所定の制御信号を前記レギュレータに出力し、前記レギュレータの出力電圧を制御する電源電圧制御部24と、電源投入または所定のテストモードの際に、前記位相周波数比較器の出力を、前記チャージポンプから前記電源電圧制御部に切り替える第1経路設定部25-1と、第1制御電圧を出力するロウパスフィルタ23と、第2制御電圧を出力する制御電圧発生回路27と、前記第1、第2制御電圧および前記レギュレータの出力電圧に応じて出力クロックを出力する電圧制御発振器28と、前記電源投入または前記所定のテストモードの際に、前記電圧制御発振器の制御端子に入力する制御電圧を、前記第1制御電圧から前記第2制御電圧に切り替える第2経路設定部25-2と、分周器29とを具備する。

(もっと読む)

半導体集積回路装置

【課題】PLL回路等を代表とする各種フィードバックシステムの高精度化を実現する。

【解決手段】例えば、PLL回路内のチャージポンプ回路CPにおいて、電源電圧Vddと出力ノードOUTの間に直列3段接続のPMOSトランジスタTp80〜Tp82を設け、接地電圧VssとOUTの間に直列3段接続のNMOSトランジスタTn82〜Tp80を設ける。そして、Tp81およびTn81は、パルス信号PLS1によってVdd又はVssとOUTの間を導通させる際にオンに駆動し、Tp80およびTn80は、パルス信号PLS2によってこの導通を遮断させる際にオフに駆動する。そうすると、PLS1と一方のエッジとPLS2の一方のエッジとの時間差によってこの導通時間を設定できるため、短い導通時間を設定可能となり、チャージポンプ回路の電流量を高精度に制御可能となる。

(もっと読む)

クロック発生装置

【課題】PLL回路を使用し、より幅広い環境変動に適応して周波数を一定値にロックすることのできるクロック発生装置を得る。

【解決手段】クロック発生装置200は、基本的に同一構成で共にLC型VCOを備えた第1および第2のPLL回路201、202を備えている。マスタ側の第1のPLL回路201の第1のVCO2241に加わる第1の制御電圧2281は基準電圧検出回路212で3つの固定値と比較され、その結果に応じて第2のPLL回路202の容量スイッチ247、257の値を調整しておいて、出力セレクタ207で第1のPLL回路201から第2のPLL回路202にクロックの選択を切り替える。

(もっと読む)

周波数合成回路、通信装置、周波数制御方法、周波数制御回路、周波数制御システム、およびコンピュータ読取可能な記録媒体

【課題】周波数合成器(200)の可変発振器(202)の出力信号の周波数を制御するシステムを提供する。

【解決手段】可変発振器(202)と周波数制御回路(208)を有する。可変発振器(202)は予め定められた周波数を有する出力信号を生成するために構成される。また可変発振器(202)は周波数制御回路(208)によって制御される複数の動作状態によって構成される。可変発振器(202)の動作状態のそれぞれは、可変発振器(202)の出力信号のための別個の周波数を決定する。周波数制御回路(208)は、可変発振器(202)の出力信号を受信し、予め定められた周波数に最も近い出力信号のための別個の周波数を決定する。また、周波数制御回路(208)は、可変発振器(202)へ、予め定められた周波数に最も近い別個の周波数に対応する動作状態へ、可変発振器(202)を移行するために構成される制御信号を供給する。

(もっと読む)

カスコードバイアスされたチャージポンプ

【課題】チャージポンプの線形動作範囲を広くする。

【解決手段】一実施形態によるチャージポンプは、アップ(UP)信号を受け取り、そのUP信号の受け取りに応答して正の電源から出力ノードに対応する出力電流を送るように動作可能な第1の入力トランジスタを含む。このチャージポンプは、ダウン(DN)信号を受け取り、そのDN信号の受け取りに応答して、第2の対応する出力電流を負の電源から出力ノードに送るように動作可能な第2の入力トランジスタをさらに含む。また、このチャージポンプは、第1の入力トランジスタと出力ノードとの間の第1の電流経路に配置された第1のカスコードトランジスタと第2のカスコードトランジスタを含み、第2の入力トランジスタと出力ノードとの間の第2の電流経路に配置された第3のカスコードトランジスタと第4のカスコードトランジスタを含む。このチャージポンプは、第1、第2、第3及び第4のカスコードトランジスタのゲートに結合した電流ミラーをさらに含む。

(もっと読む)

CASレイテンシを利用してロッキングレゾリューション調節が可能な遅延同期ループ回路

【課題】単位遅延器の数を増やさなくとも広いロッキング範囲を有し、またロッキングサイクル時間を減らせる遅延同期ループ回路を提供する。

【解決手段】遅延ライン、位相検出器、制御回路を備える。遅延ラインは、直列連結された多数の単位遅延器を含んで制御信号に応答して選択される単位遅延器を通じて外部クロック信号を遅延させる。位相検出器は、前記外部クロック信号の位相と前記遅延ラインから出力される内部クロック信号の位相とを比較し、外部クロック信号と遅延ラインから出力される内部クロック信号間の位相差を検出する。制御回路は、前記位相検出器の出力信号に応答して前記制御信号を発して遅延制御信号に応答して前記遅延ラインのロッキング位相ステップを可変にする。

(もっと読む)

マイクロプロセッサー用の位相ロックループの動的周波数スケーリングの方法と装置

複数個の発振器複合体を使用する位相ロックループが開示される。位相ロックループは、クロック出力と、出力信号を発生するように動作可能な複数個の発振器複合体を含んでいる。位相ロックループは、さらに、複数個の発振器複合体のうち1個の出力信号を選択して、クロック出力に結合するように構成された制御ロジックを含んでいる。  (もっと読む)

(もっと読む)

電圧制御発振回路

【課題】電圧電流変換部の制御電圧入力用MOSトランジスタにデプレッション型を使用した際に発生する発振周波数(バイアス電流)オフセットの製造プロセスばらつきが補正された電圧制御発振回路を提供する。

【解決手段】電圧制御発振回路1は、制御力電圧がゲートに入力される第1のデプレッション型MOSトランジスタ13と、その第1のデプレッション型MOSトランジスタ13のゲート・ソース間電圧が0Vのときのオフセットを補償する第2のデプレッション型MOSトランジスタ15を有し、制御電圧に応じたバイアス電流を発生する電圧電流変換回路3を備える。

(もっと読む)

電圧制御発振器、PLL回路

【課題】 低周波の発振信号であっても安定して出力することが可能な電圧制御発振器及びPLL回路を提供する。

【解決手段】 本発明に係る電圧制御発振器1は、インダクタ4及び可変キャパシタ5を有するLC共振回路2と、複数の負性抵抗回路NR1、NR2、…、NRnを備える。各負性抵抗回路NR1、NR2、…、NRnは、定電流源CG1、CG2、…、CGnを介して夫々接地線と接続される構成であり、各定電流源は、夫々個別に導通状態(一定電流を流す状態)と非導通状態(開放された状態)との間で切換制御が可能に構成されており、本発明に係る電圧制御発振器1は、これらの各定電流源の導通制御を行うための制御手段7を備える構成である。

(もっと読む)

フィードフォワード分割器を有する適応帯域幅位相ロックループ

【課題】位相ロックループを提供する。

【解決手段】一部の実施形態では、チップは、第1及び第2の電圧制御式発振器(VCO)出力信号を供給するための第1及び第2のVCOと、第1及び第2VCO出力信号の第1及び第2の周波数を第1及び第2の分周率によって分割するための第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)を含む。チップはまた、第1及び第2分周率を選択するための位相ロックループ制御回路を含む。他の実施形態も説明して特許請求する。

(もっと読む)

チャージポンプがない位相固定ループ回路及びこれを含む集積回路

【課題】チャージポンプがない位相固定ループ及びこれを含む集積回路を提供する。

【解決手段】チャージポンプがない位相固定ループは、位相周波数検出器及びループフィルタを含む。ループフィルタは、プルアップ抵抗、プルアップ抵抗と直列に連結されたプルダウン抵抗及びプルアップ抵抗とプルダウン抵抗の連結ノードと連結された電気容量部を含み、位相周波数検出器から第1制御信号が入力される時に提供される第1基準電圧の入力を受けてプルアップ抵抗と電気容量部によって形成されたパスを通じて電気容量部を充電させ、位相周波数検出器から第2制御信号が入力される時に提供される第1基準電圧より低い第2基準電圧の入力を受けてプルダウン抵抗と電気容量部によって形成されたパスを通じて電気容量部を放電させ、充電された又は放電された電気容量部に基づいて生成された制御電圧を出力する。

(もっと読む)

VCO回路

【課題】可変周波数範囲の広域化を可能にしつつ高い位相雑音特性を備えるVCO回路を提供する。

【解決手段】上記課題を解決するために、VCO回路100に、バッファ回路B11、P型MOSトランジスタQ11及びキャパシタC11からなるバイアス回路101と、アンプA11と、インダクタL11、可変キャパシタC12、及びスイッチ付きキャパシタC13、C14、・・・からなる共振回路102と、を備える。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】電圧制御発振器の出力周波数範囲が狭帯域であるか広帯域であるかに関わらず、所望の周波数で位相同期を実現することができるようにする。

【解決手段】高周波信号Do(t)と局部発振信号Dp(t)の周波数を混合して、相互に90度の位相差を有する第1の低周波帰還信号Dv1(t)と第2の低周波帰還信号Dv2(t)を出力する周波数混合手段を設け、位相比較器9,10が第1及び第2の低周波帰還信号Dv1(t),Dv2(t)と第1及び第2の基準信号Dr1(t),Dr2(t)との位相を比較して、位相の比較結果を示す第1及び第2の位相比較信号De1(t),De2(t)を出力する。

(もっと読む)

位相比較信号処理回路

【課題】位相比較回路の出力矩形波信号の処理する際に、簡単な回路構成を有し、PLLで引込み可能な周波数幅を拡げ、同期時間を短縮できる位相比較信号処理回路を提供する。

【解決手段】入力矩形波信号を双極性信号に変換する電圧シフタ2、入力矩形波信号のレベル変化時に制御パルス信号を発生する制御パルス信号発生器7、制御パルス信号の到来時に積分値をリセットし、その後双極性信号を積分して積分値を出力する積分回路3、積分値のリセット時のレベル変化分を微分パルスとして出力する微分回路4、制御パルス信号の到来時に微分パルスを出力するゲート回路6、前記保持回路は最新の入力微分パルスレベルを保持し、微分パルスレベルの更新時にその微分パルスレベルが保持されるように保持電圧値が順次変化する保持信号を形成するホールド回路8を備え、この保持信号を次段のループフィルタに供給する。

(もっと読む)

61 - 80 / 127

[ Back to top ]