Fターム[5J106LL04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | フィルタ回路 (45)

Fターム[5J106LL04]に分類される特許

1 - 20 / 45

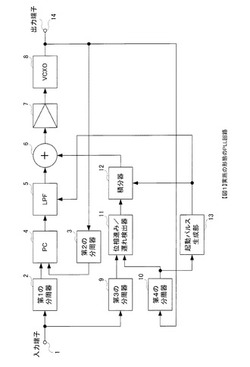

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

PONシステムの局側装置、クロックデータ再生回路及びクロック再生方法

【課題】 想定外の伝送レートの入力信号が入力されても、次の入力信号に対するクロックとデータの再生を適切かつ高速に行えるようにする。

【解決手段】 本発明は、位相ロックループと周波数ロックループのうちのいずれか一方に切り替え可能なデュアルループ方式のクロックデータ再生回路50に関する。この再生回路50は、各ループのうちのいずれか一方を選択的に動作させるセレクタ53と、各ループにおいてそれぞれ制御電圧を発生させ、周波数ロックループの動作中に制御電圧をいったん入力信号の到来前の中立状態に戻す電圧発生回路54と、を備える。

(もっと読む)

周波数シンセサイザ

【課題】 スプリアスを低減すると共にDDS回路本来の出力周波数帯域を十分に活用して所望の基準周波数信号を出力することができる周波数シンセサイザを提供する。

【解決手段】 DDS回路22の出力に、帯域制御電圧に応じて通過周波数帯域を可変とする帯域可変型フィルタ24を備え、制御回路21が、周波数の値と帯域制御電圧の値とを対応付けた制御電圧テーブルを記憶しており、外部からDDS回路22の出力周波数が設定されると、制御電圧テーブルを参照して、設定された出力周波数に対応する制御電圧を帯域可変型フィルタ24に出力して、帯域可変型フィルタ24をDDS回路からの出力周波数に応じたフィルタ特性としてスプリアス成分を除去する周波数シンセサイザとしている。

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

PLL回路および電子機器

【課題】PLL回路の回路規模の増大を抑制しながら、安定性と周波数引込み速さとを独立に設定可能にする。

【解決手段】PLL回路1は、信号を遅延する遅延閉ループ19により発振信号を生成するリング発振部2と、位相比較部3、チャージポンプ4、平滑フィルタ5、平滑電流源6、遅れ成分フィルタ7、および補正電流源8を有する。遅れ成分フィルタ7は、平滑フィルタ5と並列にチャージポンプ4の出力に接続され、チャージポンプ4の出力信号に含まれる応答遅れ成分を抽出する。リング発振部2は、遅延閉ループ19において信号を遅延する遅延部として、平滑電流源6および補正電流源8の少なくとも一方の電流源から供給される電流により動作して信号を遅延する遅延部11を有する。

(もっと読む)

PLL回路

【課題】ループ内の無駄時間を補償し、所望の特性を取得可能なPLL回路を提供する。

【解決手段】メインパス110は、入力段に配置され、入力信号と実信号との位相検出を行うフェーズディテクタ111と、フェーズディテクタの出力側に配置され、ループの応答特性を決めるためのループフィルタ113と、ループフィルタの出力信号に応じた周波数で発振し、発振信号を実信号としてメイン帰還パスに出力する制御発振器114と、を含み、ローカル帰還パス130は、ループフィルタの出力が入力され、制御発振器のレプリカとして機能するレプリカ部131と、レプリカ部の出力を一巡無駄時間分遅延させる遅延部132と、遅延部の入力信号と出力信号の差分を得る第1の減算器133と、第1の減算部の出力信号からループフィルタ中の内部信号を定数倍した信号を減算し、ループフィルタの入力側に出力する第2の減算器136と、を含む。

(もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの帯域幅切り替え時の周波数変動を低減することによって、高速に周波数切り替えが可能なPLL周波数シンセサイザを提供する。

【解決手段】PLL周波数シンセサイザは、基準発振器と、分周器と、位相比較器と、チャージポンプと、ループフィルタと、VCOとを備えている。ループフィルタは、チャージポンプとVCOとの間に互いに並列に設けられた第1経路および第2経路と、第1経路上に設けられた第1スイッチと、第2経路上に設けられた第2スイッチとを含み、第1スイッチおよび第2スイッチの双方がオフ状態であるとしたときに、それぞれの寄生容量が互いに同じであり、第1経路および第2経路それぞれの抵抗値が互いに異なり、第1スイッチおよび第2スイッチの一方がオン状態であるとき、他方がオフ状態となる。

(もっと読む)

PLL発振回路

【課題】ループ中に、バッファアンプや逓倍回路と、不要周波数成分を除去するフィルタを含むPLL発振回路において、広帯域に発振周波数を変化させた場合でも、簡単な構成によって、発振ループ中の不要周波数信号成分を除去し、安定化した発振出力を得ることが可能なPLL発振回路を提供する。

【解決手段】PLL発振回路において、電圧制御発振器と位相比較器との間に不要周波数成分を除去するフィルタ回路を挿入するとともに、電圧制御発振器の制御電圧情報を記憶した制御電圧メモリの出力信号によって、上記フィルタ回路の通過周波数帯域を変更するように構成する。

(もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

フラクショナル−N方式位相同期ループ形周波数シンセサイザ

【課題】 位相比較器の位相差に対する検波電圧特性の非線形性によって、F−N方式PLL周波数シンセサイザ出力に発生するスプリアスの抑圧を実現することを目的とする。

【解決手段】 高周波信号を生成する電圧制御発振器と、前記高周波信号より同期信号を生成する可変分周器と、基準信号を生成する基準発振源と、前記基準信号より位相差を有する2つの基準信号を生成する基準信号生成手段と、前記それぞれの基準信号と前記同期信号を入力とし、第1と第2の位相比較信号を出力する第1の位相比較器と、第3と第4の位相比較信号を出力する第2の位相比較器と、前記第1と第2の位相比較信号を差分した差分結果と、前記第3と第4の位相比較信号を差分した差分結果を合成して平滑化した合成信号を出力するループフィルタとを備え、前記合成信号に応じて電圧制御発振器を制御することにより前記高周波信号を生成する。

(もっと読む)

位相ロックループ回路及び遅延ロックループ回路

【課題】ジッタの増加を防止し、カットオフ周波数の変動を防止することができる位相ロックループ回路及び遅延ロックループ回路を提供することを課題とする。

【解決手段】リファレンス信号とフィードバック信号との位相を比較し、その位相差を示す位相差信号を出力する位相比較器(101)と、前記位相差信号に応じたチャージポンプ電流を出力するチャージポンプ(102)と、抵抗及び容量を含み、前記チャージポンプ電流を平滑化して制御電圧に変換するローパスフィルタ(103)と、前記制御電圧に応じた周波数の発振信号を生成する電圧制御発振器(104)と、前記発振信号を分周した分周信号を生成し、前記分周信号を前記フィードバック信号として前記位相比較器に出力する分周器(105)とを有し、前記ローパスフィルタ内の抵抗は、前記制御電圧に応じて変化する可変抵抗であることを特徴とする位相ロックループ回路が提供される。

(もっと読む)

半導体集積回路

【課題】ロック動作の初期において高速引き込みを可能とすると伴に入力信号ジッタや入力雑音の影響の小さなディジタルフェーズロックドループを提供すること。

【解決手段】半導体集積回路は、位相比較器10、11、ディジタルループフィルタ12、ディジタル制御発振器13、フィードバック分周器14を含むディジタルフェーズロックドループADPLLを具備する。ディジタルループフィルタ12は、第1ゲインαを有して位相比較器10、11のディジタル位相出力信号θが供給される比例パス12aと、第2ゲインβを有して信号θが供給される積分パス12b、12c、12dと、信号θの大きさを判定する判定器12g、12hを含む。ディジタル位相出力信号θの大きさが所定の基準値θthよりも大きい場合には、判定器12g、12hは第2ゲインβと第1ゲインαとの比β/αを大に設定する。

(もっと読む)

位相ロックループ回路

【課題】回路面積の増大、ピン数の浪費、入出力位相誤差特性の悪化を招くことなく、ループバンド幅の狭い位相ロックループ回路を提供する。

【解決手段】位相ロックループ回路は、フィルタ回路と電圧制御発振回路との間に設けられ、フィルタ回路から供給される第1のアナログ電圧のゲインを1/n(nは1よりも大きい値)に抑制した第2のアナログ電圧を電圧制御発振回路に供給するゲイン抑制回路を備える。ゲイン抑制回路は、第1のアナログ電圧が、その可動範囲の上限電圧もしくは下限電圧に到達している期間は、第2のアナログ電圧の可動範囲の上限電圧が、最大で電圧制御発振回路の入力電圧範囲の上限電圧になるまで一定の比率で平行移動させる、もしくは、第2のアナログ電圧の可動範囲の下限電圧が、最小で電圧制御発振回路の入力電圧範囲の下限電圧になるまで一定の比率で平行移動させる。

(もっと読む)

CDR回路

【課題】カットオフ周波数をアダプティブに制御する。

【解決手段】CDR回路40には、位相検出器1、シリアル−パラレル変換器2、デジタルフィルタ3、位相制御器4、位相補間器5、積分器6、マルチプレクサ7、及びマルチプレクサ8が設けられる。積分器6は、デジタルフィルタ3で計算されたアーリィ(Early)信号[0:n]−レート(Late)信号[0:n]の符号の情報信号である出力信号SFを入力し、この信号を一定期間Mでモニターし、遅延要素と加算器とを用いて周波数ジッタとして積分する。CDR回路40は、デジタルフィルタの閾値と位相補間器の位相ステップを最適な値に変更して、カットオフ周波数をアダプティブに制御する。

(もっと読む)

PLL周波数シンセサイザ

【課題】ループフィルタの帯域幅切換時の周波数変動を低減することによって、高速に周波数切換が可能なPLL周波数シンセサイザを提供する。

【解決手段】本発明の一実施形態のPLL周波数シンセサイザ1は、分周器30と、位相比較器40と、チャージポンプ50と、ループフィルタ60と、電圧制御発振器70と、切換スイッチ(切換部80の内部)とを備える。ループフィルタ60は、半導体基板上の基準電位を接地電位とし、切換スイッチは、半導体基板2上に形成され、ループフィルタ60の時定数を切り換えるためにループフィルタ60の中間ノードと半導体基板2上の基準電位とを接続するか否かを切り換える。

(もっと読む)

チャージポンプがない位相固定ループ回路及びこれを含む集積回路

【課題】チャージポンプがない位相固定ループ及びこれを含む集積回路を提供する。

【解決手段】チャージポンプがない位相固定ループは、位相周波数検出器及びループフィルタを含む。ループフィルタは、プルアップ抵抗、プルアップ抵抗と直列に連結されたプルダウン抵抗及びプルアップ抵抗とプルダウン抵抗の連結ノードと連結された電気容量部を含み、位相周波数検出器から第1制御信号が入力される時に提供される第1基準電圧の入力を受けてプルアップ抵抗と電気容量部によって形成されたパスを通じて電気容量部を充電させ、位相周波数検出器から第2制御信号が入力される時に提供される第1基準電圧より低い第2基準電圧の入力を受けてプルダウン抵抗と電気容量部によって形成されたパスを通じて電気容量部を放電させ、充電された又は放電された電気容量部に基づいて生成された制御電圧を出力する。

(もっと読む)

移相回路

【課題】 移相量を常に一定に制御可能とし、電源電圧変動時等の影響の低減、素子バラツキの影響を低減する移相回路の提供。

【解決手段】基準周波数信号が入力されて2分配され一方の信号は位相比較器102の一方の入力となり、他方の信号は移相器101を介してその位相が移相された後に、前記位相比較器102の他方の入力となり、位相比較器102の出力はループフィルタ(LPF)103を介して差動増幅器104の一方の入力端子に入力され、差動増幅器104の出力信号により移相器101の移相量が制御されるPLLループを有し、差動増幅器104の他方の入力端子に印加される基準電圧により前記移相器101での移相量が定まる。

(もっと読む)

位相同期ループ回路及び信号発生装置

【課題】回路規模の大幅な増大を招かずに、早期に所望の周波数を有する信号を出力することができる位相同期ループ回路及び当該回路を備える信号発生装置を提供する。

【解決手段】位相同期ループ回路1は、PLL部10と、PLL部10から出力される信号S1の周波数をPLL部10の同調周波数帯域に高速に引き込むためのプリチューン信号S26を生成するプリチューン信号生成部20とを備えている。プリチューン信号生成部20は、PLL部10から出力される信号S1の周波数をカウントするカウンタ21、カウンタ21でカウントされた信号S1の周波数とプリチューン周波数との誤差を示す誤差値が所定の閾値よりも小であるか否かを判定する誤差判定部23、及び誤差判定部23の判定によって誤差値が所定の閾値よりも小となるときのPLL部10に与えられるプリチューン信号S26を記憶するメモリ25を備える。

(もっと読む)

PLL回路を備えた半導体集積回路

【課題】製造条件によるデバイス特性のバラツキや使用温度、電源電圧などの使用環境によるデバイス特性のバラツキがある場合でも、未然にVCO6の発振停止を防止すると共に、安定的に起動を行うことができるPLL回路を備えた半導体集積回路を提供する。

【解決手段】PLL回路2の過渡応答時間とデバイス及び使用環境に応じたチャージポンプ4の電流値を、事前にメモリ10に保存しておき、マイコン9からの制御信号ICPctlに基き、チャージポンプ4は、PLL回路2起動時から発振安定時までの過渡応答期間中は、電流値をメモリ10の設定情報に従って低減させる。

(もっと読む)

周波数シンセサイザおよびこれに用いるループフィルタ

【課題】コンデンサの容量値を小さくしてループフィルタのIC化を容易にし、かつ、周波数シンセサイザの同期状態に関係なくC/N特性やスプリアス特性を改善できるようにする。

【解決手段】並列接続された複数のコンデンサC1〜Cnと、これらのチャージ/ディスチャージ動作をパイプライン処理として行うように切り替えを行うスイッチSW11〜SW1n,SW21〜SW2nと、複数のコンデンサC1〜Cnを備えた並列回路の出力側に接続されたコンデンサCHとを備えてLPF15を構成し、各コンデンサC1〜Cnに順次チャージされた電荷が並列回路の出力として得られ、それがコンデンサCHに順次に蓄積されるようにすることにより、各コンデンサC1〜Cn,CHの容量値を小さくすることにより時定数が小さくなっても、回路全体として大きな時定数を実現できるようにする。

(もっと読む)

1 - 20 / 45

[ Back to top ]