Fターム[5J106PP01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 出力周波数可変方式 (219) | 基準周波数の変化によるもの (24)

Fターム[5J106PP01]に分類される特許

1 - 20 / 24

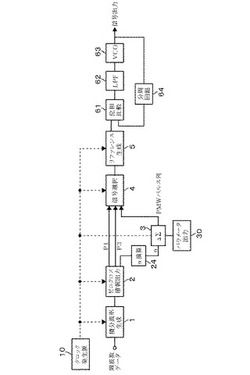

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

多周波発振器

【課題】発振周波数の安定性及び周波数の過渡応答性において従来よりも優れた多周波発振器を提供する。

【解決手段】水晶振動子を少なくとも備え、変調信号発生器5から入力された変調信号によって水晶振動子の発振周波数を調整する基準信号発生器12と、位相比較器6、ループフィルタ7及び電圧制御発振器8を少なくとも備え、基準信号発生器11の出力と電圧制御発振器8の出力とを位相比較器6で位相比較するPLL11とを具備する。

(もっと読む)

周波数シンセサイザ及び周波数合成方法

【課題】広い帯域幅、高い周波数分解能及び低い位相ノイズを提供する周波数シンセサイザ及び対応する周波数合成方法を提供する。

【解決手段】第1のリファレンス信号を提供するリファレンス信号源22と、合成周波数出力信号を所定の周波数で生成する周波数信号生成部24と、前記合成周波数出力信号を周波数チューニング信号とミキシングして、ミキシング信号46を出力するミキシング部26と、前記周波数チューニング信号を提供する周波数チューニング部28とを備え、前記周波数チューニング部28は、前記周波数チューニング信号を交互に提供する、第1のサブ周波数チューニング部及び第2のサブ周波数チューニング部を有し、前記ミキシング信号から所望の周波数レンジを選択して周波数シンセサイザ出力信号を出力する周波数選択部30を備えた。

(もっと読む)

周波数シンセサイザ

【課題】位相雑音を改善することのできる周波数シンセサイザを提供すること。

【解決手段】周波数設定部により設定された周波数の正弦波信号を設定信号出力部からディジタル信号として出力し、これをD/A変換する。ここから出力された正弦波信号と電圧制御発振部の出力周波数に対応する周波数の正弦波信号と、前記D/A変換部からの正弦波信号と、の差分を差動増幅器で増幅し、増幅された信号をA/D変換部を介して、既述の両正弦波信号の位相差を取り出す手段に入力する。この位相差を積分した信号に相当する電圧を電圧制御発振器に制御電圧として入力する。そして差動増幅器の利得をA/D変換部の位相雑音劣化の最大値よりも大きく設定し、これによりA/D変換部の位相雑音劣化をキャンセルする。

(もっと読む)

PLL回路

【課題】 全てのチャンネルについてスプリアス特性が良好なVCO出力を得ることができ、温度変化による特性変動を抑えることができるPLL回路を提供する。

【解決手段】 制御回路3が、温度センサ31と、温度に応じてチャンネル番号毎に電圧制御発振器の出力におけるスプリアス特性が良好となる分周比を記憶した分周比テーブル32とを備え、温度センサ31で検出された温度及び入力されたチャンネル番号に対応する分周比を分周比テーブル32から読み取って、PLLIC2に設定すると共に、DDS回路(基準周波数生成回路)4にチャンネル番号と分周比とを設定し、DDS回路4が、チャンネル番号と分周比に基いて基準周波数の値を算出して、当該値に対応する基準周波数を生成するPLL回路としている。

(もっと読む)

デジタル制御型の周波数発生装置

【課題】本発明は、従来の周波数発生装置から共振チップを取り替えずに、その出力のクロック信号を需要の周波数に自由に調整することができる周波数発生装置を提供する。

【解決手段】所定の振動周波数を有する第1クロック信号を発生する発振器モジュールと、操作により、需要の周波数に対応して制御信号を発生するプログラマブル制御モジュールと、前記発振器モジュールからの前記第1クロック信号と前記プログラマブル制御モジュールからの前記制御信号とを受信し、前記両信号に基づいて前記需要の周波数を有する第2クロック信号を発生することができるように前記発振器モジュールと前記プログラマブル制御モジュールとに電気的に連結されている直接デジタル周波数シンセサイザとからなっていることを特徴とするデジタル制御型の周波数発生装置を提供する。

(もっと読む)

分数分割電荷補償手段を有する周波数シンセサイザ

【課題】分数−N補償法で用いられる電荷ポンプを容易に整合し、分数分割によって導入された望ましくない周波数成分を濾波する。

【解決手段】VCO周波数分割器309と基準周波数信号303との間の位相不整合の分数−NPLLにおける補償が可変電荷ポンプ装置307により行われる。移相比較器305は、電荷ポンプ装置の電荷ポンプのいくつかを早くオンにし、残りの電荷ポンプを遅れてオンにするために補償論理501を有する。このプロセスは、部分電荷を適切に補償するために正確な時点で等価電荷をオンにする。

(もっと読む)

周波数合成器および周波数合成装置

【課題】基準信号の周波数の実数倍の周波数を持ちジッタの少ないデジタル信号を整数PLLとデジタル回路のみを用いて生成する。

【解決手段】実数である周期指定値をデルタ・シグマ変調器を通してジッタの低周波成分を抑制した整数分周数列を発生させ、その分周数列で基準信号を分周する。その分周出力信号に対して整数PLLによりジッタを除去することにより所望の信号を得る。また、前記デルタ・シグマ変調器では、分周器出力において理想的な信号の立ち上がりのタイミングと実際の立ち上がりのタイミングの誤差を算出し、その誤差に対してデジタルフィルタを通して分周数にフィードバック補償を行う。

(もっと読む)

搬送波生成回路

【課題】広帯域にわたって周波数成分の劣化がない搬送波を生成する搬送波生成回路を提供する。

【解決手段】指定された搬送波の周波数に応じて設定を変更する機能を設け、スプリアスが発生しない設定値に切り替える。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

周波数シンセサイザ装置及びその制御値決定方法

【課題】特性に優れた発振出力を得る。

【解決手段】 発振周波数の粗調整のための第1の可変容量部及び前記発振周波数の微調整のための第2の可変容量部によって前記発振周波数が可変の電圧制御発振器14と、前記第1及び第2の可変容量部を制御して前記電圧制御発振器の発振周波数を所望の周波数にするPLL回路14と、前記粗調整時において前記第2の可変容量部の容量を制御するための制御値を記憶するメモリ13と、を具備したことを特徴とする。

(もっと読む)

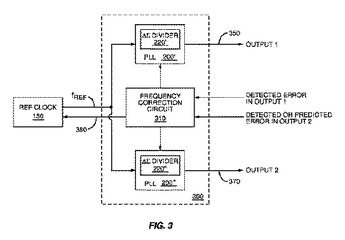

多出力周波数シンセサイザにおける周波数制御のための装置と方法

共通の基準周波数信号に位相同期した2つ以上の信号を合成(シンセサイズ)するための方法と回路とを開示する。1つの実施例では、その方法は、第1と第2の位相同期ループ回路(200′,200″)を使用して、基準クロック信号に位相同期する第1と第2の出力信号(350,370)を生成する工程を備える。第1の出力信号において検出された周波数誤差に応じて、第1の出力信号(350)は、第1の位相同期ループ回路における周波数分周比を調整することにより補正される。第2の出力信号(370)は、検出した周波数誤差から算出される調整パラメータを使用して、第2の位相同期ループ回路における周波数分周比を調整することにより、第1の出力信号への補正とは別個に補正される。別の代表的な方法では、第1と第2の出力信号は、第1と第2の位相同期ループ回路を使用して、上述したように生成される。第1の出力信号において検出された周波数誤差に応じて、第1の位相同期ループ回路における周波数分周比を調整し、制御信号(360)を生成して基準クロック信号の周波数を調整することにより、第1の出力信号が補正される。第2の出力信号(370)は共通の基準クロック信号から導出されるので、基準クロック周波数(FREF)に対する調整はまた、第2の出力信号の周波数も調整するであろう。いくつかの実施例においては、第2の位相同期ループ回路における周波数分周比を調整することにより、第2の出力信号(370)に対する付加的な調整を施すことができる。記述した方法を実施するための回路もまた開示される。  (もっと読む)

(もっと読む)

シンセサイザ

【課題】本発明は、周波数可変間隔(チャネルステップ)を細かく設定できると同時に位相比較周波数を高く設定し信号近傍の位相雑音を抑制することを目的とする。

【解決手段】本発明に係るシンセサイザは、高周波信号を発生させる第1のループ84に、第1のループ84の基準周波数を調整するための第2のループ85を設けたことを特徴とする。第2のループ85が第1のループ84の基準周波数を目的の周波数に調整する。第1のループ84は、第2のループ85の調整した基準周波数を用いて高周波信号を発生させる。第2のループ85が第1のループ84の基準周波数を微調整するので、第1のループ84の分周回路の分母を小さくしても周波数設定の分解能は粗くならない。第1のループ84の分周回路の分母を小さくしても、分解能を落とすことなく所望の周波数を発振する。

(もっと読む)

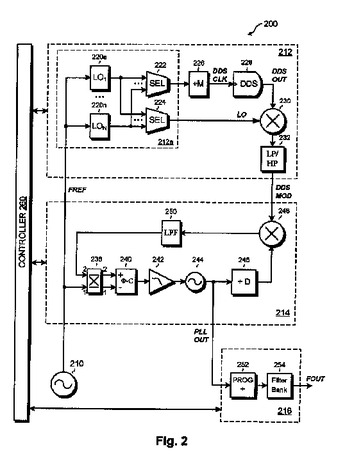

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

PLLシンセサイザ

【課題】 高速起動性、低消費電力性、定常状態における低スプリアス性を同時に満足させるPLLシンセサイザを構成する。

【解決手段】 可変整数分周器と可変分数分周器としての機能を有し、外部からの切換信号によりこの2つの分周器の機能を切り換える手段を含む切換型可変分周器と、外部からの切換信号により分周比の切り換えが可能な切換型基準分周器と、切換型可変分周器を可変分数分周器として機能させ、かつ切換型基準分周器の出力信号の周波数が電圧制御発振器の出力信号の周波数チャネル間隔より大きくなるようにその分周比を設定する分数分周モードと、切換型可変分周器を可変整数分周器として機能させ、かつ切換型基準分周器の出力信号の周波数が電圧制御発振器の出力信号の周波数チャネル間隔に等しくなるようにその分周比を設定する整数分周モードを切り換える切換制御回路を備える。

(もっと読む)

PLL周波数シンセサイザ回路

【課題】スプリアス信号がシンセサイザ回路の基準周波数信号に含まれると、発振出力信号のS/Nが著しく低下し、受信機の復調音声中に可聴音として出力される不具合が生じる。発明は、希望信号周波数近傍のスプリアスであっても、これを除去し得る機能を備えたPLL周波数シンセサイザ回路を提供することを目的とする。

【解決手段】電圧制御発振器、位相比較器、低域フィルタ、可変分周手段、を備えたPLL周波数シンセサイザ回路において、基準周波数信号に含まれる不要交流信号成分と振幅が同一で位相が逆相のレプリカ信号を生成し、該レプリカ信号によって前記不要交流信号成分を相殺除去するように構成する。

(もっと読む)

送信装置及び制御方法

【課題】FSK無線送信機10において、電圧制御発振器136へのFSK変調データのDCオフセットにもかかわらず、各論理値に対応する送信波の周波数を適格化する。

【解決手段】A/D変換器15は、FSK変調データの電圧をA/D変換して、CPU14へ送る。選択チャンネルの送信波の指示周波数をfoとする。また、FSK変調データの各論理値に対応して周波数軸方向上側及び下側に生じる送信波の周波数をそれぞれfu,flとし、fu,flの中心点の周波数を中心点周波数fmと呼ぶことにする。CPU14は、検出したDCオフセット量に基づいて、DDS12の設定データを調整することにより、DDS12の出力周波数を制御する。DDS12の出力周波数は、中心点周波数fmがfoとなるようなものに制御される。

(もっと読む)

位相比較回路およびそれを用いたPLL周波数シンセサイザ

【課題】高速に周波数切り換えが可能であり、且つ小型でスプリアスを低減することが可能な位相比較回路を提供する。

【解決手段】本発明の一実施形態に係る位相比較回路は、制御回路からの制御信号に基づいて、クロックを分数分周した分数分周信号を生成する分数分周器と、分数分周信号を整数分周した第1の整数分周信号を生成する第1の整数分周器と、基準クロックを整数分周した第2の整数分周信号を生成する第2の整数分周器と、切換信号に基づいて、分数分周信号と第1の整数分周信号とのいずれか一方を選択的に出力する第1の選択回路と、制御回路からの切換信号に基づいて、基準クロックと第2の整数分周信号とのいずれか一方を選択的に出力する第2の選択回路と、第1の選択回路からの出力信号と第2の選択回路からの出力信号との周波数差および位相差を表す比較信号を生成する位相比較器とを備えている。

(もっと読む)

半導体集積回路

【課題】アナログ回路の回路特性を切り替えて、その特性が所定の範囲内に入るように調整することができる半導体集積回路において、調整の精度を下げることなく調整時間を短縮し、低消費電力を実現する。

【解決手段】アナログ回路1の調整動作の終了後に、調整した結果である特性切替信号と、そのときの所望特性信号とを記憶回路4に記憶する。同じ所望特性信号で再びアナログ回路1の調整動作を行うときは、記憶回路4に記憶された前回の特性切替信号を初期値として設定してから調整動作を行う。

(もっと読む)

PLL回路、テレビジョン受信機、及びテレビジョン受信機のビート改善方法

【課題】 チャネル毎に基準発振周波数の必要変化量が異なる場合に、複数のチャネルでビート回避し得るPLL回路、テレビジョン受信機、及びテレビジョン受信機のビート改善方法を提供する。

【解決手段】 局部発振成分として基準となる周波数の信号を発振すべく、発振子32、容量及び発振子32の直列回路にて構成される基準信号発振回路40を備える。容量は、妨害症状を有するチャネルに対して局部発振成分における基準となる周波数を可変すべく、バリキャップダイオード(VDi)42・バリキャップダイオード(VDi)用バイアス抵抗43にて構成される可変容量からなっている。

(もっと読む)

1 - 20 / 24

[ Back to top ]