Fターム[5J106RR15]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | D−A変換器 (39)

Fターム[5J106RR15]に分類される特許

1 - 20 / 39

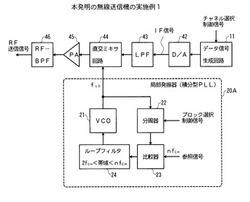

無線送信機

【課題】局部発振器の位相雑音性能の改善により、送信信号に含まれる隣接チャネル漏洩信号を大幅に低減することができる無線送信機を提供する。

【解決手段】ディジタルデータ信号を出力するデータ信号生成回路と、ディジタルデータ信号をディジタル/アナログ変換し、中間周波数のIF信号を出力するディジタル/アナログ変換回路と、IF信号と局部発振器から出力されるローカル信号とをミキシングし、無線周波数のRF送信信号を出力する直交ミキサ回路とを備えた無線送信機において、データ信号生成回路は、ディジタル/アナログ変換回路から出力されるIF信号の周波数が送信チャネルに応じて切り替わるディジタルデータ信号を出力する構成であり、局部発振器は、RF送信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成である。

(もっと読む)

周波数シンセサイザ

【課題】ディジタル処理を用いたPLLにより周波数シンセサイザを構成するにあたって、A/D変換部を不要とすること。

【解決手段】設定周波数に応じたディジタル値を積分することにより、位相信号となる鋸波を生成する。一方電圧制御発振器から出力される周波数信号を分周回路を介してエッジ検出部に入力し、前記周波数信号の立ち上がりまたは立ち下がりのエッジを検出して当該周波数信号の周波数に応じた矩形波信号を生成する。そしてラッチ回路にて、前記矩形波信号により鋸波の値をラッチし、この値をループフィルタにて積分し、電圧制御発振器の制御電圧とする。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を含むSSCG回路であって、出力クロック信号のジッタを低減する。

【解決手段】SSCG回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた第1の移相量で変化させるように、さらに、所定の範囲内で周期的に変化する第2の移相量を第1の移相量に加算するように、位相選択回路6を制御する。

(もっと読む)

信号レベル調整装置及び高周波機器

【課題】電圧制御発振器の後段に設けられた可変減衰器と、検波器と、検波電圧に応じてディジタル/アナログ変換器を介して可変減衰器の減衰量調整用の制御電圧を出力する制御部と、を備えた周波数シンセサイザにおいて、ディジタル/アナログ変換器の出力変化に基づくスプリアスを抑制できる技術を提供すること。

【解決手段】ディジタル/アナログ変換器の出力側と可変減衰器との間にローパスフィルタを設けて、ディジタル/アナログ変換器の出力の変化時に発生するオーバーシュートに対応する周波数成分をカットする。そして制御部が制御電圧を出力してから検波器で検出された信号レベルを読み込むまでの時間は、ローパスフィルタのカットオフ周波数で決まる当該ローパスフィルタの時定数よりも長い時間に設定し、信号レベルの自動制御動作に影響がないようにする。

(もっと読む)

無線通信のためのディジタル送信機

【課題】改善された性能、低電力消費、低コストのディジタル送信機を提供する。

【解決手段】デカルト座標−極座標変換器230で、受信したデカルト座標から極座標への変換を行う。FIRフィルタ234(または、デルタ−シグマ変調器)により、前記極座標の振幅情報からエンベロープ信号を生成し、位相変調PLL250、VCOにより、前記極座標の位相情報から位相変調された信号を生成する。複数状態増幅器274(または、排他的論理和ゲート)により、前記のエンベロープ信号および位相変調された信号に基づいて、ディジタル変調された信号を生成する。電力増幅器280は、前記のディジタル変調された信号を増幅して、RF出力信号を生成する。

(もっと読む)

PLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法

【課題】安価な構成とするとともに、性能を向上させることができるPLL周波数シンセサイザ、無線通信装置およびPLL周波数シンセサイザの制御方法を提供する。

【解決手段】PLL周波数シンセサイザは、基準周波数信号と分周信号との位相を比較する位相比較部101からの信号と位相誤差補償信号とに応じて、電流パルス信号を生成するCPDAC102と、電流パルス信号を電圧信号に変換するループフィルタ103と、電圧信号に応じた発振周波数の信号を出力するVCO104と、VCO104からの出力を分周して分周信号として出力する分周器105と、分数分周のための分周比のデータに基づいて、分周比制御信号を生成するデルタシグマ変調器107および加算器106と、分周比のデータから少なくとも2つの位相誤差補償用のデータを生成し、生成したデータを異なるタイミングで利用して、位相誤差補償信号を生成する制御部108とを備える。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

発振器

【課題】フロア雑音または位相雑音を抑えることができ、かつ分周器の分周比の設定に手間がかからない発振器を提供すること。

【解決手段】周波数シンセサイザの出力信号を順次分周する複数の分周器と、前記複数の分周器における最終段の分周器から目的とする周波数が得られるように、当該複数の分周器の各々について、入力周波数と分周比との組み合わせを複数設定すると共に各組み合わせ毎に、各段の分周器の出力信号のフロア雑音または位相雑音の大きさを記載した分周特性データを記憶する記憶部と、前記記憶部に記憶されている分周特性データに基づいて、各分周器の許容入力周波数の範囲内でありかつ最終段の分周器からの出力信号のフロア雑音または位相雑音が良好な入力周波数と分周比との組み合わせを判断して選択する選択部と、を備えるように発振器を構成する。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

周波数ジェネレータ

【課題】 DDSを用いて高速スイープを可能にすると共に、周波数設定を容易に行うことができる周波数ジェネレータを提供する。

【解決手段】 スイープ制御部1が、スタート周波数やスイープ周波数ステップ設定値等の周波数設定値を入力して十進数の周波数設定データを出力し、周波数設定データ変換部2が、スイープ制御部1から入力された十進数に、動作周波数、DDS3への入力設定データのビット数、スイープ周波数のステップ設定値に基づく係数をスイープ制御部から入力される十進数の周波数設定データに乗算することで二進数に変換するbitデータ変換部21と、丸め処理を行う丸め処理部22とを備え、DDS3が、入力された二進数の周波数設定データに従って周波数信号を生成して出力する周波数ジェネレータである。

(もっと読む)

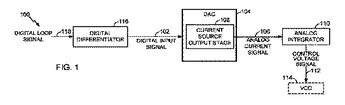

アナログ積分のためのデジタル補償を有するフェイズロックループ

フェイズロックループ(PLL)デバイスは、アナログ積分器によるアナログ電流信号の積分を少なくとも部分的に補償するために、デジタルループ信号を微分するように構成されたデジタル微分器を含む。デジタルアナログコンバータ(DAC)は、デジタル入力信号に基づいてアナログ電流信号を発生する電流源出力ステージを含む。アナログ積分器は、アナログ電流信号を積分して、電圧制御発振器(VCO)を制御するための電圧制御信号を発生する。  (もっと読む)

(もっと読む)

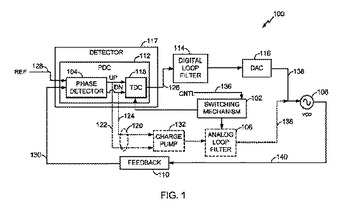

設定可能なデジタル−アナログ位相ロックループ

位相ロックループ(PLL)デバイスは、アナログ位相ロックループおよびハイブリッドアナログ−デジタル位相ロックループ内で構成可能である。アナログモードでは、少なくとも位相検出器、アナログループフィルタおよび電圧制御発振器(VCO)はアナログループを形成するために接続される。デジタルモードでは、少なくとも前記位相検出器、前記電圧制御発振器(VCO)、時間−デジタルコンバータ(TDC)、デジタルループフィルタおよびデジタル−アナログコンバータ(DAC)は前記ハイブリッドデジタル−アナログループを形成するために接続される。  (もっと読む)

(もっと読む)

周波数シンセサイザ

【課題】位相雑音を改善することのできる周波数シンセサイザを提供すること。

【解決手段】周波数設定部により設定された周波数の正弦波信号を設定信号出力部からディジタル信号として出力し、これをD/A変換する。ここから出力された正弦波信号と電圧制御発振部の出力周波数に対応する周波数の正弦波信号と、前記D/A変換部からの正弦波信号と、の差分を差動増幅器で増幅し、増幅された信号をA/D変換部を介して、既述の両正弦波信号の位相差を取り出す手段に入力する。この位相差を積分した信号に相当する電圧を電圧制御発振器に制御電圧として入力する。そして差動増幅器の利得をA/D変換部の位相雑音劣化の最大値よりも大きく設定し、これによりA/D変換部の位相雑音劣化をキャンセルする。

(もっと読む)

周波数シンセサイザ

【課題】 電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られる周波数シンセサイザを提供する。

【解決手段】 基準信号発生回路1に、OCXO20と、TCXO30と、それぞれの出力に対してウェイト調整を行うウェイト変換器21,31と、各ウェイト変換器からの出力を加算して基準信号として出力する加算器41を備え、CPU10が、電源投入時にはTCXO30のウェイトを100%、OCXO20のウェイトを0%とし、徐々にOCXO20のウェイトを上げて、予め設定された一定時間後にTCXO30のウェイトを0%、OCXO20のウェイトを100%とするようにウェイト変換器B,Cを制御する周波数シンセサイザとしており、電源投入後に急速に周波数を安定させることができるものである。

(もっと読む)

PLL回路

【課題】 全てのチャンネルについてスプリアス特性が良好なVCO出力を得ることができ、温度変化による特性変動を抑えることができるPLL回路を提供する。

【解決手段】 制御回路3が、温度センサ31と、温度に応じてチャンネル番号毎に電圧制御発振器の出力におけるスプリアス特性が良好となる分周比を記憶した分周比テーブル32とを備え、温度センサ31で検出された温度及び入力されたチャンネル番号に対応する分周比を分周比テーブル32から読み取って、PLLIC2に設定すると共に、DDS回路(基準周波数生成回路)4にチャンネル番号と分周比とを設定し、DDS回路4が、チャンネル番号と分周比に基いて基準周波数の値を算出して、当該値に対応する基準周波数を生成するPLL回路としている。

(もっと読む)

復調器および通信装置

【課題】高精度に復調処理を行う。

【解決手段】復調器30Aの局部発振器70は、変調器10から送信されて注入される変調信号SRFの局部発振周波数に局部発振信号SLOの周波数を同期させ、同期させた局部発振信号SLOをミキサ40に出力する。ミキサ40は、同期した局部発振信号SLOと変調器10から送信される変調信号SRFとを掛け算して復調信号SDMを生成する。このとき、局部発振信号SLOと周波数同期した変調信号SRFとの間の位相差に応じて復調信号SDMにDC成分が発生する。DC補正部50は、復調信号SDMのDC電圧Vdcを検出し、検出したDC電圧Vdcが予め設定されている基準電圧となるように補正する。

(もっと読む)

2点FSK変調を用いる周波数シンセサイザのための自己較正方法

【課題】2点FSK変調を用いる周波数シンセサイザの自己較正方法の提供。

【解決手段】周波数シンセサイザ1が、第1の位相ロック・ループおよび高周波アクセス部を備え、高周波アクセス部は、電圧制御発振器の第2の入力に接続されたデジタル/アナログ変換器20を備える。較正動作のために、高周波アクセス部に、第1の位相ロック・ループ内の位相比較器3に接続された第2の電荷ポンプ14および第2のループ・フィルタ15を備える。第2の電荷ポンプ14が、オンに切り替えられると、第2の位相ロック・ループを形成する。デジタル/アナログ変換器20の利得を較正するために、決められた出力周波数に予めロックされた第2の位相ロック・ループの第2の電荷ポンプ14を切り離した後に、電圧比較器21が、デジタル/アナログ変換器20の出力電圧を、第2のループ・フィルタ内に蓄えられた電圧と比較する。

(もっと読む)

搬送波生成回路

【課題】広帯域にわたって周波数成分の劣化がない搬送波を生成する搬送波生成回路を提供する。

【解決手段】指定された搬送波の周波数に応じて設定を変更する機能を設け、スプリアスが発生しない設定値に切り替える。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供する。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを利用したPLLにて、周波数引き込み手段は、PLLから電圧制御発振部への制御電圧が予め設定した設定範囲よりも大きい場合には、出力周波数を上昇させるための第1の定数を引き込み用電圧として積分し、また当該制御電圧が前記設定範囲よりも小さい場合には、出力周波数を低下させるための第2の定数を引き込み用電圧として積分する。そして加算手段は、PLLからの制御電圧と周波数引き込み手段からの引き込み用電圧とを加算し、電圧制御発振部へ出力する。

(もっと読む)

位相差補正回路及び位相差補正方法

【課題】現用系と予備系の基準クロックの位相同期の精度を向上させる。

【解決手段】基準クロック供給システムは、現用系のクロック供給回路及び予備系のクロック供給回路の冗長構成で形成され、現用系から第1の基準クロックを供給すると共に予備系から第1の基準クロックに位相同期させた第2の基準クロックを供給する。位相差補正回路は、基準クロック供給システムから第1及び第2の基準クロックを受信する側で第1及び第2の基準クロック間の位相差を測定し、その位相差情報を基準クロック供給システムにフォードバックさせる位相差測定部を有し、位相差情報に応じて、基準クロック供給システムによる第1及び第2の基準クロックの位相同期動作に補正をかける。

(もっと読む)

1 - 20 / 39

[ Back to top ]