Fターム[5J500AA51]の内容

Fターム[5J500AA51]の下位に属するFターム

入力(出力)信号切換型増幅器 (61)

ゲート増幅器、出力信号を遮断できる増幅器 (31)

双方向増幅器 (8)

Fターム[5J500AA51]に分類される特許

21 - 40 / 376

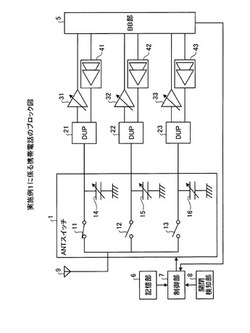

無線端末装置

【課題】電力効率を下げずに部品を削減した無線端末装置を提供する。

【解決手段】第一の筐体及び該第一の筐体と可変自在に連結される第二の筐体とを有する。そして、PA41〜43は、送信信号を増幅する。FETスイッチ14〜16は、PA41〜43とアンテナ9とを結ぶ伝送経路とグランドとの間に設けられ、中間電圧を印加した場合、印加した中間電圧に応じた静電容量を有する。開閉検知部8は、第一の筐体と第二の筐体の位置関係に対応したアンテナ9のインピーダンスを取得する。制御部7は、スイッチ11〜13のいずれか一つをONにし、開閉検知部8が取得した、アンテナ9のインピーダンスを基に、スイッチがONになっている伝送経路に配置されたPAのインピーダンスとアンテナ9のインピーダンスとが整合する静電容量を有するようにFETスイッチ14〜16に対して中間電圧を印加する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DCオフセットキャンセル動作の動作期間を短縮する。

【解決手段】フィルタ処理と増幅機能を有するアクティブローフィルタ300の差動出力端子に2個の校正抵抗R22の一方の端子が接続され、2個の校正抵抗R22の他方の端子に電圧比較器CMPの2個の入力端子と切り換えスイッチSWIOの2個の端子が接続される。DCオフセット電圧低減のデジタル制御信号DACS、DAC2…DAC0を算出する算出期間で、デジタルアナログ変換器DAC0のアナログ電流による一方の校正抵抗R22の電圧降下に依存する校正電圧を電圧比較器CMPが検出する。DCオフセット電圧を低減する校正期間では、デジタル制御信号に応答したデジタルアナログ変換器の校正アナログ電流が切り換えスイッチSWIOを介してフィルタ300の入力側に流される。

(もっと読む)

共同受信システム用増幅器

【課題】 TDA及びTBAのいずれか選択されたものとして共同受信システム用増幅器を使用可能とする。

【解決手段】 入力端子2から供給された共同受信信号を第1の増幅手段8が増幅し、1分岐器26に供給する。1分岐器26の出力信号が出力端子30に供給され、1分岐器26の分岐出力信号が分岐・分配切換手段32に供給され、その出力信号が分岐端子50、52、54、56に分配される。分岐・分配切換手段32は、1分岐器26の分岐出力信号を増幅して出力する増幅状態または前記分岐器の分岐出力信号をそのまま通過させる通過状態のいずれかとする第1の切換手段58と、第1の切換手段58の出力信号を増幅して、分岐端子50、52、54、56に供給する増幅器67とを備えている。

(もっと読む)

信号増幅回路

【課題】入力電圧に比例した電流を出力するOTAの製造ばらつきおよび周囲温度の変化による利得の変化を抑制することが可能な信号増幅回路を提供する。

【解決手段】入力電圧Vinが入力される第1のOTA1、第1のコンデンサC1を有する第1の積分器10と、第1のコンデンサC1に並列接続された第1のアナログスイッチSW1と、入力電圧Vinの積分時間を調整する積分時間調整回路3とを備える。積分時間調整回路3は、第1の参照電圧Vref1が入力される第2のOTA2、第2のコンデンサC2を有する第2の積分器20と、第2のコンデンサC2に並列接続された第2のアナログスイッチSW2と、第2の積分器20の出力電圧と第2の参照電圧Vref2とを比較するコンパレータCP2とを備え、コンパレータCP2の出力に基づいて第1のアナログスイッチSW1、第2のアナログスイッチSW2それぞれを制御する第1の制御信号、第2の制御信号を出力する。

(もっと読む)

電力増幅器

【課題】チップサイズを増加させることなく、使用する経路に応じてフィードバック経路の接続・未接続を切替えることができる電力増幅器を得る。

【解決手段】スイッチSW1は、制御信号に従って入力端子Tin1を出力端子Tout1と出力端子Tout2の何れかに接続する1入力多出力のスイッチである。スイッチSW1の入力端子Tin1は、トランジスタTr1のコレクタ(出力端子)に接続されている。フィードバック経路12は、スイッチSW1の出力端子Tour1をトランジスタTr1のベース(入力端子)に接続させる。

(もっと読む)

受信回路、電子機器、受信回路の制御方法

【課題】信号増幅について消費出力を低減することの可能な増幅回路、電子機器、増幅方法を提供する。

【解決手段】高周波信号が入力されこの高周波信号を増幅して出力するn段アンプと、前記n段アンプの消費電力の制御を行う制御回路と、前記制御に対応して前記n段アンプの内の出力の選択を行う切り替え回路とを備えた増幅回路。また、アンテナと、前記アンテナを介して入力された信号を増幅して出力する複数のアンプと、前記複数のアンプのそれぞれに供給される電流を制御する制御回路と、前記制御回路の前記電流制御に対応して、前記複数のアンプの出力を切り替える切り替え回路とを有する増幅回路と、前記増幅回路から出力された信号を復調する復調回路と、を備えた電子機器。

(もっと読む)

増幅回路

【課題】高出力時と低出力時の間で利得の変化や通過位相の変化が少ないもしくは抑制された増幅回路を提供する。

【解決手段】電力分配回路は,入力信号の電圧を複数の電圧に分配する電圧分配回路と,入力信号の電流を複数の電流に分配する電流分配回路とを縦続接続し,前段の電圧または電流分配回路に分配前入力信号を入力し,後段の電流または電圧分配回路が分配入力信号を出力する。電力合成回路は,電圧合成回路と,電流合成回路とをいずれかを前段にして縦続接続し,前段の電流または電圧合成回路に分配出力信号を入力し,後段の電圧または電流合成回路が合成後出力信号を出力する。さらに,電圧分配数Mと電流分配数Nの比M/Nと,電圧合成数Kと電流合成数Lの比K/Lとを一定に維持しながら,分配数M,Nと合成数K,Lとを変化させると共に,信号が分配される増幅器を動作状態に分配されない増幅器を非動作状態に制御する制御回路を有する増幅回路。

(もっと読む)

増幅回路

【課題】複数の増幅部の動作時の出力電圧の波形を後段回路の処理可能な電圧範囲内に収めることができる増幅回路を提供する。

【解決手段】信号入力端子66に入力されたデジタル信号のレベルが所定の値以下である場合には、増幅率変更部64は、スイッチ35をオンにして増幅部62を動作状態にするとともに、スイッチ41をオフにして増幅部63を停止状態にし、かつ、増幅部62に流し込み電流を流し込むよう流し込み電流源65を制御する。それに対し、信号入力端子66に入力されたデジタル信号のレベルが所定の値を超える場合には、増幅率変更部24は、スイッチ35をオフにして増幅部62を停止状態にするとともに、スイッチ41をオンにして増幅部63を動作状態にし、かつ、増幅部62に流し込み電流を流し込まないよう流し込み電流源65を制御する。

(もっと読む)

増幅器及びアンプ制御方法

【課題】 各アンテナへ供給可能な最大電力の配分をフレキシブルに変更可能な送信機及びアンプ制御方法を提供する。

【解決手段】 送信機は、第1乃至第3のアンプと、入力側及び出力側スイッチ部と、切替制御部とを具備する。第1のアンプは、第1のアンテナの第1の接続経路に接続される。第2のアンプは、第2のアンテナの第2の接続経路に接続される。入力側スイッチ部は、第1のアンプと第3のアンプとの間を接続する第1の入力スイッチと、第2のアンプと第3のアンプとの間を接続する第2の入力スイッチとを有する。出力側スイッチ部は、第1のアンプと第3のアンプとの間を接続する第1の出力スイッチと、第2のアンプと第3のアンプとの間を接続する第2の出力スイッチとを有する。切替制御部は、入力切替信号及び出力切替信号を同期して入力側スイッチ部及び出力側スイッチ部へ出力し、第3のアンプが第1及び第2のアンプのいずれに接続するか制御する。

(もっと読む)

チョッパスタビライズドアンプ

【課題】演算増幅回路が有限の周波数特性およびスルーレートを有することに起因して発生するグリッチングを抑制し、高調波歪のより少ない出力信号を得ることができるチョッパスタビライズドアンプを提供する。

【解決手段】変調回路MODは、所定の周波数を有する矩形波である変調信号を使って、入力信号をデジタル的に第1の被変調信号に変換する。演算増幅回路AMPは、第1の被変調信号を増幅して、第2の被変調信号に変換する。復調回路DEMODは、第1の被変調信号と第2の被変調信号の周波数成分の違いに対応する波形をもった復調信号を使って、アナログ的に第2の被変調信号を出力信号に変換する。

(もっと読む)

電流切り替え回路

【課題】定電流回路の定電流源トランジスタを破損せずに、安定的にシャットダウンを行う。

【解決手段】電流切り替え回路は、エミッタフォロア回路(EF回路)と、定電流回路と、定電流回路をオン/オフするスイッチSW1とを備える。EF回路は、ベースが信号入力端子IN1に接続され、コレクタが電源VCC1に接続され、エミッタが信号出力端子OUT1に接続されたトランジスタQ1からなる。定電流回路は、ベースがスイッチSW1の出力に接続され、コレクタがトランジスタQ1のエミッタに接続されたトランジスタQ2と、第1の端子がトランジスタQ2のエミッタに接続され、第2の端子が電源VEE1に接続された抵抗RS1と、第1の端子がトランジスタQ2のコレクタに接続され、第2の端子が電源VEE1に接続されたリーク電流源JREAK1とからなる。

(もっと読む)

バイアス回路、LNA、およびLNB

【課題】バイアスの供給のオン・オフを切り替える際の、過剰な貫通電流の発生を防止する。

【解決手段】ソース端子が接地されたHEMT1にバイアスを供給するHEMTバイアス回路10であって、オペアンプAMP1と、抵抗素子RIと、スイッチSWgと、スイッチSWdと、基準電圧源VREFと、基準電圧源VDRAINと、負電源電圧源VNEGとを備え、オペアンプAMP1は、正入力端子がHEMT1のドレイン端子に接続され、負入力端子が基準電圧源VDRAINに接続され、出力端子がHEMT1のゲート端子に接続され、負電源端子がスイッチSWgの切り替えにより負電源電圧源VNEGまたはグランドに接続可能とされ、抵抗素子RIは、第1端子および第2端子を有し、該第1端子がHEMT1のドレイン端子に接続され、該第2端子がスイッチSWdの切り替えにより基準電圧源VREFまたはグランドに接続可能とされている。

(もっと読む)

スイッチ制御回路、増幅器、および送信装置

【課題】 増幅素子のバイアス入力部の近傍に大容量のコンデンサが接続された場合であっても、バイアス電圧制御の応答遅れを抑制することが可能なスイッチ制御回路、増幅器、および送信装置を提供する。

【解決手段】 バイアスが印加されることによって増幅作用を発生する増幅素子の前記バイアスのオン/オフを制御するスイッチ制御回路であって、二つのスイッチ素子が相補的に動作するコンプリメンタリ回路を複数並列に接続した回路を含む。

(もっと読む)

増幅回路とそれを有する無線受信装置

【課題】ゲインと最大入力振幅とを独立して制御可能な増幅回路及びそれを有する受信装置を提供する。

【解決手段】増幅回路は,入力信号がゲートに入力され可変ゲート幅を有するソース接地トランジスタと,ソース接地トランジスタのドレインと電源との間に設けられた可変電流源と,ドレインと可変電流源との接続ノードに接続された出力端子と,出力端子と基準直流電源との間に設けられた可変抵抗負荷とを有する増幅器と,ゲイン制御信号と最大入力振幅制御信号に基づいて,ソース接地トランジスタのゲート幅と,可変電流源の電流値と,可変抵抗負荷の抵抗値とを制御する増幅器制御回路とを有する。

(もっと読む)

音声切換出力装置

【課題】 BTL方式を使用して音声信号を出力するか否かを切換可能であり、かつ、コモンモードチョークコイルを備える場合に、信号経路ではないコモンモードチョークコイルが音声信号に悪影響を与えることを防止すること。

【解決手段】 BTL方式を使用しない場合、スイッチSW1、スイッチSW2をオン状態に制御し、スイッチSW3、スイッチSW4をオフ状態に制御する。従って、音声信号の電流がコモンモードチョークコイルL3に流れることがなく、音声信号に歪みが生じることが防止される。BTL方式を使用する場合、スイッチSW1、スイッチSW2をオフ状態に制御し、スイッチSW3、スイッチSW4をオン状態に制御する。従って、音声信号の電流がコモンモードチョークコイルL4、L5に流れることがなく、音声信号に歪みが生じることが防止される。

(もっと読む)

電子回路

【課題】適切な利得制御を行うことが可能な電子回路を提供すること。

【解決手段】入力信号Iinを増幅する増幅器10と、増幅器10から出力された出力信号Vtiaを、時定数に基づいて平均化して制御信号Vagcを生成するとともに、時定数τs1と、時定数τs1より大きい時定数τl1との間で時定数を切り替え可能な制御回路20と、制御信号Vagcに基づいて第1時定数制御信号を生成し、制御回路20の時定数を時定数τs1から時定数τl1に切り替える第1時定数制御回路30と、増幅器10から出力された出力信号Vtiaを、時定数τs1より大きく、かつ時定数τl1より小さい時定数τl2に基づいて平均化して第2時定数制御信号を生成し、制御回路20の時定数を時定数τl1から時定数τs1へと切り替える第2時定数制御回路60と、制御信号Vagcに基づいて、入力信号Iinをバイパスするバイパス回路40と、を具備する電子回路。

(もっと読む)

変調電源回路

【課題】オーバーシュート/アンダーシュートを低減することで、デバイスサイズの拡大を抑えるとともに、エラーアンプの効率を改善し高効率な変調電源回路を提供すること。

【解決手段】変調電源回路100は、入力されるエンベロープ信号と閾値テーブル160の閾値とを比較器150で比較して、スイッチ部120の各スイッチ121〜123を切替える切替信号を生成する制御部140と、スイッチ部120に入力される切替信号を監視し、スイッチ部120の各スイッチ121〜123が同時にオン/オフしないようにタイミングをずらす遅延を切替信号に挿入する遅延挿入部200とを備える。

(もっと読む)

増幅回路及びその増幅回路を含むアナログデジタル変換回路

【課題】オフセットキャンセル動作において発生する消費電力を低減可能なコンパレータを提供する。

【解決手段】差動入力信号を受ける一対のMOSトランジスタのドレインと高電位電源線に接続し、一対のMOSトランジスタのドレインに接続する差動出力ノード間の電位差を増幅し、増幅後の電位を差動出力ノードに保持する増幅部と、差動出力ノード間の電圧増幅時に、差動出力ノードにキャンセル電流を流し、増幅部による増幅動作後に、一対のMOSトランジスタのドレイン電圧に応じて差動出力ノードへのキャンセル電流の流入を遮断するキャンセル回路と、差動入力信号の一方の信号の電位を他方の信号の電位と等しく設定し、差動出力ノード間の電位差を増幅したときに、差動出力ノード間の電位が、キャンセル電流を注入する前に比較し、キャンセル電流の注入後に逆転するように、キャンセル電流を設定するコントローラと、を備える増幅回路。

(もっと読む)

電流制御回路

【課題】小規模、低消費電力にて信号電流を抽出する電流制御回路を実現する。

【解決手段】電流制御回路100は、電流源としてのフォトダイオードPD、準備回路102、制御回路104および除去回路106を含む。制御回路104は、準備期間において準備回路102に第1の電流を供給し、受信期間において除去回路106とフォトダイオードPDとを接続する経路に第2の電流を供給する。準備回路102は、準備期間において、電流源から供給される第1の電流に含まれる直流成分により充電される。除去回路106は、受信期間において、電流源から供給される第2の電流から直流成分を差し引くことにより、電流から交流成分(信号電流)を分離する。

(もっと読む)

半導体装置及び電子機器

【課題】負荷(EL画素や信号線)に電流を供給するトランジスタにおいて、バラツキの影響を受けずに正確な電流を供給できる半導体装置を提供する。

【解決手段】増幅回路を使ったフィードバック回路を用いて、トランジスタの各端子の電圧を調節する。電流源回路から電流Idataをトランジスタに入力して、トランジスタが電流Idataを流すのに必要なゲート・ソース間電圧を、フィードバック回路を用いて設定する。フィードバック回路は、トランジスタが飽和領域で動作するように制御する。すると、電流Idataを流すのに必要なゲート電圧が設定される。そして、設定されたトランジスタを用いれば、正確な電流を負荷(EL画素や信号線)に供給できる。なお、必要なゲート電圧を設定するとき、増幅回路を用いるので、すばやく設定できる。

(もっと読む)

21 - 40 / 376

[ Back to top ]