Fターム[5J500AA51]の内容

Fターム[5J500AA51]の下位に属するFターム

入力(出力)信号切換型増幅器 (61)

ゲート増幅器、出力信号を遮断できる増幅器 (31)

双方向増幅器 (8)

Fターム[5J500AA51]に分類される特許

61 - 80 / 376

増幅回路及び受信装置

【課題】受信電波環境の変化に対して良好な受信感度を得ることのできる増幅回路及び受信装置を提供する。

【解決手段】入力信号の強度が第1の状態のときは第1の出力端に出力し、前記入力信号の強度が前記第1の状態よりも大きい第2の状態のときは第2の出力端に出力する入力回路と、前記第1の出力端から出力された信号を増幅し位相を反転して出力する反転増幅回路と、前記第2の出力端から出力された信号をそのまま、または減衰して出力するバイパス回路と、前記第1の状態のときは前記反転増幅回路の出力の位相を反転してまたは同相で出力し、前記第2の状態のときは前記バイパス回路の出力を同相または位相を反転して出力する出力回路と、を備えたことを特徴とする増幅回路が提供される。

(もっと読む)

ドライブ回路

【課題】低電圧の制御信号を高電圧の制御信号に変換して出力する高圧用のドライブ回路において、待機時の消費電力を削減することができるようにする。

【解決手段】低圧部1からの制御信号a1〜d1及びa2〜d2により高圧部2のトランジスタMN1〜MN8を駆動し、操作対象3に駆動信号を出力する。その際、低圧部1からの制御信号a1〜d1をそれぞれ論理積ゲートQ1〜Q4の一方の入力端子を介して高圧部2のトランジスタMN1,MN3,MN5,MN7のゲートに入力し、論理積ゲートQ1〜Q4の他方の入力端子には高圧部2のオン/オフ信号を入力する。

(もっと読む)

マルチステージのインピーダンス整合

インピーダンス整合を実行する例示的な技術を記述する。装置は、第1および第2の整合回路とに結合されている増幅器を備える。第1の整合回路は、第1のノードに結合されている複数のステージを備え、増幅器に対する入力インピーダンス整合を提供する。第2の整合回路は、第2のノードに結合されている複数のステージを備え、増幅器に対する出力インピーダンス整合を提供する。少なくとも1つのスイッチは、第1のノードと第2のノードとの間に結合され、増幅器をバイパスまたは選択する。第1および第2のノードは、共通のインピーダンスを持つ。装置は、増幅器と並列に、整合回路にさらに結合されている第2の増幅器をさらに備える。第2の整合回路は、増幅器に結合されている第1の入力ステージと、第2の増幅器に結合されている第2の入力ステージと、スイッチを通して2つの入力ステージに結合されている第2のステージとを備える。 (もっと読む)

車載用アンプの低バッテリ電圧時制御方法及び装置

【課題】バッテリ電圧が低下してアンプの電流が増大し、ヒューズ切れ等を生じることがなく、且つアンプ全体の出力の大きな低下を生じない「車載用アンプの低バッテリ電圧時制御方法及び装置」とする。

【解決手段】複数チャンネルのオーディオ信号を入力して各チャンネルの出力レベルを算出し、その出力レベルにより、最も出力レベルの高いチャンネルを選択し、アンプの昇圧用出力電圧を、最も出力レベルの高いチャンネルの出力が得られるように設定する。この出力電圧で作動するバッテリ電流を算出し、その電流がヒューズの容量を超えるかを判別する。超えないときはアンプからスピーカへの出力を行い、超えるときは前記選択した最も出力レベルの高いチャンネルの出力レベルを所定量低下させ、低下させた出力レベルでのバッテリ電流がヒューズの容量を超えないとき、アンプからスピーカへの出力を行う。

(もっと読む)

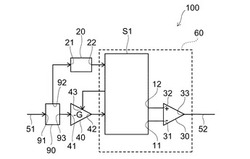

携帯電話端末、高周波複合装置、および高周波切替装置

【課題】複数の通信方式に対応した携帯電話端末における高周波送受信信号経路と制御信号経路のレイアウトを簡略化する。

【解決手段】複数の通信方式の高周波送受信信号経路の切替を行う切替装置100aは、複数のスイッチSW1〜SW6と論理回路110aを有する。論理回路110aは、高周波制御装置140aからの制御信号a〜cに応じて制御信号d1〜d8を生成する。そのうち制御信号d1〜d6は、それぞれ、信号経路をON/OFFする複数のスイッチSW1〜SW6の切替制御信号となる。制御信号d7,d8は電力増幅器PA1,PA2のON/OFF制御信号として出力される。SW3,SW4の切替制御信号d3,d4は、PA3,PA4のON/OFF制御信号を兼ねる。

(もっと読む)

複数の動作モードを備えた増幅器モジュール

複数の動作モードを備えた増幅器モジュールが記述される。例示的な設計において、増幅器モジュールは、増幅器(例えば、電力増幅器)、スイッチ、および、出力回路を含む。増幅器は、第1のモードで入力信号を受取って増幅し増幅信号を提供する。スイッチは増幅器の出力に結合され、第2のモードで増幅器をバイパスしてバイパス信号を提供する。出力回路は増幅器およびスイッチに結合される。出力回路は第1のモードで増幅器のための出力インピーダンス整合を行う。出力回路は、さらに、(i)第1のモードで増幅信号を受取って出力信号を提供し、(ii)第2のモードでバイパス信号を受取ってて出力信号を提供する。増幅器は第1のモードでイネーブルされ、第2のモードでディセーブルされうる。  (もっと読む)

(もっと読む)

比較回路

【課題】比較回路の自己発熱を抑制して、自己発熱対策に起因する当該比較回路の動作速

度の低下を防止できるようにする。

【解決手段】差動増幅部11,12にスイッチS1,S2をそれぞれ接続させる。スイッ

チS1をONにして差動増幅部11を動作させるときには、スイッチS2をOFFにして

差動増幅部12を停止させ、スイッチS2をONにして差動増幅部12を動作させるとき

には、スイッチS1をOFFにして差動増幅部11を停止させる。この結果、スイッチS

1,S2によって差動増幅部11,12が交互に動作するので、差動増幅部11,12の

動作による自己発熱を抑制することができ、自己発熱対策に起因する比較回路1の動作速

度の低下を防止できる。

(もっと読む)

スプリット−バイアス電流のスケーラブル・バッファ

集積回路を渡る伝達のために、高周波数信号(IN)をバッファリングするための回路、技術、方法が開示される。ある特別の実装において、複数の増幅回路(M1,M2)は、電圧制御発振器および/またはデジタル制御発振器からの信号を増幅するために個別にバイアスされ、デバイス上の局所発振器の信号を提供する。 (もっと読む)

アレーアンテナ用送信機

【課題】装置の小型化を実現しながら、複数のアンテナブランチ全ての各送信部の増幅器の歪み補償を可能にしたアレーアンテナ用送信機を提供する。

【解決手段】アンテナブランチ数に対応したN系統毎の送信データのプレディストーション信号を増幅し送信信号を発生する送信部及び送信データの計算した瞬時振幅に応じた歪み補償係数を記憶部から読出し送信データに乗算してプレディストーション信号を生成し送信部に入力するプレディストーション部と、N系統中の割当られた複数の系統に対し送信部からの送信信号の一部のフィードバック信号と該系統の送信データを比較し歪み補償係数を演算しプレディストーション部へ記憶部を更新するために出力する重複なしにN系統が割当られた系統数N未満のM個のフィードバック推定演算部、フィードバック推定演算部を割当られた系統に時分割で接続する推定演算部毎の切替手段を含む。

(もっと読む)

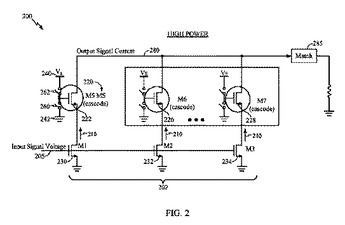

RF駆動増幅器送信機における利得制御の直線性

入力信号電圧を複数の入力信号電流に変換するための複数の電圧−電流トランスデューサとカスコード段とを備える例示的装置が開示される。カスコード段は、増幅器利得制御を実現するように電圧−電流トランスデューサに結合される。カスコード段は、薄ゲート酸化膜トランジスタと厚ゲート酸化膜トランジスタとを備える。  (もっと読む)

(もっと読む)

増幅部制御装置、及び、増幅部制御プログラム

【課題】増幅部の消費電力を継続的に低減するように、増幅部を制御することができる増幅部制御装置及び増幅部制御プログラムを提供する。

【解決手段】本発明にかかる増幅部制御装置は、撮像素子から供給された第1の信号を増幅し、増幅した後の信号である第2の信号を後段の信号処理回路に供給する増幅部を制御する増幅部制御装置であって、前記増幅部に供給される前記第1の信号が画像データに使用されるか否かに応じて前記増幅部に供給される電流を変化させる制御手段を備える、ことを特徴とする。

(もっと読む)

オフセットキャンセル回路

【課題】ホール素子のオフセットキャンセル回路における基準電圧差とオフセットキャンセル回路の容量素子につく寄生容量によって生ずる出力オフセットを低減する。

【解決手段】ホール素子10に流れる電流が切り替わるように外部から電圧を印加したときに、その各状態でのホール素子10の出力電圧で複数のコンデンサC1,C2をそれぞれ充電する。複数のコンデンサC1,C2を並列に接続するスイッチング素子S11,S12に、スイッチング素子S11,S12と互いに排他的にオン/オフ制御されるダミースイッチング素子D1,D2を接続する。

(もっと読む)

低雑音増幅器およびミキサ

パワー消費に対して制御可能な線形性および雑音指数を有する低雑音増幅器(LNA)システムが提供される。システムは、調節のために2つの制御入力を備える。一方の入力は、実効トランジスタ幅を制御し、他方の入力は、バイアス電流を制御する。実効トランジスタ幅に対する変化が、信号に与えられる利得を変更し、バイアス電流に対する変化が、システムのパワー消費を変更する。より厳密な信号仕様に関して、LNAのインピーダンス整合した誘導縮退変化が提供される。  (もっと読む)

(もっと読む)

RF増幅装置

【課題】RF変調信号の広帯域化を図り、出力電圧をより高速に変化させる場合でも、電力効率の低下を抑え、かつ、RF増幅器の飽和を回避するRF増幅装置を提供する。

【解決手段】第1RF増幅部103及び第2RF増幅部104は、RF変調信号を所望の電力まで増幅する。ET動作電圧信号生成部108は、RF変調信号の包絡線振幅情報と、第2RF増幅部104の電源電圧−出力特性とに基づいて、ET動作電圧信号を生成する。DC電源部110は、複数の異なるDC電圧を出力し、DC電圧選択切替部111は、ET動作電圧信号に基づいて、DC電源部110から出力された複数のDC電圧のうち一つを第2RF増幅部104に選択出力する。補助電源部114は、DC電圧選択切替部111の出力電圧がET動作電圧信号生成部108から出力されたET動作電圧以下となる瞬間にET動作電圧を第2RF増幅部104に出力する。

(もっと読む)

波形直線性に基づくPA利得ステート切換え

無線通信デバイスの通話時間を増加させるために、既存の低コスト複数利得ステート電力増幅器(PA)の電力消費を最適化するための技術が説明される。典型的な実施形態において、例えばベースバンド・プロセッサのようなデバイスは、送信信号を増幅するための少なくとも2つの利得ステートを有するマルチステージPAを最も低い電力消費利得ステートに設定するように動作する。デバイスは、識別された最大電力低減(MPR)値の関数として遷移電力レベルを計算し、送信電力レベルが計算された遷移電力レベルよりも高い場合、PAを低利得ステートから高利得ステートへ切り換える。  (もっと読む)

(もっと読む)

携帯電話機、電圧切替制御方法、プログラム

【課題】PAに供給する電圧の供給切り替え制御においてばたつきが生じることなく、従

来よりPAに供給するローモード時の電圧を下げることを実現した携帯電話機を提供する

。

【解決手段】DC/DCコンバータ12が、PA16に電圧Cを供給している間に、制御

部5が、所望の送信電力レベルが一定期間、閾値E以下となるように、VGA15の利得

を制御した時(指示線41が示す時点)、PA16への供給電圧をCからFに切り替え、

DC/DCコンバータ12が、PA16に電圧Dを供給している間に、制御部5が、所望

の送信電力レベルが閾値Eを超えるように、VGA15の利得を制御した時(指示線42

が示す時点)、PA16への供給電圧をFからCに切り替える制御を行う。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】増幅回路の応答速度等を改善する。

【解決手段】増幅回路1bは、入力信号が供給される差動増幅回路20と、差動増幅回路20の出力を受けるソースフォロア回路30と、ソースフォロア回路30の出力端E、差動増幅回路20の入力端S、差動増幅回路20の出力端とソースフォロア回路30の入力端Sの間の中間端点Mのそれぞれと接続される複数の帰還経路ブロック40を備える。各帰還経路ブロック40において、抵抗16およびキャパシタ17の一端は、選択スイッチ18を介して入力端Sと接続され、抵抗16の他端は出力端Eに接続され、キャパシタ17の他端は中間端点Mに接続されている。そして、中間端点Mから帰還経路ブロック40−2、40−3のキャパシタ17−2、17−3に至る経路に解放スイッチ70が間挿される。

(もっと読む)

増幅回路及び送受信機

【課題】不要な電力損失の防止及び/又は高周波数特性の低下防止を実現することができる増幅回路を提供することを課題とする。

【解決手段】第1のゲートには差動信号の一方の信号が入力され、第1のソースが基準電位ノードに接続された第1の電界効果トランジスタ(101)と、第2のゲートには差動信号の他方の信号が入力され、第2のソースが基準電位ノードに接続された第2の電界効果トランジスタ(102)と、第1の1次側インダクタ(103)が第1の電界効果トランジスタの第1のドレイン及び第2の電界効果トランジスタの第2のドレイン間に接続され、第1の2次側インダクタ(104)が出力端子及び基準電位ノード間に接続された第1のトランスフォーマと、第1の1次側インダクタの中点に電源電位ノード又は基準電位ノードを接続する第1のスイッチ回路(301,302)とを有する増幅回路が提供される。

(もっと読む)

半導体集積回路

【課題】電源電圧が低い場合においても確実に動作させることができる半導体集積回路を提供する。

【解決手段】入力端子1、2に入力される信号を、制御信号SEL1、SEL2に従ってオン/オフ制御するNMOSスイッチ5、6と、NMOSスイッチ5、6によってオン/オフ制御された信号を増幅する演算増幅器8とを具備する半導体集積回路である。この集積回路は、制御信号SEL1、SEL2を演算増幅器8の電源電圧より高い電圧に昇圧するレベルシフタ31を有している。

(もっと読む)

バイアス生成回路及び電圧制御発振器

【課題】小さい面積で低ノイズのバイアスを生成する。

【解決手段】 元バイアス電圧を発生するバイアス発生部と、前記元バイアス電圧と比較電圧とを比較し、比較結果を出力する比較部と、可変抵抗部を含む抵抗回路によって構成されて前記比較電圧を発生する抵抗分割部と、前記比較部の比較結果に基づいて、前記比較電圧を前記元バイアス電圧に近づけるように前記可変抵抗部の抵抗値を制御するためのバイアス決定データを求めるバイアス決定制御部と、前記バイアス決定データを保持して前記可変抵抗部の抵抗値を制御することにより前記比較電圧をバイアス電圧として出力させる記憶部とを具備したことを特徴とする。

(もっと読む)

61 - 80 / 376

[ Back to top ]