Fターム[5J500AK06]の内容

Fターム[5J500AK06]に分類される特許

1 - 20 / 132

コンデンサマイクロホン用インピーダンス変換器およびコンデンサマイクロホン

同相電圧帰還回路及び全差動演算増幅器

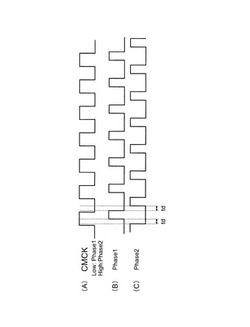

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の利得の温度依存性を抑制し、温度補償回路を有するバイアス回路を備えた電力増幅回路を提供する。

【解決手段】ドレインが高電位に接続され、ソースが接地された増幅用トランジスタを備え、ソースが接地され増幅用トランジスタGTrのゲートにゲートが接続されたカレントミラートランジスタCMTrによって増幅用トランジスタのバイアス電流を制御する電力増幅回路であって、アノードが制御電源端子に接続された第1のダイオードD1と、アノードが第1のダイオードD1のカソードに結合され、カソードがカレントミラートランジスタCMTrのドレインに接続された第2のダイオードD2と、一方の端子が第2のダイオードD2のカソードに接続され他方の端子が接地された第1の抵抗素子R1と、第2のダイオードD2と並列接続された第2の抵抗素子R2とを備える。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

ソースフォロア回路

【課題】電流源側の駆動能力の大幅な改善を図り、回路の消費電力やエリアの大幅な削減を図るようにしたソースフォロア回路の提供。

【解決手段】この発明は、入力電圧を受けるMOSトランジスタM1と、MOSトランジスタM1とカスコード接続される電流源10とを備えている。電流源10は、MOSトランジスタM1とカスコード接続されるMOSトランジスタM2と、MOSトランジスタM1とMOSトランジスタM2との共通接続部と、MOSトランジスタM2のゲートとの間に接続されるコンデンサC1と、MOSトランジスタM2のバイアスを印加する経路上に配置される抵抗R1とを備えている。

(もっと読む)

全差動増幅器

【課題】初期動作を安定させるスタートアップ回路を備え、消費電力を低減すると共に、回路規模の増加を抑制した全差動増幅器を提供する。

【解決手段】図1に示す全差動増幅器は、入力信号を受け付ける差動対を含み、差動信号を出力する差動増幅器と、差動信号を増幅し、差動出力信号から出力コモンモード電圧を生成する出力コモンモード電圧生成回路と、出力コモンモード電圧と所定の基準電圧を比較することでコモンモードフィードバック信号を生成し、コモンモードフィードバック信号を差動増幅器にフィードバックすることで、出力コモンモード電圧と基準電圧を実質的に一致させるコモンモードフィードバック回路と、入力信号に基づいて、差動信号を略電源電圧にプルアップ又は略接地電圧にプルダウンするスタートアップ回路と、を備える。

(もっと読む)

演算増幅器

【課題】チップ面積の極端な増大を招くことなく、電源投入時の過渡期に出力端子を接地側に落とことを可能にすること。

【解決手段】正転入力電圧VIN_Pと反転入力電圧VIN_Nの差分を増幅する差動増幅回路10と、該差動増幅回路10の出力信号を入力し増幅してPMOSトランジスタM12とNMOSトランジスタM13の共通接続点から出力電圧VOUTを出力する出力回路20とを有する演算増幅器100である。トランジスタM13のゲートに一端が接続されたコンデンサCx1とトランジスタM12のゲートに一端が接続されたコンデンサCx2を備え、コンデンサCx1,Cx2の他端は抵抗Rx1を介して高電源端子1に接続されている。

(もっと読む)

定電流回路およびフィールド機器

【課題】電流信号の伝送線上の負荷に流れる電流の値の変化を低減させることのできる定電流回路およびフィールド機器を提供する。

【解決手段】電流(電流信号)ISが流れる伝送線L1上の負荷Fに対して直列に接続され、該負荷Fに流れる負荷電流I1の値を検出する電流検出部21と、負荷Fおよび電流検出部21の上流で伝送線L1から分流して負荷Fおよび電流検出部21の下流で伝送線L1に合流するバイパス電流I2の値を、負荷電流I1の値に基づいて制御する電流制御部25と、を備える。

(もっと読む)

オペアンプ

【課題】位相余裕を減らすことなく電源立ち上げ時における出力電圧の立ち上がりを速くする。

【解決手段】電源電圧が立ち上がると、入力電圧VinpがVinmよりも高くなるので、トランジスタ9がオン、トランジスタ10がオフとなり、差動対11に供給される動作電流は全てトランジスタ9に流れる。電流検出回路62に電流が流れないので、トランジスタ73がオフし、第2の定電流回路69が出力する増分動作電流I2は、ダイオード72を通して差動対11に流れ込む。トランジスタ9に流れる電流は定常動作電流I1+増分動作電流I2となり、位相補償コンデンサ8の充電電流が増えて出力電圧Voの立ち上がりが速くなる。

(もっと読む)

バイアス回路を一体化した金属酸化膜半導体デバイス

【課題】デバイスの温度変動および/またはプロセス変動に起因するMOSデバイスのバイアス条件の変動を正確に補償できる技術を提供する。

【解決手段】ICデバイスがゲート端子、ソース端子およびドレイン端子を有するMOSデバイスを備え、ゲート端子はICデバイスの入力部に動作可能に結合され、ドレイン端子はICデバイスの出力部に動作可能に結合され、ソース端子は負電圧供給源に結合している。ICデバイスは、さらに、MOSデバイスのゲート端子に動作可能に結合されているバイアス発生器を備え、このバイアス発生器は、MOSデバイスにほぼ一定の静止動作点でバイアスをかけるバイアス電圧および/またはバイアス電流を発生する。バイアス発生器は、バイアス電圧および/またはバイアス電流がMOSデバイスの接合温度の関数として変化するように構成されている。このようにして、バイアス発生器が、MOSデバイスの1つまたは複数の動作条件を正確にたどり、それによってデバイスの性能を向上させる。

(もっと読む)

完全差動型オペアンプ

【課題】完全差動型オペアンプの動作の安定度を向上し、高速動作を可能にする。

【解決手段】差動増幅部は、第1ステージの第1の差動増幅回路と、第2ステージの第2の差動増幅回路2から構成される。位相補償回路5は、第2の差動増幅回路2の差動入力端子と差動出力端子との間に接続されている。第1のCMFB回路3は、第1ステージの差動増幅回路1の差動出力電圧VP,VNの第1の同相電圧VC1が第1の基準電圧になるように、第1の差動増幅回路1をフィードバック制御する。第2のCMFB回路4は、第2の差動増幅回路2の差動出力電圧VOUTP,VOUTNの第2の同相電圧VC2が第2の基準電圧になるように、第2の差動増幅回路2をフィードバック制御する。

(もっと読む)

差動トランスインピーダンス増幅器

【課題】同相入力電流成分に対する耐性を大きくする。

【解決手段】差動トランスインピーダンス増幅器は、入力信号合成回路12で得られた、入力端子IT,ICのそれぞれの信号を合成した同相入力電圧と、出力信号合成回路15で得られた、出力端子OT,OCのそれぞれの信号を合成した参照電圧との差電圧に応じた制御信号を制御用増幅器13で生成し、可変電流源IS1,IS2で、この制御信号に応じた量の電流を入力電流信号から引き抜く。入力信号合成回路12は、抵抗R31〜R33と、容量C31とから構成される。出力信号合成回路15は、抵抗R41〜R43と、容量C41とから構成される。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

適応型バイアシングを用いた高スイング演算増幅器出力段

【課題】加工コストを増大させず、適応型バイアシング出力段を用いた高スイング演算増幅器を提供する。

【解決手段】出力段123は、VDDAノードと出力ノードとの間のプルアップ電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT3及びバイアシングトランジスタT4)を含み、前記出力ノードと接地ノードとの間のプルダウン電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT1及びバイアシングトランジスタT2)も含む。前記バイアシングトランジスタT4,T2を提供することは、前記トランジスタT3,T4において低下される最大電圧を低減させ、それによって前記トランジスタT1〜T4がVDDAよりも低い破壊電圧を有するのを可能にする。

(もっと読む)

電圧電流変換回路

【課題】差動入力部を有するとともに、出力部を構成するカレントミラー回路のミラー比を調整して入力オフセット電圧をもたせた電圧電流変換回路において、差動入力部および入力オフセット電圧の温度特性を平坦なものにする。

【解決手段】平坦な温度特性を有する第1の定電流Ib1に正の温度特性を有する第2の定電流Ib2を加えた電流をバイアス電流として、MP10及びMP11からなる差動入力部に供給することにより、差動入力部の温度特性とバイアス電流の温度特性とを相殺させて差動入力部の温度特性をゼロ(平坦なもの)にすることができる。また、電流吐き出し型の第1のカレントミラー回路の出力と、電流吸い込み型の第2のカレントミラー回路の出力との接続点を電圧電流変換回路の出力端子Out2とし、この接続点に第1の定電流Ib1に比例した電流を加える構成により、温度特性のない入力オフセット電圧も実現することができる。

(もっと読む)

オペアンプ

【課題】低い電源電圧に対応する生産プロセスで生産された製品に対して高い電源電圧を供給した場合にも、ホットキャリアに起因するオペアンプ特性の劣化を回避することができるオペアンプを提供する。

【解決手段】バイアス電源回路が、2つのカレントミラー回路の間に挿入された一対の抵抗部を有して定電流バイアス電位の他に付加バイアス電位を生成し、差動増幅器が、差動入力トランジスタ対と能動負荷トランジスタ対との間に挿入され且つ当該付加バイアス電位によってバイアスされる電圧降下用トランジスタ対を含むオペアンプ。

(もっと読む)

パルス幅変調回路およびスイッチングアンプ

【課題】 オーディオ信号の振幅が負側に過大になったときのパルス幅変調信号の応答性を安定させる。

【解決手段】 パルス幅変調回路10は、クロック生成回路11と、差動増幅回路12と、第1充電電流生成回路13と、第2充電電流生成回路14と、スイッチSW1〜SW4と、コンデンサC1,C2と、第1放電用定電流回路15と、第2放電用定電流回路16と、第1パルス生成回路17と、第2パルス生成回路18と、パルス合成回路19と、充電開始電圧維持回路20とを備える。充電開始電圧維持回路20は、コンデンサC1、C2の電圧が定電流Idによる放電動作によって電圧Vaよりも低下しようとするときに、電源電圧をコンデンサC1、C2に供給することによって、コンデンサC1、C2の充電開始電圧がVaよりも低下することを防止する。

(もっと読む)

差動増幅器及びアナログ/デジタル変換器

【課題】スイッチに流れるオフリーク電流の影響を抑制し、利得の発振を抑える。

【解決手段】差動増幅器16は、入力信号が入力される入力端子27,28と、前記入力信号が増幅された出力信号を出力する出力端子25,26と、を備える差動増幅器16であって、前記入力信号を増幅し前記出力信号を生成する増幅部21と、前記増幅部21と電源端子との間に接続され、第1導電型トランジスタT34,T35と、前記第1導電型トランジスタT34,T35のゲート端子をドレイン端子に接続するかまたは前記出力端子25,26に接続するかを切り替える切り替えスイッチ22と、を有する負荷回路23と、前記切り替えスイッチ22のオフリーク電流を低減するキャンセル電流を生成するリークキャンセルスイッチ30と、を備える。

(もっと読む)

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

1 - 20 / 132

[ Back to top ]