Fターム[5J500AM05]の内容

Fターム[5J500AM05]に分類される特許

1 - 20 / 85

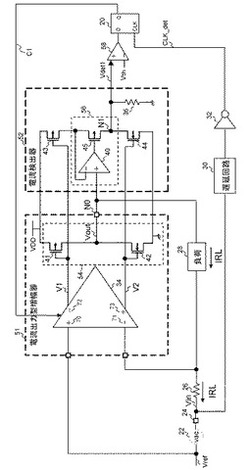

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】第1バッファ10の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第2バッファ12の電源端子には、第1電源からの第1電源電圧VCC1が供給される。非反転アンプ14の電源端子には、第2電源電圧VCC2が供給される。起動電圧源16は、その電源端子に第2電源電圧VCC2を受け、起動電圧VSTARTを生成する。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW1をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW1をオフする。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

増幅回路および帰還回路

【課題】反転入力容量Csinが異なる場合、帰還容量Cfが小容量の固定値であっても、周波数特性の肩特性の劣化やピークがほとんど生じない増幅回路および帰還回路を提供する。

【解決手段】個別に負帰還をかけるとともに直列に接続された複数の増幅器と、前記複数の増幅器に含まれる出力側の増幅器の出力側と入力側の増幅器の入力側に接続された帰還手段(帰還回路)とを備え、前記複数の増幅器は奇数個の反転増幅器を含む構成である。

(もっと読む)

定電圧バッファ回路

【課題】スタートアップ時などに、演算増幅回路の出力電圧が、駆動能力の高い側とは反対方向に大きくずれた場合においても、出力段の定電流源に制限されることなく、所定電圧へのセットリングを加速することが可能な定電圧バッファ回路を提供すること。

【解決手段】基準電圧(Vref)をバッファし、一定電圧の出力電圧(Vout)を供給する定電圧バッファ回路であって、出力電圧と基準電圧とを取得する差動増幅器(1)と、差動増幅器(1)の出力信号に応じて制御されるP型駆動の出力手段(2)と、出力電圧が基準電圧よりも大きいことを検出する検出手段(M11)と、検出手段(M11)において、出力電圧が基準電圧に対して大きいことが検出された場合には、出力ノードから電流を引き出すように電流を制御する電流制御手段(3)とを有する定電圧バッファ回路。

(もっと読む)

ボルテージフォロワ回路

【課題】動作電流を大きく増大させることなく、入力信号変化に対する出力追従性を向上させることのできるボルテージフォロワ回路を提供する。

【解決手段】実施形態のボルテージフォロワ回路は、P型差動対101と、N型差動対102と、折り返しカスコード型中間増幅段103と、出力段104とを備える演算増幅回路100を使用するボルテージフォロワ回路であって、出力変化加速部1が、P型差動対101に接続された定電流源I101からP型差動対101へ電流が流れないときに、出力段104へ加速電流I1を印加して出力段104の出力変化を加速し、出力変化加速部2が、N型差動対102に接続された定電流源I102からN型差動対102へ電流が流れないときに、出力段104へ加速電流I2を印加して出力段104の出力変化を加速する。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

トランスインピーダンスアンプ、半導体デバイス、および光通信モジュール

【課題】高速、かつ高品質な受信動作が実現可能な、トランスインピーダンスアンプを含んだ光通信モジュールを提供する。

【解決手段】トランスインピーダンスアンプTIAにおいて、単相電流信号を入力として単相電圧信号に変換するプリアンプPRAMPと、プリアンプPRAMPの出力の単相電圧信号の中心電位を検出する閾値検出回路ATCと、プリアンプPRAMPの出力の単相電圧信号を差動化するとともに増幅するポストアンプPSAMPと、プリアンプPRAMPに電源を供給する電源回路PSPYとを有する。特に、電源回路PSPYは、プリアンプPRAMPの入力電圧信号または出力電圧信号でプリアンプPRAMPの電源端子に流れる変化電流とその変化電流と逆相の変化電流とを出力する。これにより、電源電流変化量を相殺する。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

電子装置

【課題】電力損失を最小限にすることが可能な複数の電源を含む電子装置を提供する。

【解決手段】パワーアンプ40は、入力電圧Viに基づいた出力電圧の電力を被試験体DUTに供給する。検出回路43は、パワーアンプ40の動作電源であるスイッチング電源22から、パワーアンプ40に電流が流れたことを検出する。選択回路51は、電流が流れない場合には、スイッチング電源22の電圧値を所定値に設定し、電流が流れた場合には、スイッチング電源22の電圧値を入力電圧Viより予め定められた値αだけ大きい値に設定する。

(もっと読む)

スルーレート制御回路、制御方法及び半導体集積回路

【課題】出力アンプのスルーレートを、出力負荷変動があっても高精度に調整可能なスルーレート制御回路を提供すること。

【解決手段】制御時間設定回路がスルーレートを検出するタイミング信号を発生し、電圧比較回路が、出力アンプの出力信号と、上記のタイミング信号によるタイミングに応じた制御電圧との比較を行う。比較結果に応じて、出力アンプ制御回路が、出力アンプのバイアス電流を制御する。上記した処理を、スルーレート制御期間において複数回繰り返す。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】駆動回路76は、入力電位VIよりも所定電圧高い電位をノードN22に出力するレベルシフト回路61と、ノードN22の電位よりも所定電圧低い電位をノードN30に出力するプルアップ回路30と、入力電位VIよりも所定電圧低い電位をノードN27に出力するレベルシフト回路63と、ノードN27の電位よりも所定電圧高い電位をノードN30に出力するプルダウン回路33と、一方電極がそれぞれ信号φB,/φBを受け、他方電極がそれぞれノードN22,N27に接続されたキャパシタ76,77とを備える。入力電位VIの変化時、信号φB,/φBは、それぞれパルス的に「H」レベルおよび「L」レベルになる。したがって、低消費電流化と応答速度の高速化が図られる。

(もっと読む)

演算増幅回路

【課題】数多くの出力電圧レベルを出力可能で、かつ、製造ばらつきに伴う出力オフセット電圧を低減し得る演算増幅回路を提供する。さらに、出力オフセット電圧の低減精度が、入力電圧に依存しないようにする。

【解決手段】第1および第2の回路状態を切り替えるスイッチ群を設ける。n+1種類の出力電圧レベルを出力できるよう、n個の入力用差動対を設ける。第1の回路状態において、各入力用差動対に一対の入力電圧群を供給して、カレントミラー回路を介して出力オフセット電圧を容量に保持する。第2の回路状態において、容量に保持された電圧を用いて出力オフセット電圧をキャンセルする。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

差動増幅回路、レギュレータモジュール及びハイパワーアンプ

【課題】製造時の工程及び製品の消費電力の点で優れたレギュレータモジュール、及びそれを用いたバイアス回路を提供する。

【解決手段】パワーアンプモジュールとレギュレータモジュール801を含むパワーアンプをバイポーラトランジスタと電界効果トランジスタとを同一基板上に備える技術によって1チップで構成する。レギュレータモジュール801はデプリーション型トランジスタによる差動増幅回路を内包する。該差動増幅回路の一方のFETQ4のソース端子を、ダイオード接続したバイポーラトランジスタQ7を介して、FETQ3のソース端子と接続することで、バイポーラトランジスタQ7の電位差をレギュレータの出力電圧とすることが可能となる。

(もっと読む)

ソースフォロワ回路、ソースフォロワ型フィルタ回路

【課題】入力MOSトランジスタのオーバードライブ電圧が低い場合でも、出力信号が歪まないソースフォロワ回路を提供することを目的とする。

【解決手段】ソースフォロワ回路を、MOSトランジスタ(Tr)1、Tr2でなるTr対、ドレインがTr1のソース及び出力端子17に接続するTr3、ドレインがTr2のソース及び出力端子18に接続するTr4でなるTr対、ゲートとドレインがTr3のゲートに接続してTr3と電流ミラーを構成するTr7、Tr7のドレインに接続してTr7に電流を供給する電流源9、ゲートとドレインがTr4のゲートに接続してTr4と電流ミラーを構成するTr8、Tr8のドレインに接続してTr8に電流を供給する電流源10、Tr7のゲートと出力端子18との間に接続される容量素子11、Tr8のゲートと出力端子17との間に接続される容量素子12によって構成する。

(もっと読む)

電子回路

【課題】相補信号による差動出力のバイアス電圧のオフセットの入力信号に対する変化を抑制すること。

【解決手段】ベースに入力信号Vinが入力される第1トランジスタQ1と、ベースに前記入力信号を平滑化した平滑信号Vavgが入力され、エミッタが前記第1トランジスタのエミッタと共通接続された第2トランジスタQ2と、前記第1トランジスタおよび前記第2トランジスタのコレクタに接続され、相補出力をなす第1出力端子OUT1および第2出力端子OUT2と、前記第1トランジスタおよび前記第2トランジスタのそれぞれのコレクタと前記第2トランジスタのベースとの電位差をそれぞれ一定に保つ電位差生成回路20と、を具備する電子回路。

(もっと読む)

1 - 20 / 85

[ Back to top ]