Fターム[5J500AM17]の内容

Fターム[5J500AM17]に分類される特許

21 - 40 / 313

送信器

【課題】電力増幅器を高効率化及び高信頼性化する。

【解決手段】一つの実施形態によれば、送信器は、第1のバッファ、第2のバッファ、論理回路、及びE級電力増幅器が設けられる。第1のバッファは、第1の正弦波信号が入力され、第1の正弦波信号を第1の矩形波信号に変換する。第2のバッファは、第1の正弦波信号よりも位相が遅れた第2の正弦波信号が入力され、第2の正弦波信号を第2の矩形波信号に変換する。論理回路は、第1及び第2の矩形波信号が入力され、第1及び第2の矩形波信号を論理演算して所定のデューティーを有するロジック信号を生成する。E級電力増幅器は、ロジック信号が入力され、ロジック信号に基づいて増幅動作する。

(もっと読む)

プリアンプ回路、及びマイクロフォン

【課題】低ノイズ特性を持つプリアンプ回路を提供すること

【解決手段】プリアンプ回路は、ソースフォロアとして機能するPMOSトランジスタM1A及びM1Bを備える。さらにプリアンプ回路は、差動増幅器として対となって機能するPMOSトランジスタM2A及びM2Bを備える。M1AのゲートとM2Bのゲートとが、可変容量C2を介して接続される。M1BのゲートとM2Aのゲートとが、可変容量C1を介して接続される。M1Aのソースと、M2Aのドレインと、が接続される。M1Bのソースと、M2Bのドレインと、が接続される。M2Aのソースと、M2Bのソースと、が接続される。

(もっと読む)

低雑音増幅器

【課題】低雑音増幅器の周波数帯域を拡大すること。

【解決手段】入力信号がゲートに供給されるソース接地トランジスタと、前記ソース接地トランジスタのドレイン電流が供給される第1の負荷とを有する増幅回路と、前記入力信号がソースに供給されるゲート接地トランジスタと、前記ゲート接地トランジスタのドレイン電流が供給される第2の負荷とを有する終端回路と、前記ゲート接地トランジスタのソースとドレインの間に接続されたアクティブインダクタとを有すること。

(もっと読む)

演算増幅回路

【課題】セトリング速度を向上させる。

【解決手段】差動入力信号を増幅する差動対(M1、M2、M19)と、差動対の一方および他方の出力端にそれぞれ接続される一方および他方のカスコード増幅器対(M9、M10)と、カスコード増幅器対の一方および他方の出力端にそれぞれゲートを接続し、差動対の一方および他方の出力端にそれぞれドレインを接続するソース接地の第1のMOSトランジスタ対(M11a、M12a)と、を備える。カスコード増幅器対の一方および他方の出力端にそれぞれゲートを接続し、差動対の他方および一方の出力端にそれぞれドレインを接続する、第1のMOSトランジスタ対と同一の導電型であるソース接地の第2のMOSトランジスタ対(M3a、M4a)をさらに備える。

(もっと読む)

出力回路

【課題】より十分な出力電流を流せる出力回路を提供する。

【解決手段】PMOSトランジスタ12のドレイン電流が大きい場合、PMOSトランジスタ13は非飽和領域で動作する。このときNMOSトランジスタ14及び17のゲート電圧は電源端子電圧付近まで上昇している。このため、NMOSトランジスタ17のゲート・ソース間電圧は大きくなり、十分な出力電流が流れる。

(もっと読む)

集積フィルタを備えた増幅器

【課題】良好な雑音性能を有しかつ大きい干渉信号に対処できる増幅器を提供する。

【解決手段】集積フィルタを備えた増幅器320b(例えば,LNA)は利得ステージ330、フィルタ・ステージ340およびバッファ・ステージ350を含んでいてもよい。利得ステージは、入力信号に対して信号増幅を提供する。フィルタ・ステージは、入力信号に対してフィルタリングを提供する。バッファ・ステージは、フィルタ・ステージからのフィルタされた信号をバッファする。増幅器は、第2のフィルタ・ステージ360及び第2のバッファ・ステージ370をさらに含んでいてもよい。

(もっと読む)

高周波電力増幅器

【課題】従来よりも高効率で消費電力を抑えることが可能な高周波電力増幅器を提供する。

【解決手段】ソース接地され、ゲート端子が、信号が入力される入力ノードに接続された入力側トランジスタ10と、ゲート接地され、ソース端子が、入力側トランジスタ10のドレイン端子に共通に接続され、且つドレイン端子が、出力信号が出力される出力ノードに接続された複数の出力側トランジスタ20,30とを備え、各出力側トランジスタ20,30は、それぞれが異なるゲート・ソース間電圧によりバイアスされている構成とする。

(もっと読む)

演算増幅回路

【課題】電流源の誤差やカレントミラーのミラー精度の誤差による同相出力電圧の出力オフセット電圧を補正し、より正確に同相出力電圧を制御することができる演算増幅回路を提供する。

【解決手段】入力切替回路14がコモンモード参照電圧を選択してコモンモード基準電圧として出力したときの全差動増幅回路10の同相出力電圧をコモンモード検出回路11が検出した後、S/H回路12がコモンモード検出回路11の出力のサンプル及びホールドを行い、演算回路13がS/H回路12の出力とコモンモード参照電圧とのずれ量とコモンモード参照電圧とに基づく電圧を出力し、入力切替回路14が演算回路13の出力を選択してコモンモード基準電圧として出力する。

(もっと読む)

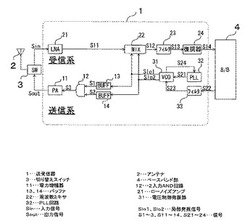

全二重伝送回路、及び電子機器

【課題】消費電力を低減すること。

【解決手段】送信信号が入力される第1の内部入力端子と、送信信号に比べて振幅が1/2であり、かつ、送信信号と同相の信号が入力される第2の内部入力端子と、特性インピーダンスZを有する伝送路に接続された外部入出力端子と、外部入出力端子から入力された受信信号が出力される内部出力端子と、ソースが電流源及び外部入出力端子に接続され、ゲートが第1の内部入力端子に接続され、ドレインが第2のMOSトランジスタのソース及び内部出力端子に接続された第1のMOSトランジスタと、ソースが第1のMOSトランジスタのドレイン及び内部出力端子に接続され、ゲートが第2の内部入力端子に接続された第2のMOSトランジスタと、を備え、第1及び第2のMOSトランジスタのトランスコンダクタンスが1/Zとなる、全二重伝送回路が提供される。

(もっと読む)

入れ子状のトランスインピーダンス増幅器

【課題】光ファイバ受信器やハードディスクドライブ向けに、大きい帯域幅及び高利得TIAを提供する。

【解決手段】入れ子状のトランスインピーダンス増幅器(TIA)回路は、入力及び出力を有する0次のTIAと、第1の演算増幅器(オペアンプ)と、を備えている。オペアンプは、0次のTIAの出力に接続する入力と、該入力によって駆動される第1のトランジスタと、第1のバイアス電圧によって駆動され且つ上記第1のトランジスタに接続する第2のトランジスタと、第2のトランジスタに接続する第1の電流源と、第1のトランジスタと第2のトランジスタの間のノードに存在する出力と、を備えている。

(もっと読む)

ボルテージレギュレータ

【課題】正確な出力電圧を得る事ができる位相補償回路を有するボルテージレギュレータを提供する。

【解決手段】位相補償回路を出力トランジスタのゲートに接続される第一の定電流回路と、ドレインが出力トランジスタのゲートに接続された第一のトランジスタと、ドレインが第一のトランジスタのゲート及び第二の定電流回路及び抵抗に接続され、ゲートが抵抗及び第一の容量に接続される第二のトランジスタと、もう一方が出力端子に接続される第一の容量で構成する。こうすることで、差動増幅回路の出力端子から第一のトランジスタのドレインへ電流が流れる事を防止することができ、差動増幅回路の入力トランジスタに発生するオフセット電圧が低減され、正確な出力電圧を得ることできる。

(もっと読む)

単一のプロセスを用いて高性能ロジックおよびアナログ回路をイネーブルするプロセス/設計方法論

【課題】混合信号プロセスにおいてアナログ回路の性能を向上させる方法および装置を提供すること

【解決手段】順方向バイアスおよび修正された混合信号プロセスを用いた回路設計を用いて、アナログ回路性能を向上させる方法が提示される。複数のNMOSトランジスタおよびPMOSトランジスタを含む回路が規定される。NMOSトランジスタのボディ端子は、第1の電圧ソースに連結され、PMOSトランジスタのボディ端子は、第2の電圧ソースに連結される。回路内のトランジスタは、各選択されたNMOSトランジスタのボディ端子に該第1の電圧ソースを適用することと、各選択されたPMOSトランジスタのボディ端子に該第2の電圧ソースを適用することとによって、選択的にバイアスされる。一実施形態において、第1の電圧ソースおよび第2の電圧ソースは、順方向バイアスおよび逆方向バイアスをトランジスタのボディ端子に提供するように修正可能である。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

広帯域増幅器

【課題】RFで動作するシングルエンド出力であるフィードバック型の広帯域増幅器における二次歪み耐性を向上させる。

【解決手段】主増幅MOSトランジスタQ1を含むシングルエンド出力であるフィードバック型の主増幅器310における電圧−電流変換抵抗素子R1と並列に主増幅器310とは逆極性のMOSトランジスタで構成されたバイパス回路320を設け、このバイパス回路320の副増幅MOSトランジスタQ3へのバイアス値を所定値に合わせ込むことによって、主増幅器310に生じる二次歪成分のみに対し逆極性で且つ相似な特性を呈するバイパス作用信号を生成し、該バイパス作用信号で主増幅器310に生じる二次歪成分をバイパス回路320側に引き込むことによって、主増幅器310とバイパス回路320とを含む広帯域増幅器300の二次歪み耐性を向上させる。

(もっと読む)

金属検出システム作動方法及び金属検出システム

【課題】2つ以上の送信周波数を使用する金属検出システムを提供する。

【解決手段】少なくとも2つの送信周波数グループから選択される送信周波数を有する送信信号を生成する送信装置3と接続される送信コイル4と、受信装置5に含まれる少なくとも1つの増幅装置14,15の信号入力へ出力信号を提供し、出力信号が、システムが平衡状態にあるように相互に相殺する第1及び第2の受信コイル6,7とを備えた、平衡コイルシステムを含む金属検出システム1を作動させる。制御装置16が、少なくとも1つの増幅装置14,15の信号入力と接続される少なくとも1つの制御可能インピーダンス装置12,13の制御入力に提供される制御信号を送信装置3の送信周波数に従って生成し、送信周波数が増減されるとき、インピーダンス値が増減されるような方法で制御信号が、制御可能インピーダンス装置12,13のインピーダンス値を制御する。

(もっと読む)

電流電圧変換回路

【課題】回路構成を簡素化した電流電圧変換回路を提供することである。

【解決手段】NPNトランジスタQ1のエミッタとPNPトランジスタQ2のエミッタとが入力端子INに接続される。NPNトランジスタQ1のコレクタが定電源V1ラインに接続され、PNPトランジスタQ2のコレクタが電源C2ラインにされる。NPNトランジスタQ1のベースと、PNPトランジスタQ2のベースとの間に、バイアス回路20が接続され、フローティング状態とされる。

(もっと読む)

光受信回路用のトランスインピーダンスアンプ

【課題】電源電圧の変動に関わらず、クロスポイントのシフト幅を安定させることが可能な光受信回路用のトランスインピーダンスアンプを提供する。

【解決手段】TIA15は、互いに直列に接続された負荷抵抗23、入力FET22及びカスコードFET21を含み、入力FET22のゲート端子が入力端15aに接続された入力部20と、互いに直列に接続されたソースフォロワFET31及び電流源FET33を含み、ソースフォロワFET31のゲート端子にカスコードFET21のドレイン電圧を受けるとともに、ソースフォロワFET31のソース端子が帰還抵抗34を介して入力端15aに接続されたソースフォロワ部30と、電流源FET33のゲートバイアスを生成するバイアス生成部40とを備える。電流源FET33を流れる電流は、電源電位線18における電源電圧の大きさに基づいて可変とされている。

(もっと読む)

広帯域増幅器

【課題】RF(Radio Frequency)で動作する、シングルエンド出力であるフィードバック型の広帯域増幅器において、特に二次歪み耐性に優れたフィードバック型の広帯域増幅器を実現する。

【解決手段】入力信号を電圧−電流変換して出力するMOSトランジスタQ1の出力電流を第1の抵抗素子R1によって出力電圧に変換し、該出力電圧をMOSトランジスタQ1の入力に第2の抵抗素子R2によってフィードバックする。さらに、第1のバイアス回路(VG1+R3)からMOSトランジスタQ1の入力へバイアスを供給する。そして、このバイアス値を、MOSトランジスタQ1のドレイン電流が流れるように、且つ、MOSトランジスタQ1のドレイン電流をゲート電圧で二回微分した成分の絶対値が極小となるように設定する。

(もっと読む)

スイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システム

【課題】精度および高速性能を損なうことなくアンプシェア動作を実現可能なスイッチドキャパシタ増幅回路、パイプライン型AD変換器、および信号処理システムを提供する。

【解決手段】複数のスイッチドキャパシタ回路210,220で共有される演算増幅器AMP11を有し、複数のスイッチドキャパシタ回路は演算増幅器の入力および出力と切り離すように複数のスイッチが制御されて複数の容量で第1のアナログ信号をサンプリングするサンプルモードと、サンプリングした容量を演算増幅器の入力および出力と選択的に接続するように複数のスイッチが制御されて、演算増幅器のサンプルモードでサンプリングした信号と第2のアナログ信号との差分を2N倍に増幅するホールドモードとが相補的に設定され、サンプルモード時に演算増幅器の入力および演算増幅器の内部における電圧が固定されていないノードを共通電位にリセットするスイッチswrを有する。

(もっと読む)

パススルー付き増幅器

【課題】パススルーモード時の通過特性を向上できかつ低電源電圧化に対応できるパススルー付き増幅器を提供する。

【解決手段】パススルーモード時に、信号伝達用トランジスタ(M1)とともにバイアス制御用トランジスタ(M2)をオンさせて、出力端子OUTの電圧をバイアス制御用トランジスタ及び抵抗(R1)を介してグランド電位に維持させる。これにより、信号伝達用トランジスタの制御端子には電源電圧が印加され、信号伝達用トランジスタの一方の主端子はグランド電位に維持されるので、信号伝達用トランジスタのオン抵抗が最大限に減少する。

(もっと読む)

21 - 40 / 313

[ Back to top ]