Fターム[5J500AM17]の内容

Fターム[5J500AM17]に分類される特許

61 - 80 / 313

エラーアンプの位相補償回路

【課題】 ICチップ上のコンデンサ面積を小さくすることができる位相補償回路を提供する。

【解決手段】 エラーアンプの出力端子に容量と抵抗を直列接続し、容量に流れる電流を抵抗の両端に接続したトランスコンダクタンスアンプにより増幅してフィードバックすることにより、エラーアンプの周波数特性の主要極の周波数を低くする。

(もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

出力回路

【課題】構成素子数を最小限に抑えて消費電流の増加を抑え、且つ過渡応答時のクロスオーバー歪を改善する。

【解決手段】NチャネルMOSトランジスタM1,M2,M6と、PチャネルMOSトランジスタM3,M4,M5を備える出力回路において、ドレインとゲートがMOSトランジスタM2のドレインおよびトランジスタM5のゲートに接続され、ソースがMOSトランジスタM4のドレインに接続されたMOSトランジスタM7を設けた。

(もっと読む)

差動増幅回路及び液晶ディスプレイドライバ

【課題】線形領域で高精度に動作する差動増幅回路及びこの差動増幅回路を用いた液晶ディスプレイドライバを提供する。

【解決手段】差動増幅回路は、入力電圧V1がゲート端子に与えられるトランジスタM1及びM2と、トランジスタM1のソース端子にドレイン端子が接続されるトランジスタM3、トランジスタM3のゲート端子に入力電圧V1を与えるか否か切り替えるスイッチS1、トランジスタM3のゲート端子に入力電圧V2を与えるか否か切り替えるスイッチS2、及びトランジスタM2のソース端子にドレイン端子が接続され、ゲート端子に入力電圧V3が与えられ、ソース端子がトランジスタM3のソース端子と接続されるトランジスタM4をそれぞれ有する複数の差動対D1〜D4と、差動対D1〜D4のトランジスタM3、M4のソース端子に電流を供給する電流源I1と、を備える。

(もっと読む)

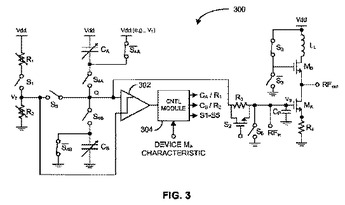

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】回路ゲイン切り替え時における入力端子の入力容量値の変動を低減し、周波数依存性を大幅に改善する。

【解決手段】スイッチ22(0〜N),23(0〜N),24(0〜N)におけるON/OFFの動作制御は、ロジックコントローラから出力される制御信号Ctrl0〜Ctrln,CtrlB0〜CtrlBnによってそれぞれ制御される。スイッチ24(0〜N)は、スイッチ22(0〜N)がON(トランジスタ19(0〜N)がバイアスオフ)する際に、同じタイミングでONとなり、スイッチ22(0〜N)がOFF(トランジスタ19(0〜N)がバイアスオン)する際には、同じタイミングでOFFとなる。トランジスタ24(1〜N)がバイアスオフのときに静電容量素子25(0〜N)が有効になり、回路ゲインを切り換えた時の入力端子INから見た入力容量値Cinの大きな変動を防止することができる。

(もっと読む)

演算増幅器および演算増幅装置

【課題】低消費電流でかつ十分な位相余裕を有して、高速動作することが可能な演算増幅器を提供する。

【解決手段】演算増幅器に、差動増幅器203の出力電圧に応じた抵抗を有する抵抗用MOSトランジスタ17を設ける。そして、抵抗用MOSトランジスタ17の抵抗値を、制御回路20によって調整する。さらに、制御回路20を、抵抗用MOSトランジスタ17と同じ抵抗値を有する制御用MOSトランジスタ201に接続される反転入力端子と、リファレンス信号が印加される非反転入力端子、抵抗用MOSトランジスタ17のゲート及び制御用MOSトランジスタ201のゲートに接続される出力端子とを有する差動増幅器203、図1のMOSトランジスタ16のトランスコンダクタンス値に比例したトランスコンダクタンス値を有し、差動増幅器203の反転入力端子に出力信号を供給するトランスコンダクタンスアンプ202によって構成する。

(もっと読む)

低ドロップアウト線形レギュレータ(LDO)、LDOを提供するための方法、およびLDOを動作させるための方法

【課題】PSRRが改良された低ドロップアウト線形レギュレータを提供する。

【解決手段】LDOは、差動増幅器と調整されたカレントミラーとを結合し、それぞれ差分信号を受信するように構成された2つのノードを有する。調整されたカレントミラーは、差分信号をシングルエンド信号に変換および増幅するように構成される。LDOは、周波数補償用に構成された第1のコンデンサを有し、第1のコンデンサは、第1の段と第2の段との間に結合される。LDOは、第1のカスコード回路の容量性負荷を平衡化するための第2のコンデンサを有し、第2のコンデンサは、第1の段と電源電圧との間に結合される。第1のカスコード回路は、電源電圧の変動によって生じるコンデンサの入出力間の差電圧を抑制するように構成される。LDOは、差動増幅器の電源の変動を抑制するように構成された第2のカスコード回路を有する。

(もっと読む)

電力増幅器及びその製造方法

【課題】低耐圧のトランジスタを用いた高出力の電力増幅器を提供すること。

【解決手段】本発明に係る電力増幅器は、制御端子に第1の入力信号が入力される第1のトランジスタ6と、第1のトランジスタ6と縦列接続され、制御端子に第2の入力信号が入力される第2のトランジスタ10とを備え、第1の入力信号と第2の入力信号とが、同期し、かつ、同位相であるものである。これにより、出力電圧が、最大電圧振幅時に、第1のトランジスタ6と第2のトランジスタ10とに略均等に分割して印加される。

(もっと読む)

入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システム

【課題】 入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システムを提供する。

【解決手段】 本発明は、入力段(EE)及び出力段(ES)を含む入力信号の電力増幅用回路(CIR)に関し、前記入力段(EE)は:

―いわゆる主駆動トランジスタ(T3)を組み込んでいる駆動手段(MP)と、

―入力信号を受信可能で、主駆動トランジスタ(T3)と共に電流ミラーとして組み立てられた、第1のいわゆる主入力トランジスタ(T1)とを備える。

第1の主入力トランジスタ(T1)は、入力段(EE)内へ組み込まれた第2のいわゆる主入力トランジスタ(T2)を介して出力段(ES)に連結され、かつ駆動手段(MP)によって制御され、第1の主入力トランジスタ(T1)と第2の主入力トランジスタ(T2)は相互に連結され、かつ共振回路(BB2,Cp)を経由してDarlington型の構造に従ってアースに連結される。

(もっと読む)

可変利得増幅器

【課題】利得を変化させた際の出力インピーダンスの変動を抑える可変利得増幅器を得る。

【解決手段】ゲートバイアスが供給されるゲートが入力端子1と接続され、入力された信号を増幅するソース接地型増幅素子3と、一端からドレインバイアスが印加される複数の並列抵抗63を有するとともに、並列抵抗63の他端間を結ぶ複数の直列抵抗62を有するラダー抵抗回路61と、ゲートバイアスが供給されるゲートが高周波的に接地され、ドレインがラダー抵抗回路61における各並列抵抗の他端と接続され、ソースがソース接地型増幅素子3のドレインと接続され、複数のゲート接地型増幅素子51〜5nと、複数のゲート接地型増幅素子のいずれかのドレインに接続された出力端子12と、複数のゲート接地型増幅素子のゲートと接続され、ゲートバイアスを選択的に供給するゲートバイアス制御回路6とを備える。

(もっと読む)

差動増幅器

【課題】非反転入力端子の電圧が変化した場合でも、出力トランジスタに流れる電流を一定にすることができる、差動増幅器を提供する。

【解決手段】非反転入力端子143と、反転入力端子144と、P型MOSトランジスタ107及び108とN型MOSトランジスタ101及び102と定電流源121とからなる差動増幅回路と、P型MOSトランジスタ103及び104とN型MOSトランジスタ113及び114と定電流源122とからなる差動増幅回路と、P型MOSトランジスタ107及び108に電流を流す定電流源124とで構成される相補型フォールデッドカスコード増幅回路に、さらにP型MOSトランジスタ107及び108に電流を流す電流制御回路である、定電流源123とN型MOSトランジスタ105を備え、相補型差動対の負荷であるカスコード増幅回路に流れる電流を、非反転入力端子の電圧によって制御する構成とした。

(もっと読む)

増幅回路

【課題】出力トランジスタに直列にトランジスタを接続し、このトランジスタに入力信号を入力すると共に、このトランジスタによって出力トランジスタをドライブするカスコード構成の増幅回路では、出力トランジスタのベース電位は固定されていた。このため、電源電圧が高くなると出力トランジスタの消費電力が増大し、その規格を越えてしまうという課題があった。本発明は、電源電圧が高くなっても出力トランジスタの消費電力が増大しない増幅回路を提供することを目的にする。

【解決手段】電源電圧が入力され、この電源電圧に基づいて出力トランジスタのベース電位を決定すると共に、電源電圧の変動に連動して、前記出力トランジスタのベース電位を変化させる電圧帰還回路を具備した。電源電圧が高くなると出力トランジスタのベース電位も高くなるので、出力トランジスタの消費電力を低減することができる。

(もっと読む)

ESD保護を有する集積電子回路を設計する方法及びそれにより得られる回路

【課題】電子静電放電保護を有する集積電子回路を設計する方法を提供する。

【解決手段】通常の動作の間の所与のパフォーマンスを有する集積電子回路1を設けるステップを含み、集積電子回路1は、電力供給ライン2と、電力供給ライン2により電力供給され、電子静電放電保護装置5により保護される少なくとも一つの能動装置4とを含み、更に、集積電子回路1上でESDイベントをシミュレートして、ESDイベントの間に、寄生ESD電流経路が、電力供給ライン2と少なくとも一つの機能装置4との間で形成されるかどうか、及びどこで形成されるかを、決定するステップと、決定された寄生ESD電流経路内で、少なくともESDイベントの一部の間に、この寄生ESD電流経路を遮断する回路6を形成するステップとを含む。

(もっと読む)

出力回路

【課題】出力電流吸込み時における消費電流の増加を抑え、かつ過渡応答時のクロスオーバー歪を改善した出力回路を提供する。

【解決手段】NチャネルMOSトランジスタM1、M2,M6と、PチャネルMOSトランジスタM3,M4,M5を備える出力回路において、ドレインがトランジスタM3のドレインに接続され、ソースがトランジスタM1のドレインに接続されたNチャネルMOSトランジスタM7と、ゲートがトランジスタM5のゲートに接続され、ソースが正電源端子+Vに接続されたPチャネルMOSトランジスタM8と、ゲートがトランジスタM7のゲートに接続され、ドレインがトランジスタM8のドレインに接続され、且つゲートとドレインが共通接続されたNチャネルMOSトランジスタM9と、トランジスタM9のソースと負電源端子−Vとの間に接続した電流源I1と、を設けた。

(もっと読む)

カスコード回路

【課題】RF高効率高出力電力増幅とともに、低ひずみ化の可能性をも併せ持つカスコード回路を提供する。

【解決手段】カスコード回路の両FET(または両バイポーラトランジスタ)の接続部にバイアス電圧を印加することで、ソース接地FETにおけるゲートバイアス電圧(またはエミッタ接地バイポーラトランジスタにおけるベースバイアス電圧)と、RFゲート接地FETにおけるドレーンバイアス電圧(またはベース接地バイポーラトランジスタにおけるコレクタバイアス電圧)とを、独立に設定できる。特に、これらのバイアス電圧を、ソース接地FET(またはエミッタ接地バイポーラトランジスタ)がB級動作ないし深いAB級動作をし、かつ、交流ゲート接地FET(または交流ベース接地バイポーラトランジスタ)が浅いAB級動作ないしA級動作をする組み合わせに設定する。

(もっと読む)

共通のバイアス電流をシェアする複数の増幅ステージを用いて信号を増幅するシステム及び方法

装置は、共通のDC電流によってバイアスされ、入力信号から増幅された出力信号を発生するように適応されたカスケードの増幅ステージを含む。第1の増幅ステージは、入力電圧信号を実質的に2倍にするルーティングネットワークと、入力電圧信号から第1の電流信号を発生する第1の相互コンダクタンスゲインステージとを含む。第2の増幅ステージは、第1の電流信号を第2の電圧信号に変換する共振器と、第1の電流信号から第2の電流信号を発生する第2の相互コンダクタンスステージとを含む。第3の増幅ステージは、第2の電流信号から第3の電流信号を発生する電流ゲインステージと、第3の電流信号が流れて出力信号を発生する負荷とを含む。  (もっと読む)

(もっと読む)

線形化回路及び電力増幅のための方法

本発明の線形化回路は、電力増幅器コアを有する電力増幅回路に関連して使用する。例示的な線形化回路は、電力増幅器コアのレプリカを備える。線形化回路はその動作にあたり、RF信号からエンベロープ信号を生成する。このエンベロープ信号を使用して、レプリカを制御することによりアナログ出力信号を生成し、このアナログ出力信号は、電力増幅器コアにおけるAM‐AM変換歪みの反転を表す。その後、線形化回路は、レプリカにおける反転した非線形信号でRF信号をバイアスし、電力増幅コアを制御する。電力増幅器コア及びそのレプリカは、いずれも同一半導体のダイ上に配置することができるため、双方ともに、製造プロセス変動に対して同様の応答を示す。 (もっと読む)

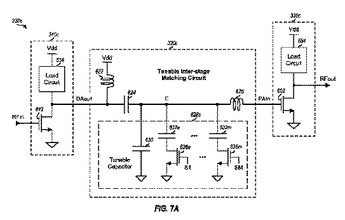

デジタルのチューナブル段間整合回路

性能を改善できるチューナブル段間整合回路について説明する。例示的な設計では、装置は、第1の能動回路(たとえば、ドライバ増幅器)と、第2の能動回路(たとえば、電力増幅器)と、第1の能動回路と第2の能動回路の間に接続されたチューナブル段間整合回路とを含む。このチューナブル段間整合回路は、第1の能動回路と第2の能動回路の間のインピーダンス整合を調整するために個別のステップで変化できるチューナブルキャパシタを含む。例示的な設計では、このチューナブルキャパシタは、(i)並列に接続された複数のキャパシタと、(ii)この複数のキャパシタに対してキャパシタごとに1つ接続された複数のスイッチとを含む。各スイッチは、関連するキャパシタを選択するためにオンにされるか、または関連するキャパシタの選択を解除するためにオフにされることができる。チューナブルキャパシタは、複数のキャパシタと並列に接続された固定キャパシタをさらに含むことができる。  (もっと読む)

(もっと読む)

ダイオードベースバイアス有りスタックアンプ(stackedamplifier)

アンプの直線性を改善するための技術が述べられる。典型的な設計では、アンプ(例えば、パワーアンプ)は、スタック内に結合された複数のトランジスタと、少なくとも一つのダイオードを含む。前記複数のトランジスタでは、入力信号を受信して増幅する出力信号を提供する。少なくとも一つのダイオードがスタック内の少なくとも一つのトランジスタに動作可能なように結合される。各ダイオードは、スタック内の関連付けられたトランジスタに可変バイアス電圧を提供する。各ダイオードは、高入力パワーでダイオードの両端で電圧降下を有し、そして、高入力パワーで関連付けられているトランジスタに高バイアス電圧を提供する。少なくとも一つのトランジスタは、少なくとも一つのダイオードから高バイアス電圧に起因する高入力パワーで高ゲインを有する。高ゲインはアンプの直線性を改善する。  (もっと読む)

(もっと読む)

61 - 80 / 313

[ Back to top ]