Fターム[5K020GG01]の内容

スーパーヘテロダイン受信機 (8,436) | 回路(局部発振回路) (952) | PLL系の局部発振回路 (545)

Fターム[5K020GG01]の下位に属するFターム

複数のループを持つもの (11)

VCO (131)

前置周波数逓降回路 (15)

プログラマブル可変分周器 (27)

位相比較回路 (53)

基準周波数発生回路 (64)

LPF (45)

ロック、アンロックの検出 (3)

Fターム[5K020GG01]に分類される特許

21 - 40 / 196

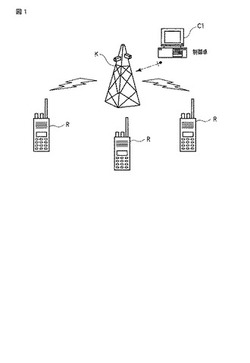

無線機

【課題】基地局からのトーン信号に基いて周波数調整を行うアナログ方式の無線機を提供する。

【解決手段】基地局とアナログ無線通信を行う通信部14と、通信部から受けたトーン信号に基き、通信部を周波数調整用チャンネルに切り換えて基地局から調整用周波数を受信し、この調整用周波数に基いて周波数調整を行う制御部20をもつ無線機。

(もっと読む)

ダイナミックな中間周波数スケーリングを有する無線デバイス

無線デバイス内の中間周波数(IF)信号のダイナミックな周波数スケーリングに対して、方法及び装置が提供される。  (もっと読む)

(もっと読む)

受信装置およびチューナ

【課題】チューナの高速動作が実現可能であると共に、受信装置の各性能を的確に最適化することが可能である、受信装置およびチューナを実現する。

【解決手段】受信した無線周波信号に応じた検波用無線周波信号111を検波して得られた第1デジタル値116と、中間周波信号106に応じた検波用中間周波信号109を検波して得られた第2デジタル値117と、を記憶する記憶部119と、第1デジタル値116および第2デジタル値117を、一定時間毎に、記憶部119に記憶させる記憶処理部121と、記憶部119に第1デジタル値116および第2デジタル値117が記憶される度に、PLL回路104のロック周波数を、1チャンネル周波数帯域に相当する分上昇させる発振周波数変化処理部122と、を備える。

(もっと読む)

低転送速度モードにおける感度が高いFSK変調信号受信機

【課題】低転送速度モードにおける感度が高いFSK変調信号受信機を提供する。

【解決手段】FSK変調信号のための受信機は、アンテナと、低雑音増幅器と、水晶共振器を含んでいて高周波同相信号SIおよび高周波直角位相信号SQを供給する局部発振器6と、高周波同相信号および直角位相信号と、フィルタリングされ且つ増幅された入力信号とを混合して、中間信号Im、Qmを生成する第1および第2のミキサ4、5と、中間信号をフィルタリングするフィルタリング・ユニット12とを備えている。フィルタリング・ユニットは、多相フィルタ13においてフィルタリングされた中間信号IF、QFを中間若しくは高転送速度モードで第1の復調段に供給し、または2つの低域通過フィルタ14、15に転換された多相フィルタにおいてフィルタリングされた中間ベースバンド信号を低転送速度モードで第2の復調段に供給する。

(もっと読む)

信号伝送装置及び信号伝送方法

【課題】 高速ディジタル信号伝送において周波数変動の影響や発振回路に起因する位相雑音の影響を除去し、信頼度の高い信号伝送を可能にする。

【解決手段】 IF信号を主にマイクロ波帯に変換して伝送する信号伝送装置において、主信号にSynthesizerで生成された互いの周波数差が基準周波数に等しいパイロット信号fp1s、fp2sを付加して変調して送信する。受信側ではこの信号を受信、復調して、主信号fIF22とパイロット信号fP1r'、fP2r'とに分波してのち、パイロット信号fP1r'とfP2r'との周波数差から基準周波数信号fREF2を再生すると共に、この基準周波数信号をもとにパイロット信号fP2r'を修正したパイロット信号fP2rを生成して、このパイロット信号fP2rによって主信号fIF22からパイロット信号成分を完全に除去して、乱れのない主信号成分を得る。

(もっと読む)

受信装置

【課題】受信チャンネルの周辺に位置する妨害信号の影響を小さくして、妨害耐性を向上させることができる受信装置を提供すること。

【解決手段】同調周波数をシフト可能なRF同調回路2と、複数のチャンネルを含む所定の受信周波数範囲をスキャンして、信号レベル分布を記憶するメモリ13と、チャンネル受信時に、信号レベル分布に現れた受信チャンネル周辺の妨害信号レベルに応じて、受信チャンネルに対するRF同調回路2の同調周波数をシフトする構成した。

(もっと読む)

ラジオ受信機、該受信機に内蔵された混信除去回路、及び該混信除去回路を用いた混信除去方法

【課題】ラジオ受信機のIF信号に含まれる希望局の上下の隣接局による混信成分を除去し、混信のない復調出力を得る。

【解決手段】フロントエンド3からのIF信号をデジタル変換後に、3つの同期検波回路5,25,35で検波して、希望局のUSBとLSBを生成すると共に、希望局の上側の隣接妨害局のUSBと希望局の下側隣接妨害局のLSBを生成し、希望局のUSBから上側の隣接妨害局のUSBを減算して、希望局のUSBに含まれる上側の隣接妨害局の成分を除去し、希望局のLSBから下側の隣接妨害局のLSBを減算して、希望局のLSBに含まれる下側の隣接妨害局の成分を除去することにより、隣接局による混信のない希望局の音声信号を生成することができるラジオ受信機である。

(もっと読む)

チューナ部とこれを用いた高周波受信部および高周波受信機器

【課題】弱電界においても良好な受信感度を有するチューナ部を実現する。

【解決手段】高周波信号が一方の入力に供給される混合器117と、この混合器117の他方の入力に発振信号を供給する発振器123と、この発振器123の発振周波数をPLL制御するPLL回路125と、混合器117からの出力信号が供給される出力端子113を備え、PLL回路125に対して基準信号を発生する基準発振器126と、この基準発振器126からの発振信号が供給されるとともに電気信号を光信号に変換する電気光変換器128と、この電気光変換器128から出力される光信号を電気信号に変換する光電気変換器130を設け、光電気変換器130の出力をPLL回路125の一方の入力に近接して接続する。

(もっと読む)

電子装置

【課題】周波数がクロック周波数の整数倍である高調波に起因する帯域内スプリアスによる受信性能劣化を抑制可能な電子装置を提供する。

【解決手段】局所発振信号の周波数をfLO、整数をN、受信信号の下限周波数をfD1、受信信号の上限周波数をfD2とするとき、fLO=N×fclk (1)と(N−1)×fclk<fD1<N×fclk<fD2<(N+1)×fclk (2)とが成立する。これにより、周波数が上記クロック周波数fclkの整数倍である高調波成分が、スプリアスとして希望信号の経路に混入しても、ミキサーによる周波数変換後の希望波の帯域内には入らない。従って、周波数がクロック周波数の整数倍である高調波に起因する帯域内スプリアスによる受信性能劣化を抑制可能となる。

(もっと読む)

チューナモジュール

【課題】Low−IFアーキテクチャを採用したチューナモジュールにおいて受信妨害の影響を抑制する。

【解決手段】局部発振信号を発振する局部発振回路17と、地上テレビジョン放送における選局チャンネルの帯域外の信号レベルが低減されたRF信号と局部発振回路17から発振される局部発振信号とを混合してこのRF信号を低周波の中間信号にダウンコンバートする混合回路14と、局部発振回路17が発振する局部発振信号の局部発振周波数を選局チャンネルの帯域内において受信妨害の影響が抑制される値にする制御を行う制御回路16とを備える。

(もっと読む)

周波数変換装置

【課題】小型かつ低コストであり、受信された放送波信号を、その信号スペクトルを反転させた後に、ベースバンド複素信号に変換することが可能な周波数変換装置を提供する。

【解決手段】アナログ−デジタル変換部11は、局部発振器111から出力されるfs/2<f<fsの要件を満たす周波数fsの局部発振信号を利用して、IF信号をデジタル信号へ変換する。直交復調部12では、デジタル変換の際にfs/2を基準に折り返されて生成されたイメージ信号をデジタルIF信号とする。DDS121からはこのデジタルIF信号の周波数の正弦波及び余弦波が出力され、この正弦波及び余弦波をミキサ122,123でデジタルIF信号に乗じる。正弦波及び余弦波が乗じられたデジタルIF信号は、LPF124,125を通過することで、不要信号成分が抑圧され、ベースバンドI/Q信号となり、信号処理部20へ供給される。

(もっと読む)

無線受信回路

【課題】同調回路の選択度を高くすることである。

【解決手段】フロント同調回路11とその後段の同調回路12の可変容量素子Cfa、Caaは、局部発振回路13の制御電圧VT0により容量値が制御される。また、フロント同調回路11と同調回路12の微調整用可変容量素子Cfb、Cabは、RSSI信号に基づいて生成される制御電圧VT1、VT2に容量値が制御される。これにより、フロント同調回路11と同調回路12の可変容量素子の容量値のバラツキの影響を抑えることができる。

(もっと読む)

受動無線受信機

入力信号を受信しその入力信号を受動的に処理して出力信号を発生する受動無線受信機。この受動受信機の実施例は入力回路、ダイナミックスイッチング回路、スイッチ信号発生器を含む。この入力回路は入力信号を受信して第1の出力信号を発生するように構成される。入力回路はその入力信号に条件付けするように構成された受動ネットワークを含む。このダイナミックスイッチング回路は第1の出力信号に対して周波数変換を行なうように構成される。スイッチ信号発生器は、周波数制御回路によって制御され安定化されるサンプリング周波数でダイナミックスイッチング回路を活性化及び非活性化するようにダイナミックスイッチング回路を駆動するように構成される。 (もっと読む)

無線受信機及び無線受信機の制御方法

【課題】帯域拡張型の無線信号の受信およびホッピング型の無線信号の受信においてハードウエアの共用性を高め、デジタル信号処理の負担を小さくする。

【解決手段】周波数変換ブロック102は、BG内の無線信号を入力して周波数変換し、アナログ複素ベースバンド信号をバンド毎に分離して並列に出力する。スイッチ回路103は、周波数変換ブロック102から並列に出力されるバンド単位のアナログ複素ベースバンド信号のいずれかをADC104に選択的に供給する。分配回路105は、ADC104によって生成されるデジタル信号を時分割し、時分割されたデータブロックを複数の出力信号線群に分離出力可能である。制御回路106は、BG内のバンド間をホッピングする第1の通信モードと、ホッピング無しでBG内の複数バンドを同時使用する第2の通信モードとの切り替えに応じて、スイッチ回路103による信号選択の切替タイミングと、分配回路105による時分割の実行を変更する。

(もっと読む)

周波数変換回路及び受信装置

【課題】回路規模を削減し、消費電流を低減した周波数変換回路、受信装置及び送信装置を提供すること。

【解決手段】入力信号S1の周波数f1と所与の周波数f0を混合し直交出力(位相差90度ずつで4相出力)する周波数変換回路であって、所与の周波数f0で発振し、直交出力する発振部10と、入力信号に基づいて定まる電流値で発振部10を駆動する電流源部20とを含み、発振部10は、入力信号の周波数f1と所与の周波数f0とを混合し直交出力する。

(もっと読む)

信号処理装置及び信号処理方法

【課題】変調信号の復調を実行する際の消費電力を低減し、かつ実装コストを抑制することが可能であり、また入力される信号から精度良く変調成分を抽出することを可能とする信号処理装置及び信号処理方法を提供する。

【解決手段】PLL451は、ベースバンド周波数の信号であるI信号及びQ信号のそれぞれの位相差を算出し、合成することで合成位相差信号を生成する。また、合成位相差信号に基づいて、復調信号を生成する。AFC46は、復調信号に基づいて生成されるAFC用信号に基づいて、DDC421で周波数変換する際に用いた乗算信号の乗算周波数が適切なものか否かを判断し、AFC信号を生成する。そして、乗算周波数を設定するための信号であるAFC信号をDDC421に出力する。

(もっと読む)

チューナー

【課題】無線受信機のチューナーのIQミキサにおいて、回路構成のばらつきなどにより、イメージ妨害信号が十分に除去されない。

【解決手段】受信されたRF信号SRFはIQミキサのIチャネルとQチャネルとに入力される。加算器64はIチャネル、Qチャネルそれぞれから出力される信号SI2,SQ2を合成してイメージ信号を相殺し、目的受信局の信号を取り出す。一方、加算器66はSI2,SQ2から目的受信局の信号を除去しイメージ信号を抽出する。イメージ信号検出回路50が、加算器66の出力に基づいてイメージ混信の発生を検知すると制御部は第1局部発振周波数fLO1をずらす。これにより、目的受信局の信号と干渉源の信号とが周波数軸上で分離され、BPF38a,38bで干渉源の信号を選択的に除去することが可能となる。

(もっと読む)

受信装置

【課題】妨害波による高周波信号の受信特性劣化を改善する受信装置を提供する。

【解決手段】受信した高周波信号から所定の周波数帯域の信号を抽出するバンドパスフィルタ5と、バンドパスフィルタ5で抽出された信号と電圧制御発信器8からの出力とを混合することで該信号を周波数変換する混合器7を少なくとも有し、該周波数変換後の信号を出力するMOPLL回路6と、バンドパスフィルタ5と混合器7とを接続する信号線と、グランド11との間であって、バンドパスフィルタ5からの信号が入力される混合器7の入力トランジスタのバイアス電圧をダイナミックレンジの中心値に設定するための抵抗値を有する抵抗素子R1とを備える。

(もっと読む)

ディジタル制御発振回路、周波数シンセサイザ及び無線通信機器

【課題】ディジタル発振回路自体の位相ノイズを増大させることなく、発振周波数が高く且つ最小周波数変化量が小さい周波数シンセサイザを実現できるようにする。

【解決手段】周波数シンセサイザは、ディジタル制御発振回路11と、発振周波数制御部12とを備えている。ディジタル制御発振回路11は、2本の導体が互いに間隔をおいて並行に配置された並行部15Aと、2本の導体が電気的に絶縁されて交差する交差部15Bとをそれぞれ奇数個有するループ状の伝送線路15と、アクティブ回路17と、第1の可変容量部21及び第2の可変容量部22とを有している。発振周波数制御部12は、第1の可変容量部21に含まれる第1の可変容量素子の高容量状態と低容量状態とを切り替える第1の制御信号をΣΔ変調するΣΔ変調回路40を有している。

(もっと読む)

DCオフセット除去回路および受信機

【課題】アナログ信号の処理回路に適用でき、回路規模が小さく高精度にDCオフセット成分を除去できるDCオフセット除去回路を実現する。

【解決手段】本発明のDCオフセット除去回路100は、信号処理回路110の出力信号Zを量子化するための量子器1と、量子器1の出力信号ZQを増幅または減衰させるゲイン段2と、ゲイン段2の出力信号ZIを積分するデジタル積分器3と、デジタル積分器3の出力信号ZOをシェーピングするノイズシェーピング回路4と、ノイズシェーピング回路4の出力信号をアナログ信号に変換するDA変換器5と、DA変換器5の出力信号をローパスフィルタ6を介して入力信号Xにフィードバックする減算器7とを備える。

(もっと読む)

21 - 40 / 196

[ Back to top ]