Fターム[5K029AA03]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | 誤動作防止;誤り率の低減 (907) | 波形劣化、符号間干渉対策 (407)

Fターム[5K029AA03]の下位に属するFターム

直流変動、バイアス歪対策 (38)

Fターム[5K029AA03]に分類される特許

61 - 80 / 369

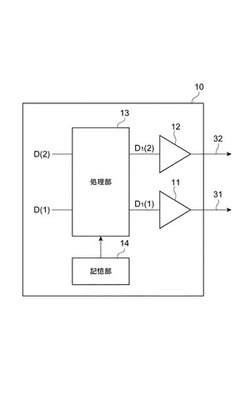

送信装置および送受信システム

【課題】受信装置において受信エラーが生じる頻度を更に低減することができる送信装置および送受信システムを提供する。

【解決手段】送信装置10は、第1出力部11、第2出力部12、処理部13および記憶部14を備える。処理部13は、送出すべき第1データD(1)および第2データD(2)を受け取るとともに、記憶部14により記憶されている信号線路31,32の線路間干渉特性をも受け取る。処理部13は、信号線路31,32の線路間干渉特性に基づいて、第1データD(1)の値を補正したデータD1(2)を求めるとともに、第2データD(2)の値を補正したデータD1(1)を求める。第1出力部11は、処理部13により求められたデータD1(1)を第1信号線路31へ送出する。第2出力部12は、処理部13により求められたデータD1(2)を第2信号線路32へ送出する。

(もっと読む)

プログラマブルロジックデバイス用のデジタル適応回路網および方法

【課題】プログラマブルロジックデバイス用のデジタル適応回路網および方法を提供すること。

【解決手段】本発明は、着信データ信号の等化を制御する方法を提供する。該方法は、該データ信号の中の2つの連続する異なる値を有するビットを検出することと、該2つのビット間の該着信データ信号における遷移が、比較的遅いか、あるいは比較的早いかを決定することと、該遷移が、比較的遅い場合、該着信データ信号の該等化を増加させることとを包含する。

(もっと読む)

伝送システムおよび伝送方法

【課題】差動信号のスキューを精度よく補償すること。

【解決手段】伝送システムは、第1差動信号を伝送路により伝送する送信機と受信機を含む。生成回路は、第1差動信号よりボーレートが低い第2差動信号を生成する。スイッチは、生成回路によって生成された第2差動信号と第1差動信号とを切り替えて伝送路へ出力する。スキュー検出回路は、送信機から伝送路により送信された第2差動信号のスキューを検出する。スキュー補正回路は、スキュー検出回路によって検出されたスキューに基づいて、送信機から伝送路により送信された第1差動信号のスキューを補正する。

(もっと読む)

プリント配線基板及びプリント配線方法

【課題】送信側LSIから受信側LSIに高速信号を伝送するプリント配線の配線パターンを形成する際に、プリント配線に設けられたスルーホールやパッド、コネクタ等による容量性反射の影響を低減し、波形歪みの低減や伝送性能の向上を図ることができるようにする。

【解決手段】送信側LSIチップ21から受信側LSIチップ22に信号を伝送する伝送路をプリント配線13a、13bで形成する際に、そのインピーダンスを一定に保ちつつ、送信側LSIチップ21の近傍の線幅が太く、受信側LSIチップ22の近傍の線幅が細くなるようにプリント配線13a、13bの配線パターンを形成している。これにより、プリント配線13a、13bに設けられたスルーホール14a、14bによる容量性反射の影響を低減させ、波形歪みの低減や伝送性能の向上を図ることができる。

(もっと読む)

送信機および通信システム

【課題】周波数の変化に対応でき、且つクロストークに起因するジッターの低減を図ることができる送信機、および通信システムを提供する。

【解決手段】送信機2は、発振回路4と、送信部5とを備える。発振回路4は、基準クロックCKrefを入力して、同一の周期を有すると共に位相が互いに異なるN相(Nは2以上の整数)のクロックCK1〜CKNを生成して出力する。送信部5は、発振回路4から出力されたクロックCK1〜CKNを入力して、このクロックCKn(nは1以上N以下の各整数)にシリアルデータ信号Snを同期させて高速シリアル伝送線路Lnを介して受信機3に送信する。

(もっと読む)

TMDS信号用差動スキュー効果の発生方法及び装置

【課題】差動のTMDS信号に、差動レーン上の信号間にスキューが生じたのと同様な差動スキュー効果を与える。

【解決手段】ユーザ定義のTMDSデータ・パターン又は入力ビット・ストリーム波形をアップサンプリングする(10)。FIRスキュー・フィルタを形成する(12)。フィルタの係数配列を初期化する(14)。アップサンプリングしたデータをフィルタ係数配列により畳み込んで(28)、差動スキュー効果を発生する。

(もっと読む)

組み合わせデータマスクおよびデータバス反転を用いたデータ符号化

【課題】 SSOノイズの低減を図ることができる符号化方式を提供することである。

【解決手段】 一回路から別の回路へデータを送信するためのデータ符号化方式は、DBI符号化および非DBI符号化を組み合わせ、かつ用いられる符号化のタイプを示すためにデータマスク信号を用いる。第1の状態におけるデータマスク信号は、一回路から前記別の回路に送信されたデータを無視すべきことを示し、第2の状態におけるデータマスク信号は、一回路から前記別の回路に送信されたデータを無視すべきでないことを示す。データマスク信号が第2の状態である場合に、データの第1のサブセットが、データバス反転を用いて符号化され、データの第2のサブセットが、データバス反転とは異なって符号化される。かかる符号化は、符号化データが一回路から別の回路に送信される場合に、SSOノイズが劇的に低減されるという利点を有する。

(もっと読む)

情報伝送システム、情報伝送装置及びプログラム

【課題】伝送路での損失により伝送路を伝送される信号波形が変化する場合でも伝送速度を低下させずに通信を確立できる情報伝送システム、情報伝送装置及びプログラムを提供する。

【解決手段】第1情報伝送装置は、通信の確立を行う際に、連続する複数ビットずつ当該複数ビットの値を同じとした予め定められた第1情報をシリアルに伝送路に送信し、第2情報伝送装置は、伝送路を介して第1情報が受信された場合に当該第1情報に基づいて通信を確立する。

(もっと読む)

アダプタ装置および伝送路評価システム

【課題】パッド付の伝送路の伝送特性についての評価装置による評価を可能にする、評価装置に接続されるアダプタ装置およびこれを備える伝送路評価システムを実現する。

【解決手段】試験信号が入力された評価対象伝送路2から出力される出力信号に基づき評価対象伝送路2の伝送特性を評価する評価装置3に接続されるアダプタ装置1は、評価対象伝送路2の入力端へ入力される試験信号と同じ信号が入力される入力端を有する基準伝送路11と、評価対象伝送路2の出力端から出力される出力信号から、基準伝送路11の入力端に生じた試験信号の反射成分と評価対象伝送路の入力端に生じた試験信号の反射成分との差を増幅した反射成分増幅信号と、基準伝送路11における試験信号の通過損失分と評価対象伝送路2における試験信号の通過損失分との差を増幅した通過損失分増幅信号と、を減算して生成される信号を評価装置3への評価信号とする生成手段12と、を備える。

(もっと読む)

イコライザ調整方法及びアダプティブイコライザ

【課題】被調整信号のEyeが開いていない場合であっても、イコライザ強度を誤って下げることなく自動調節を行う

【解決手段】本発明にかかるアダプティブイコライザは、イコライザ101と、サンプラ102と、符号比較器103と、Eye開閉判定器106とを備える。Eye開閉判定器106は、入力信号波形が開口部を有するか否かを判定する。符号比較器103は、開口部を有するか否かの判定と、サンプラ102によりサンプリングされたサンプリングデータの符号値からイコライザ101の特性の調整を行う。

(もっと読む)

信号伝送装置

【課題】送信端の出力におけるバイアス低下を防ぐ。

【解決手段】入力信号を正相入力端子1、逆相入力端子2で共通に入力し、互いに同相の出力信号を伝送路に出力する第1および第2の送信部と、第1および第2の送信部の出力端間を接続する容量素子14、15と、伝送路とインピーダンスマッチングすると共に、第2の送信部の直流負荷として接続される抵抗素子12、13と、を備え、第1の送信部は、伝送路を介した受信側の入力段の入力抵抗21、22を直流負荷として接続する。ここで、第1の送信部は、差動対となるNMOSトランジスタ8、9、およびこの差動対に電流を供給する定電流源6から構成され、第2の送信部は、差動対となるNMOSトランジスタ10、11、およびこの差動対に電流を供給する定電流源7から構成される。

(もっと読む)

集積回路装置及びデータ伝送システム

【課題】伝送路間のクロストークによる信号伝播遅延を改善する。

【解決手段】集積回路装置3は、並走する伝送路の各々について外部とのインターフェース接続のためのI/Oセル401〜409を有する。集積回路装置3は、I/Oセルの各々へ入力されるデータ信号DQ0〜DQ7の間の位相関係を検出し、その検出された位相関係に基づく制御信号を生成する制御信号生成部301〜304、701〜704と、制御信号生成部で生成される制御信号に応答して、I/Oセルのスイッチング駆動を制御するスイッチング駆動制御部とを有する。

(もっと読む)

半導体LSIおよび半導体装置

【課題】データレート可変な半導体装置及び信号伝送系においても、配線長共振起因のノイズやジッタを小さくする技術を提供する。

【解決手段】プリント回路基板3上に搭載されたメモリ1とメモリコントローラ2との間で信号配線4−1〜3を通じて信号伝送を行う信号伝送システムにおいて、メモリ1とメモリコントローラ2に、特定のデータレートで配線長共振によるノイズやジッタ増加が起こる場合において、このデータレートの情報を保持するレジスタ6−1、6−2を有する。すなわち、配線長共振が起こるデータレートを保存するレジスタ6−1、6−2とクロック周波数と配線長の関係を変更するような制御系を信号伝送システムに持たせ、共振回避できるようにデータレートまたは伝播遅延時間をコントロールする。

(もっと読む)

3元アルファベットに基づく送信シンボルを検出するための方法及び対応する受信機

3元アルファベットに基づく通信チャネルの検出方法を提供する。当該チャネルは、1つの送信時間間隔(TTI)内でN個の連続するスロットにわたって同一のシンボルを運ぶ信号を伝送する。本方法は、シンボル寄与を除去し、かつ、雑音寄与を分離するために、受信されたシンボル(k)を、受信されたシンボル(k+1)から減算するステップ(21)と、雑音の分散vを推定するステップ(22)と、ある程度の残留雑音が加わった、送信された信号の寄与を分離するために、同一のTTIに含まれる、受信された連続する全ての信号の総和を求めるステップ(23)と、送信された信号が0であった場合は中心分布であり、送信された信号が+1または−1であった場合は非心分布である、カイ二乗分布値を得るために、当該変数を2乗するステップ(24)と、上記の分散に比例する閾値を決定するステップ(25)と、上記の閾値を使用して、通信チャネルの検出を実行するステップ(26)とを含む。  (もっと読む)

(もっと読む)

プリエンファシス機能を含む出力回路

【課題】プリエンファシス時とデエンファシス時の差動出力信号のコモンモード電圧の変化を抑え、高速コモンモード電圧変動に対応可能な出力回路の提供。

【解決手段】第1の電流源で駆動され、入力信号を差動入力し、出力対が差動出力端子に接続された第1の差動トランジスタ対と、第2の電流源で駆動され、第1の制御信号を差動入力し、出力対が前記差動出力端子に接続された第2の差動トランジスタ対とを備え、差動出力端子と電源間に負荷抵抗素子対が接続されている。さらに、第3の電流源で駆動され、第2の制御信号を差動入力し、出力対が前記差動出力端子の一方の出力端子と前記電源とに接続された第3の差動トランジスタ対と、第4の電流源で駆動され、第3の制御信号を差動入力し、出力対が前記電源と前記差動出力端子の他方の出力端子とに接続された第4の差動トランジスタ対とを備えている。

(もっと読む)

光受信装置

【課題】 簡易な構成で正相信号と逆相信号との間のスキューを抑制することができる光受信装置を提供する。

【解決手段】 光受信装置は、変調信号に対して遅延干渉させる遅延干渉計と、遅延干渉計から出力される相補光を電気信号に変換する受光器と、受光器が生成する電気信号から所定の周波数成分を抽出するフィルタと、相補光の光パス、または、受光器の光電変換素子から相補信号の電気信号を合成するまでのパス、に挿入された少なくとも1つのスキュー調整手段と、フィルタからの出力に基づいて相補信号の正相と逆相との時間差が減少するようにスキュー調整手段を制御する制御手段と、を備える。

(もっと読む)

信号処理装置、信号処理方法、及び信号処理プログラム

【課題】所定信号のアイダイアグラムにおけるアイ開口を高精度に最適化すること。

【解決手段】信号処理装置は、入力信号の所定帯域を増幅して出力信号を出力するイコライザー手段と、イコライザー手段により増幅された出力信号を、多相クロック方式で、かつ振幅方向へオフセットさせつつサンプリングを行うサンプラー手段と、サンプラー手段によりサンプリングされた出力信号に基づいて、出力信号のアイダイアグラムにおけるアイ開口の面積情報を算出する面積情報算出手段と、面積情報算出手段により算出されたアイ開口の面積情報に基づいて、イコライザー手段の増幅を制御する制御手段と、を備えている。

(もっと読む)

繰り返し干渉キャンセル受信機

ワイヤレス通信における干渉を抑制する方法は、シンボルのバーストを受信すること、第1の複数のウェイトを有する干渉抑制フィルタを使って、シンボルのバーストをフィルタリングすること、フィルタリングされたシンボルのバーストを復号して、シンボルのバーストに対応するデータを生成すること、データを符号化して、再符号化シンボルのバーストを生成すること、再符号化シンボルのバーストに基づいて、干渉抑制フィルタについて第2の複数のウェイトを算出すること、第2の複数のウェイトを有する干渉抑制フィルタを使って、再符号化シンボルのバーストをフィルタリングすること、およびフィルタリングされた再符号化シンボルのバーストを復号することを備える。

(もっと読む)

信号等化器

【課題】インピーダンス不整合によって発生する反射を抑制して伝送特性の劣化を防止することで、広い周波数帯域で使用可能な信号等化器を得る。

【解決手段】送信端1と受信端2との間を接続して信号を伝送する主伝送線路20と、主伝送線路20の受信端2側に、受信端2と並列に接続された受信側終端抵抗50と、受信側終端抵抗50と並列に接続され、伝送線路61および伝送線路61とインピーダンスが異なる終端抵抗62の直列回路からなり、所望の周波数帯域以外の帯域の信号を減衰させる周波数特性調整回路60と、主伝送線路20と受信端2との間に直列に接続され、自身の入力インピーダンスと主伝送線路20の特性インピーダンスとを整合させる整合抵抗30とを備える。

(もっと読む)

信号処理装置、タイミング同期回路、信号処理方法、及びタイミング同期方法

【課題】遅延を用いずにデータ信号とクロックとを同期させるタイミング同期回路を提供すること。

【解決手段】入力信号を立ち上がり又は立ち下がりタイミングでトグルするトグル回路と、クロックと前記トグル回路の出力信号とが入力され、当該トグル回路の出力信号を前記クロックの立ち上がり又は立ち下がりタイミングに同期させる第1同期回路と、前記トグル回路の出力信号と前記第1同期回路の出力信号とが入力され、入力された両出力信号の排他的論理和を出力する排他的論理和回路と、前記クロックと前記排他的論理和回路の出力信号とが入力され、当該出力信号を前記クロックの立ち下がり又は立ち上がりタイミングに同期させる第2同期回路と、を備える、タイミング同期回路が提供される。

(もっと読む)

61 - 80 / 369

[ Back to top ]