Fターム[5K029AA03]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | 誤動作防止;誤り率の低減 (907) | 波形劣化、符号間干渉対策 (407)

Fターム[5K029AA03]の下位に属するFターム

直流変動、バイアス歪対策 (38)

Fターム[5K029AA03]に分類される特許

101 - 120 / 369

情報処理装置および方法、並びにプログラム

【課題】通信の信頼性を保ちつつ応答性を向上させる。

【解決手段】増幅部51乃至復調部53は、符号化プリアンブルと符号化データを含む符号化フレームが送信元から送信されてきた場合、符号化フレームをアナログ信号として受信する。サンプリング部61は、符号化フレームを、ビット区間を単位として、1単位につき2以上のサンプリング数でサンプリングする。ビット判別部62は、1単位分のサンプリングの結果に基づいて、ビット区間の符号化前のビットを判別する。ビットサンプリング数変更部81は、符号化プリアンブルに対するサンプリングの結果に基づいて、符号化データに対するサンプリングを行う場合のビットサンプリング数を変更する制御を行う。本発明は、例えば、パッシブエントリシステムに適用できる。

(もっと読む)

通信装置、および信号処理方法

【課題】受信情報の解析を正確に行うことを可能とする通信装置を実現する。

【解決手段】無線通信による受信信号から受信情報の検出処理を実行する構成において、検波部がキャリア信号に重畳された受信情報を入力して受信情報を含む検波信号を生成し、パーシャルレスポンス等化処理部が、前記検波信号に対するパーシャルレスポンス等化処理による信号処理を実行し、パーシャルレスポンス等化処理部において補正された信号を例えばビタビデコーダによって構成される検出部に入力して受信情報を取得する。本構成により、通信路において発生する歪みがパーシャルレスポンス等化処理部において補正され、補正信号から受信情報の取得を行う構成としたので例えば伝送レートの高い通信などにおいても正確な情報伝送が可能となる。

(もっと読む)

畳み込み逐次型適応等化器

畳み込み適応等化器を提供する。この等化器は、等化器コアと自動ゲイン制御ループとを有している。等化器コアの等化伝達関数は、自動ゲイン制御ループにより生成される1つ以上のゲイン制御信号と、自動ゲイン制御ループにより生成される畳み込み信号とにより調整される。畳み込み信号が非アクティブであるときには、ゲイン制御信号が増加すると、等化器コアの伝達関数の高周波数・高帯域幅ゲインが増加する。畳み込み信号がアクティブであるときには、ゲイン制御信号を減少させることによって、更なるゲインを適用することが可能であり、このとき、等化器コアの伝達関数において、より低帯域幅に向かって周波数シフトが生じ、また、等化器コアの伝達関数の高周波数・低帯域幅ゲインにおいて増加が生じる。 (もっと読む)

波形等化量調整方法、波形等化量調整回路、半導体装置および情報ネットワーク装置

【課題】従来の波形等化量調整方式ではトレーニングデータを必要とするため、たとえば回路特性の経時変化などにより波形等化量の最適値が変化した場合には、一旦、装置をトレーニング動作に切り替えて波形等化量を再調整する必要があるため、装置の通常動作を停止させる必要があった。

【解決手段】レシーバで受信したデータにおいて、CDRで再生されたクロックで取得したデータと、CDRで再生されたクロックとは位相の異なるクロックで取得したデータとを用いて波形等化量を調整することにより、装置を通常動作させた状態で波形等化量を最適化できる波形等化量調整方式を提供する。

(もっと読む)

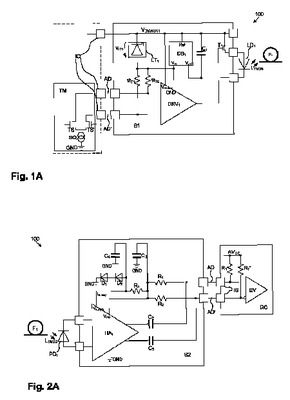

TMDS符号化信号を伝送する回路装置及び方法

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

高速シリアルインターフェイス受信器回路における自動較正

シリアルデータ信号(例えば、高速シリアルデータ信号)を受け取る回路が、シリアルデータ信号のイコライゼーションされたバージョンを発生させる調節可能なイコライザ回路を含む。イコライザ回路は制御可能に可変なDC利得および制御可能に可変なAC利得を含み得る。回路はイコライゼーションされたバージョンのアイの高さ、幅を示す第一出力信号、第二出力信号をそれぞれ発生させるアイ高さモニター回路、アイ幅モニター回路をさらに含み得る。第一出力信号はイコライザ回路のDC利得の制御において用いられ得る。第二出力信号はイコライザ回路のAC利得の制御において用いられ得る。  (もっと読む)

(もっと読む)

ハードリミットされた信号についてのチャネル推定および等化

本発明は、受信信号の振幅がハードリミットされる場合のチャネル推定のための方法および装置を提供する。チャネル推定部は、受信信号の位相サンプルおよび前回のチャネル推定値に基づいて、受信信号についての振幅推定値を算出する。振幅推定値は、位相サンプルおよび初期のチャネル推定値を所与とする振幅の期待値を含み得る。その後、チャネル推定部は、振幅推定値および位相サンプルに基づいて、修正されたチャネル推定値を算出する。プロセスは、各反復の間にチャネル推定値を精緻化するために繰り返し実行され得る。 (もっと読む)

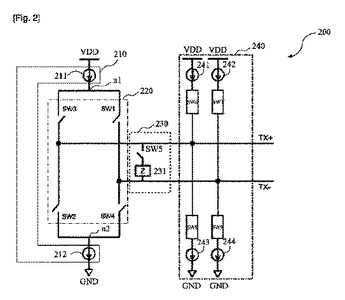

ドライバ回路

【課題】高速なデータパターンの時のみ周波数特性を改善して、所望の振幅を得ることが可能な送信側ドライバ回路を提供する。

【解決手段】第1のプルアップ抵抗回路P41、第3のプルアップ抵抗回路P43、第1のプルダウン抵抗回路N41、第3のプルダウン抵抗回路N43の抵抗値を第1の制御信号(SDATAP、SDATAM、DEMPHPP、DEMPHMN、DEMPHPN、DEMPHMP)に応じて変化させ、第2のプルアップ抵抗回路P42、第4のプルアップ抵抗回路P44、第2のプルダウン抵抗回路N42、第4のプルダウン抵抗回路N44の抵抗値を第2の制御信号(EMPHPP、EMPHPMN、EMPHPN、EMPHMP)に応じて変化させる

(もっと読む)

通信システム及び歪み抑制回路の設計方法

【課題】主伝送線の同一点に複数の通信ノードが接続され、その接続部に歪み抑制回路が設けられた通信システムにおいて、通信システムのばらつきに影響されることなく正常に機能するよう、歪み抑制回路の回路パラメータを簡単に設定できるようにする。

【解決手段】主伝送路2にハブ4を介して複数の通信ノード10が接続された通信システムにおいて、ハブ4内でのインピーダンスの不整合により通信信号が歪むのを防止するために、ハブ4内の主伝送路2上(もしくは主伝送路2を構成する通信線間)にコイル等からなる歪み抑制回路8を設ける。そして、この歪み抑制回路8の回路パラメータは、通信システムの配索制約内で通信状態が最も悪い最悪配索を算出し、その算出した最悪配索にて、所定の整合条件(例えば、反射係数0.33以下、VSWR≦2.0)となるよう、コンピュータによる演算処理にて設定する。

(もっと読む)

出力回路

【課題】複雑な遅延回路を用いずにプリエンファシスの信号を生成し、また、プリエンファシスの強度を変化させても、出力のコモンモードレベルが変化しない出力回路を提供する。

【解決手段】信号入力に比例した出力電流を生成する相互コンダクタンス回路と、前記信号入力からプリエンファシス電流を生成するプリエンファシス電流出力回路と、プリエンファシス電流出力回路の出力のAC電流成分を、調整電圧入力に基づく所定の係数で増幅するプリエンファシス電流調整回路と、前記相互コンダクタンス回路の出力電流と前記プリエンファシス電流調整回路の出力電流とが流れ、出力を生成する負荷回路とを備える。

(もっと読む)

差動電流駆動方式の送信部、差動電流駆動方式の受信部及び前記送信部と前記受信部を具備する差動電流駆動方式のインターフェースシステム

本発明は、伝送ラインに流れる電流の方向を調節することでデータを受信部に送信する差動電流駆動方式の送信部、差動電流駆動方式の送信部及び前記差動電流駆動方式の送信部と差動電流駆動方式の送信部を具備する差動電流駆動方式のインターフェースシステムに対して開示する。前記差動電流駆動方式の送信部は、電流源、電流方向選択ブロック及び平衡スイッチブロックを具備する。前記電流源は伝送ライン対に電流を供給するか、または前記伝送ライン対から流れる電流をシンクする。前記電流方向選択ブロックは、前記伝送ライン対のうちで一つの伝送ラインに前記電流源から流れる電流を伝達して、残り一つの伝送ラインに流れる電流を前記電流源に伝達する。平衡スイッチブロックは前記伝送ライン対を平衡状態に初期化する。  (もっと読む)

(もっと読む)

信号伝送システム

【課題】伝送路3を介して信号を伝送する信号伝送システムにおいて、ランダムパターンを発生する回路や伝送路3を介して伝送された後の信号のEYE波形の取得を不要として回路規模の増大を抑制する。

【解決手段】信号伝送システムは、伝送路3を介して伝送される前の信号にプリエンファシスを与えるプリエンファシス回路14と、伝送路3を介して伝送された後の信号の波形において敷居電圧レベルを超えている受信側時間を計測する受信側時間計測部32と、受信側時間計測部32が計測した受信側時間と伝送路3を介して伝送される前の信号において敷居電圧レベルを超えている送信側時間の期待値とを比較する比較判定部22と、比較判定部22による比較の結果に基づいてプリエンファシス回路14を制御してプリエンファシスを調整するプリエンファシス制御部21とを備える。

(もっと読む)

コネクタ構造及び信号伝送装置

【課題】付加的な部品を用いることなく、差動信号の伝送における波形劣化を改善することができるコネクタ構造を提供する。

【解決手段】コネクタ30にフラットケーブル20の接続部20aを挿入して接続し、送信デバイス14からプリント配線基板10上の差動伝送線路15A,15Aに差動信号を入力すると、差動信号は差動伝送線路15A,15Aを伝送し、差動伝送線路15A,22A間の電磁結合若しくは静電結合又はそれらの両方により、フラットケーブル20の差動伝送線路22,22に伝達し、受信デバイス2に受信される。

(もっと読む)

データ受信装置

【課題】シリアルデータの各データにデータ幅の不均等や位相差があっても、サンプリングミスを防止することのできるデータ受信装置を提供する。

【解決手段】データ受信装置1は、多相クロック生成部11が、入力されたクロック信号CKから相互の位相差がT/7である7個のクロックC1〜C7を生成し、位相調整部21、22、23が、位相制御信号A、B、Cによる設定に応じてクロックC1〜C7の個々のクロックの位相を調整して、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7として出力し、シリアルパラレル変換部31、32、33が、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7により、入力されたシリアルデータA、B、Cをそれぞれサンプリングし、7ビットのパラレルデータA、B、Cに変換する。

(もっと読む)

デジタル無線の受信装置

【課題】 ダイナミックレンジ性能に優れた無線通信システムを提供する。

【解決手段】デジタル無線の受信装置のべ一スバンドフィルタ出力の利得制御を行う。このための利得制御手段に、電力演算手段と、平均化手段と、利得演算手段と、比較手段と、乗算手段とを備える。電力演算手段は、ベースバンドフィルタ出力値の瞬時電力を演算する。平均化手段は、電力演算手段の出力値を平均化する。利得演算手段は、平均化手段の出力値と出力ターゲットレベルにより利得制御量を演算する。比較手段は、演算手段の出力値と所定の閾値を比較して閾値以下/より小さい場合に出力する。最小値保持手段は、比較手段の出力値の最小値を保持する。そして、乗算手段は、最小値保持手段の出力値とベースバンドフィルタ出力を乗算する。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】プリエンファシス機能を有し、ジッタを低減する出力バッファ回路の提供。

【解決手段】第1の論理信号を入力して伝送線路(L)を駆動する第1のバッファ回路(M1)と、第1の論理信号に対して所定の論理関係にある第2の論理信号を入力し、出力が第1のバッファ回路の出力と共通接続された反転バッファ(T4,T5)と、反転バッファと第1の電源(VDD)間に接続され、制御端子に入力される信号に基づき、オン・オフ制御される第1のスイッチ(T3)と、反転バッファと第2の電源(VSS)間に接続され、制御端子に入力される信号に基づき、第1のスイッチと連動してオン・オフ制御される第2のスイッチ(T6)と、を備えたプリエンファシス制御用の第2のバッファ回路(M2)を備える。

(もっと読む)

シリアルデータの劣化検出回路を有する制御回路

【課題】受信した光信号に異常が発生する前に光信号の劣化を検出する。

【解決手段】シリアル通信機能を備えた制御機器において、シリアル通信機能により受信したシリアルデータの立上りあるいは立下りエッジの位相を検出し、シリアルデータの立上りあるいは立下りエッジの位相と基準クロックの位相との間の位相差を位相データとして出力する位相検出回路12と、位相検出回路12から出力される位相データが予め設定された範囲を超えたか否かを判定し、位相データが予め設定された範囲を超えたと判定したときワーニングを出力する位相判定回路13と、を備える。

(もっと読む)

ディジタルインターフェースを有する半導体装置

【課題】本発明の課題は、インターフェースのレシーバにて、データパターンに依存するジッタを低減することにある。そして、低減するための遅延量の設定を装置毎に調整できるように自動的に調整可能なLSIを提供することにある。

【解決手段】データパターン依存ジッタは、前の状態がどの様であったかで予測可能であるので、レシーバにて受け取ったデータの状態を保持しこの保持された状態と、入力されたデータとから入力データの取り込みタイミングを調整する。

また、実装形態に依存する遅延量を決定するためのレシーバ内の調整機構として、ドライバから1サイクル間隔のパルスデータ、2サイクル間隔のパルスデータをテストパターンとして送受信する。パルス幅の異なるパルスの立上りと立下がり時間差から系に最適な遅延量を求める自動調整機構を持つ。

(もっと読む)

波形等化器および受信器ならびに光伝送システム

【課題】使用する変調方式を切替えても波形等化における重み付け量を最適値に設定できるようにする。

【解決手段】光信号の波形等化を行う波形等化器13において、波形等化の最適化のために波形等化器13の内部回路(乗算回路24−1、24−2、24−3)に設定する重み付け量を、受信する光信号の変調方式によって変化させている。変調方式によって変化するものとしては、光信号のデューティ比や光信号のスペクトル幅などがあり、これらに応じて重み付け量を変化させるようにしてもよい。

(もっと読む)

周波数応答バス符号化

データシステム(102)はバスの周波数に基づいてバスの符号化を可能にする。符号化手法は、システムパフォーマンスの低下につながる場合がある共振状態等、好ましくない周波数状態を回避するために実装可能である。装置または集積回路は、通常、符号器を備える。一実施形態では、符号器は、データバスの全てのラインを選択的に反転するデータバス変転(DBI)回路である。検出器は帯域通過フィルタまたはストップバンドフィルタを備え、これらは、例えば、バス上の伝送対象のデータを評価し、予め決定された周波数または周波数帯域等の周波数を検出する。検出器は、周波数の関数として符号化手法を選択的に適用するために符号器に制御信号を提供する。 (もっと読む)

101 - 120 / 369

[ Back to top ]