Fターム[5K029AA03]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | 誤動作防止;誤り率の低減 (907) | 波形劣化、符号間干渉対策 (407)

Fターム[5K029AA03]の下位に属するFターム

直流変動、バイアス歪対策 (38)

Fターム[5K029AA03]に分類される特許

21 - 40 / 369

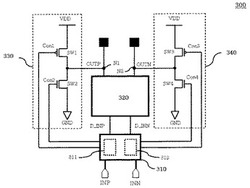

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

判定帰還型自動等化器評価装置および判定帰還型自動等化器評価方法

【課題】従来の判定帰還型自動等化器(DFE)の評価装置では、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することはできなかった。

【解決手段】

既知のデジタル入力信号を受けてDFEから出力されるデジタル信号をDFEの各タップに対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

サンプリングされた前記デジタル信号から各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備える。

(もっと読む)

パルスパターン発生装置及び該装置を用いた誤り率測定システム並びにパルスパターン発生方法

【課題】発生できるパルスパターンの種類を増やす。

【解決手段】差動クロック発生部4は、所定周期の正相クロックと、正相クロックと位相が反転した反転クロックとを発生する。クロック選択部5は、差動クロック発生部4が発生する正相クロック又は反転クロックの何れかのクロックを選択する。データ保持部3は、クロック選択部5で選択された正相クロック又は反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力する。パルスパターン発生部7は、データ保持部3から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生する。

(もっと読む)

中継装置

【課題】第2通信信号が中継先から中継元の伝送路に帰還されることを防止して、波形を乱すことなく第2通信信号を中継可能な中継装置を提供する。

【解決手段】中継装置1は、第1抽出部111と第2重畳部132との間に挿入された第1スイッチ151と、第2抽出部112と第1重畳部131との間に挿入された第2スイッチ152とを備えている。第1スイッチ151は、第1伝送路21から第2伝送路22へ中継される重畳信号の経路のオンオフを行い、第2スイッチ152は、第2伝送路221から第1伝送路21へ中継される重畳信号の経路のオンオフを行う。第1スイッチ151は、第2伝送路22から第1伝送路21への重畳信号の中継時にオフするように、第1制御信号を受けてオンオフ制御される。第2スイッチ152は、第1伝送路21から第2伝送路22への重畳信号の中継時にオフするように、第2制御信号を受けてオンオフ制御される。

(もっと読む)

プログラム可能な、レシーバの等化回路および方法

【課題】伝送媒体によって起こる減衰を好適に補償する等化回路を提供する。

【解決手段】伝送媒体を介して送信されるデータ信号は、その伝送媒体によって起こる減衰をこうむる。等化回路(106)は、直列に配列される複数のステージ(202)を含み、それによって、ステージ(202)の周波数応答を共に統合することを可能にする。各ステージ(202)は、ゼロを挿入するようにプログラム可能であり得、それによって、ステージ(202)の周波数応答の大きさは、20dB/decade大きくなる。ゼロの周波数位置はまた、プログラム可能であり得、それによって、各ステージ(202)が、特定の周波数に対する特定の量のゲインを与えることを可能にする。各ステージ(202)は、高周波ノイズの低減およびクロストーク消去に対する極の位置を決定するようにプログラム可能でもあり得る。

(もっと読む)

受信回路

【課題】補間誤差を低減することができる受信回路を提供することを課題とする。

【解決手段】受信回路は、入力データ信号をクロック信号に基づいてサンプリングしてサンプリング信号を出力するサンプリング回路(201)と、前記入力データ信号に対する前記サンプリング信号の位相情報に基づいて前記サンプリング信号を補間して補間データ信号を出力するデータ補間回路(202)と、前記サンプリング信号と前記位相情報とに基づいて補間誤差を出力する補間誤差判定回路(203)と、前記補間誤差に基づいて設定される等化係数によって前記補間データ信号を等化し、前記等化された補間データ信号を判定して判定信号を出力する判定等化回路(204)と、前記判定信号又は前記等化された補間データ信号に基づいて前記位相情報を生成し、前記データ補間回路及び前記補間誤差判定回路に前記位相情報を出力する位相検出回路(205)とを有する。

(もっと読む)

PWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができるPWM制御のデューティ決定方法を提供する。

【解決手段】制御IC63が、駆動回路に出力するPWM信号のデューティを、指令値を中心に、所定期間内における平均が前記指令値に一致するように微小変動させる場合、PC68のデータベース69に、実際にPWM信号を駆動回路に与えることで発生したノイズ成分のレベル測定結果を反映したデータを、そのデューティの変動態様と共に記憶する。そして、データベース69に記憶されているデータを参照し、与えられた動作環境や動作条件等に応じて抑圧対象となる周波数帯のノイズレベルを低減するように、制御IC63によるPWMデューティの変動態様を決定する。

(もっと読む)

エンファシス信号生成回路及び信号合成回路

【課題】電力消費の無駄を低減する。

【解決手段】加減算部100は第一信号と第二信号とを所定の比率で加減算するものであり、その比率は可変自在である。振幅調整部300は信号の振幅の調整を行うものである。直流レベル調整部400は、加減算部100に入力される信号の直流成分のレベルを調整する。回路への第一の入力信号は第一信号として加減算部100に入力される。回路への第二の入力信号は、振幅調整部300によって振幅の調整が行われると共に直流レベル調整部400によって直流成分のレベルが調整された上で、第二信号として加減算部100に入力される。

(もっと読む)

信号波形の品質改善方式

【課題】電子計算機およびその周辺機器に接続された通信用ケーブルの長さに応じて、良好な波形品質が確保できるように通信信号の波形を調整する。

【解決手段】通信用ケーブルにケーブルの長さを識別可能なID情報を保存したメモリを内蔵し、電子計算機または周辺機器に搭載された制御用マイコンが通信用ケーブルのID情報を読み出し、読み出したID情報から通信用ケーブルの長さを判別し、通信用LSIを良好な波形品質を得られるように設定する。

(もっと読む)

プリント回路板

【課題】受動部材にてデエンファシス機能を実現することで、伝送線路で減衰する信号の高周波成分を補正し、符号間干渉によるタイミングジッタを低減する。

【解決手段】送信回路131と伝送線路111との接続点101aに、送信回路131の出力インピーダンス値と伝送線路111のインピーダンス値の並列インピーダンス値以上のインピーダンス値の補正線路113の一端が接続される。補正線路113の他端には、補正線路113のインピーダンス値よりも低い抵抗値の補正抵抗器110が接続される。補正線路113の信号伝播時間をTd、信号の最小のパルス幅をTmin、信号の立ち上がり時間をTrとしたとき、信号伝播時間Tdが0.5×Tr≦Td≦0.5×Tminの条件を満たすように、補正線路113の長さが設定されている。

(もっと読む)

受信回路

【課題】ビット幅の広いデジタル演算を必要とせずに、小さい回路面積及び消費電力で適応等化処理を実現できる受信回路を提供する。

【解決手段】受信回路は、等化係数に応じた等化処理を受信信号に施して等化された信号を出力する等化回路と、等化された信号と第1閾値との大小関係に応じた0及び1の信号値を有する第1の信号を求め、等化された信号と第2閾値との大小関係に応じた0及び1の信号値を有する第2の信号を求め、第1の信号中に現れる所定の0及び1のパターンの出現回数と第2の信号中に現れる所定の0及び1のパターンの出現回数との差分を計算する誤差計算回路と、差分に応じて等化係数を調整する適応等化制御回路とを含む。

(もっと読む)

判定帰還型波形等化器

【課題】直前ビットの受信判定データを利用することなく、第1ポストカーソルのISIを補正する判定負帰還型波形等化器を提供する。

【解決手段】判定帰還型波形等化器は、受信データを入力する増幅回路と、フリップフロップを含み、増幅回路の出力がフリップフロップに入力され、フリップフロップにより増幅回路の出力を判定するデュオバイナリ信号判定器と、フリップフロップに保持された判定結果を逐次シフトさせるシフトレジスタと、シフトレジスタの各出力を入力とし、出力を増幅回路の出力に帰還し、その電位を制御する複数の電流制御ブロックとを有し、フリップフロップに保持された判定結果をシフトレジスタでシフトさせることなく増幅回路の出力の出力に帰還しない。

(もっと読む)

ドライバアンプ回路および通信システム

【課題】バイアス調整回路やプリドライバ回路が不要で、しかも出力波形の波形歪みを低減することが可能なドライバアンプ回路および通信システムを提供する。

【解決手段】スイッチングトランジスタM11〜M14を駆動するゲート電圧を均一にするため、スイッチングトランジスタM11〜M14を電源およびGND側に配置し、さらに、スイッチングトランジスタM11〜M14の駆動振幅を安定させるために、各スイッチングトランジスタM11のドレインと出力ノードND11、ND12間にそれぞれ第1から第4の抵抗素子R11〜R14を接続している。

(もっと読む)

信号発生装置及び発生方法

【課題】シリアル・データ・パターンに符号間干渉ISI効果及び帯域幅拡張プリエンファシスBWEPE効果を与える。

【解決手段】CPU60は、表示器36上にユーザ・インタフェースを発生して、シリアル・データ・パターン用のパラメータと、このシリアル・データ・パターンの帯域幅拡張プリエンファシス効果及び符号間干渉効果の少なくとも一方のパラメータとを設定する。CPUは、シリアル・データ・パターン・パラメータ、符号間干渉効果のパラメータ及び帯域幅拡張プリエンファシス効果のパラメータを用いて、波形記録ファイルを作成する。波形発生器70は、波形記録ファイルを受け、符号間干渉効果のパラメータ及び帯域幅拡張プリエンファシス効果のパラメータにより定義された符号間干渉効果及び帯域幅拡張プリエンファシス効果の少なくとも一方を有するシリアル・データ・パターン・アナログ出力信号を発生する。

(もっと読む)

エレベータの信号伝送装置

【課題】直列伝送信号が時間軸に対して歪んだとしても、正しくデータを受信することができるレベータの信号伝送装置を提供する。

【解決手段】直列伝送信号の最初のビット以外の特定のビットが直前のビットと異なるレベルに緩やかに移行する場合に、親局によるサンプリング位置での特定のビットの値が異なるレベルと認識される値となるように、残りのビットの時間幅を維持しつつ、最初のビットの時間幅を狭くして、複数のビットを連続的に並べて親局へ送信するようにした。

(もっと読む)

駆動回路および光送信装置

【課題】駆動対象の応答特性を柔軟に補償すること。

【解決手段】駆動回路100は、分岐部110と、遅延部121,122と、増幅器131,132と、合成部140と、を備えている。分岐部110は、駆動信号を分岐する。遅延部121,122は、遅延量が可変の可変遅延部を含み、分岐部110によって分岐された各駆動信号をそれぞれ遅延させる。増幅器131,132は、各駆動信号のうちの一部の駆動信号を反転させる。合成部140は、遅延部121,122および増幅器131,132の後段に設けられ各駆動信号を合成する。

(もっと読む)

信号送受信手段

【課題】矩形波信号の伝達遅れを補償できる信号送受信手段を提供する。

【解決手段】第1矩形波信号U_H等と第2矩形波信号U_L等を、送信装置4から送信し、伝送路6を伝送させ、受信装置5で受信し、送信装置4と受信装置5では、第1矩形波信号U_H等の立ち上がりのタイミングと、第2矩形波信号U_L等の立ち下がりのタイミングとが同期している送受信システム3に用いられる信号送受信手段9において、伝送路6より送信装置4側で、第1矩形波信号U_H等又は第2矩形波信号U_L等について、立ち上がりと立ち下がりの相互間の反転を行い、伝送路6より受信装置5側で、第1矩形波信号U_H等又は第2矩形波信号U_L等について、その反転を行い、伝送路6では、第1矩形波信号U_H等と第2矩形波信号U_L等の両方の立ち上がりのタイミング、又は、両方の立ち下がりのタイミングが同期している。

(もっと読む)

信号変換装置、波形測定装置および半導体試験装置

【課題】シングルエンド信号および差動信号を入力してシングルエンド信号を出力するときに、広帯域でノイズや歪みが少ない高品質なシングルエンド信号を出力することを目的とする。

【解決手段】信号変換装置3にパルストランス12を用い、シングルエンド信号を入力したときには、パルストランス12の1次入力側と2次入力側とのうちシングルエンド信号を入力した入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続し、差動信号を入力したときには、1次入力側および2次入力側との両方の入力側および1次出力側と2次出力側とのうち何れか一方の出力側をパルストランス12に接続する制御を行っている。

(もっと読む)

データ受信装置および適応等化回路

【課題】回路規模を抑制し、消費電力を低減する。

【解決手段】複数の受信回路2a〜2dは、伝送線路に接続され、伝送線路からデータ信号を受信する。受信回路2a〜2dは、受信したデータ信号の波形を整形するための等化器を具備している。適応等化回路3は、複数の受信回路2a〜2dの全部または2以上の所定数ずつに対して1つ設けられ、対応した受信回路2a〜2dの等化器の、波形整形をするための等化係数を算出し、対応した受信回路2a〜2dに出力する。

(もっと読む)

通信ネットワーク

【課題】簡易な構成でありながら、伝送路あるいは分岐路に接続される電子制御ユニットの間の信号の波形歪みを解消するようにした通信ネットワークを提供する。

【解決手段】ECU14a(第1電子制御ユニット)と、ECU14b(第2電子制御ユニット)と、ECU14a,14bを接続するバス(伝送路)16と、バス16から分岐される分岐路20に接続されてECU14a,14bの少なくともいずれかと通信可能なECU14c(第3電子制御ユニット)とを有すると共に、ECU14a,14bはバス16の特性インピーダンスに応じた終端回路22で終端される通信ネットワーク10において、前記分岐路20に導線(スタブフィルタ)24を一端で接続すると共に、前記導線24の他端を開放する。

(もっと読む)

21 - 40 / 369

[ Back to top ]