国際特許分類[G06F1/04]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875)

国際特許分類[G06F1/04]の下位に属する分類

複数のクロック信号を発生するクロック発生装置 (271)

クロック周波数が可変またはプログラマブルであるクロック発生装置 (148)

クロック信号の分配 (273)

異なるクロック信号の同期 (147)

時間監視装置,例.リアルタイムクロック (141)

国際特許分類[G06F1/04]に分類される特許

11 - 20 / 895

記録装置及び記録装置の制御方法

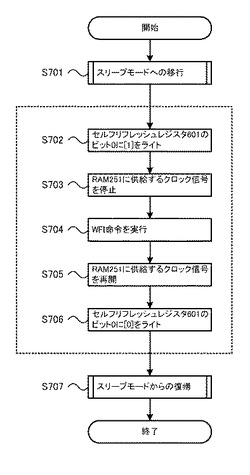

【課題】装置を消費電力の少ないスリープモードに移行する際に、不要電磁雑音の影響を抑制しつつ、不要電磁雑音のピークを低減する効果があるがスペクトル拡散しない場合に比べ消費電力が大きくなるSSCGの消費電力を低減して装置全体を省電力にする。

【解決手段】スリープモードに移行する際にSDRAMをセルフリフレッシュ状態に遷移させた後、SSCGをスペクトル拡散されていないクロック信号を出力するモードに移行させる。

(もっと読む)

調整可能な波高率による帯域制限雑音の生成

【課題】調整可能な波高率による帯域制限雑音の生成の提供。

【解決手段】各々が周波数指数に関連する個々の周波数と、前記周波数指数の指数関数である位相とを有するいくつかの正弦波信号で構成された1以上のサブバンド信号を含む試験信号を供給する試験信号発生器であって、各サブバンド信号について所望の波高率値を受信し、波高率と指数の演繹的な公知の関係に基づいて前記波高率に対応する指数を求め、前記指数関数と前記先に求めた指数とを使用して各正弦波信号について位相値を計算し、前記サブバンド信号に関連した前記正弦波信号を重畳して、前記個々の信号の前記位相が維持されるように前記サブバンド、及び、従って、各サブバンド内に所望の波高率を有する前記試験信号を取得し、その後使用するために前記試験信号を出力するように構成される試験信号発生器。

(もっと読む)

半導体集積回路及びその省電力制御方法、並びに半導体装置

【課題】デバイス間のインタフェースとしてPCI Expressを用いた画像処理装置において、画像読取部からの画像データで、画像データの転送に影響を与えずに、ASPMを利用可能にする。

【解決手段】LTSSMで定義された状態のうち、低消費電力(省電力)状態にいることを示す信号をLTSSMレジスタ602bからアンド回路603a,603bに出力し、SSCG607からのクロックをマスクすることにより、PCIeのリンクの状態に応じて、ASIC601内の所定の機能モジュールへのクロック供給を止めることができる。これにより、ASIC601の消費電力を削減できる。ASPMによる動的なクロックゲーティングが可能となり、ASIC601内のこまめな省電力制御が実現できる。

(もっと読む)

クロック診断回路

【課題】単一のクロックから、クロック周期、及びクロックパルス幅の変動の異常を確実に検出することができるクロック診断回路を提供することを目的とする。

【解決手段】クロックs10を予め設定されるクロックパルス幅以下の所定時間、遅延させる遅延回路2と、遅延回路2から出力された遅延クロックを所定の周期数倍遅延させる整数倍遅延回路3と、クロックを、遅延クロックを用いて符号化する第1の排他的論理和回路4と、第1の排他的論理和回路4の出力を、整数倍遅延回路3の出力を用いて復号化する第2の排他的論理和回路5と、クロックs10と第2の排他的論理和回路5の出力とを比較して、クロックの異常を検出する比較回路6と、を備え、クロックパルス幅、及びクロック周期の変動を、自身の単一のクロックに基づいて検出するようにしたことを特徴とするクロック診断回路1。

(もっと読む)

データ処理装置

【課題】データの送受信処理等を行うデータ処理装置に関し、装置としての信頼性を向上すると共に、省電力化を図る。

【解決手段】クロックに従ってデータ処理を実行する装置であって、クロックの供給停止を制御するクロックゲーティング部20,21を備え、このクロックゲーティング部20,21は、0系と1系とのデータ処理部、例えば、端末対応部10,11対応のクロックの供給停止を制御する構成を備え、0系と1系とのデータ処理部対応に正常性を監視して、異常発生側のクロックゲーティング部を介したクロック供給を停止し、正常側のクロックゲーティング部を介してクロック供給を行わせる調停部30等の制御部を備えている。

(もっと読む)

クロック出力回路

【課題】クロック出力回路1にて電流消費を抑えつつ、周波数が安定したクロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

(もっと読む)

シリアル通信回路

【課題】低消費電力モードから復帰時にその受信シンボルでスキュー調整を実施することができ、通常通信状態への迅速な復帰を行う。

【解決手段】符号化された複数のレーンのシリアル受信信号からクロックの再生を行い、受信シンボルを各レーン毎に再生し、バイトアライン及びSP変換後、復号化して複数のレーンの受信シンボルを同一のクロックに同期した受信シンボルに変換して出力する物理層受信回路と、複数のレーンの受信シンボルに対してレーン間のシンボルスキューを調整するレーン間スキュー調整回路とを備えたシリアル通信回路において、所定の検出基準シンボルを受信シンボルからレーン毎に検出し、カウンタ回路により検出信号に応答して検出信号の計数を開始し、カウンタ値の選択信号に対応する遅延量だけ、物理層受信回路から出力される複数のレーンの受信シンボルに対して遅延させてレーン間のシンボルスキューを調整する。

(もっと読む)

周辺機器の省電力制御装置及び省電力制御プログラム

【課題】接続される外部接続基板の種類に対応した効率的な省電力制御を行うことを目的とする。

【解決手段】RISER基板10に、PCI Expressスイッチ20、クロックジェネレータ22、クロックバッファ24、及びRoot基板12からのクロックとクロックジェネレータ22のクロックとを切り換える切換SW26を設け、スイッチング素子28、30、32のオンオフを制御することにより、接続されるエンドポイント基板14から得られる、復帰要因を検知する基板であるか否かを表す検知信号及びポーリングする必要がある基板であるかを表すポーリング信号に基づいて、Expressスイッチ20、クロックジェネレータ22、及びクロックバッファ24への通電を制御すると共に、切換SW26の切換を制御する。

(もっと読む)

ディジタル信号処理回路及び車載用電子機器

【課題】ディジタル信号処理回路及び車載用電子機器において、消費電力を低減し、発熱量を低減する。

【解決手段】車載用電子機器に搭載されるディジタル信号処理回路は、クロック信号に同期して信号取込を行う入力段のフリップフロップ回路と、クロック信号に同期して信号取込を行う出力段のフリップフロップ回路と、順次処理を行う複数の組み合わせ回路が直列に接続されて構成されるとともに、クロック信号に同期して入力段のフリップフロップ回路から処理対象の信号が入力されて前記出力段のフリップフロップ回路に処理後の信号を出力する組み合わせ回路群と、クロック信号に同期して、組み合わせ回路毎に、クロック信号の1周期内において、駆動用電源の供給期間及び非供給期間を設けて駆動用電源の供給を行う電源供給回路と、を備える。

(もっと読む)

USBハブ及びUSBハブの制御方法

【課題】USBシステムにおける消費電力を低減することが可能なUSBハブを提供する。

【解決手段】USBハブ10は、上流USBポート11と、下流USBポート12と、動作クロックをUSB周辺機器30に供給するクロック端子13と、上流USBポート11とUSBホスト20との接続が切断された場合、または、USBホスト20から下流USBポート12に対しサスペンド要求を受信した場合、クロック端子13を介したUSB周辺機器30へのクロック供給を停止するハブコントローラ17と、を備えるものである。

(もっと読む)

11 - 20 / 895

[ Back to top ]