国際特許分類[G11C17/00]の内容

物理学 (1,541,580) | 情報記憶 (112,808) | 静的記憶 (17,688) | 一度だけプログラム可能なリードオンリメモリ;半永久的記憶装置,例.手でリプレースできる情報カード (379)

国際特許分類[G11C17/00]の下位に属する分類

磁気的または誘導的素子を用いるもの

容量的素子を用いるもの (6)

ダイオード素子を用いるもの (43)

半導体装置を用いるもの,例.バイポーラ素子を用いるもの (48)

その記憶内容が,結合素子の状態を永久に変えることによって連結リンクを選択的に設定,切断または変更することにより決められるもの,例.PROM (188)

国際特許分類[G11C17/00]に分類される特許

51 - 60 / 94

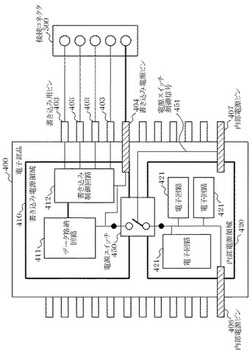

電子部品、基板、データ書き込みシステム、電源制御方法

【課題】 書き込み装置の書き込み電源のみで書き込みを可能とする。

【解決手段】内部電源をオフになると、書き込み電源領域410、および、内部電源領域420には、内部電源が供給されず、電源スイッチ450が、オフになり、書き込み電源領域410と内部電源領域420とは電源パターンが不導通になる。接続コネクタ500からの書き込み電源をオンになると、書き込み電源が、データ格納回路411、書き込み制御回路412に供給される。ここで、電源スイッチ450がオフなので、書き込み電源は、内部電源領域420には、供給されない。接続コネクタ500、書き込み用ピン403を経由し、書き込み制御情報、書き込みデータが書き込み制御回路412に入力される。書き込み制御回路412は、書き込み制御情報に基づき、書き込みデータをデータ格納回路411に書き込む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置を製造する際の信頼性試験を適切に行うこと。

【解決手段】半導体装置の製造方法は、半導体チップ(2、2a〜2d)が有する全ての通常メモリセルに対する冗長メモリセルで置換された通常メモリセルの割合を示す置換率の高低に基づいて前記半導体チップに対して行うべき信頼性試験の条件を決定するステップ(S31、S50)を具備する。置換率の高低に基づいて信頼性試験の条件を決定することで半導体装置を製造する際の信頼性試験が適切に行われる。より具体的には、置換率が高いすなわち程度の悪い半導体チップに対しては入念な信頼性試験を行い、置換率が低いすなわち程度の良い半導体チップに対しては比較的簡易な信頼性試験を行うことが可能になる。したがって、信頼性試験の所要時間と半導体装置の製造コストとが削減される。

(もっと読む)

半導体不揮発性メモリ回路および装置

【課題】余分なインターフェース回路等を必要とせず、記憶情報を光学的に設定して電気的に書き込むことができる不揮発性メモリ回路および装置を提供する。

【解決手段】第1のインバータ21および第2のインバータ22からなるフリップフロップ20と、前記フリップフロップの非反転出力端子Cと接地線GNDとの間に接続された第1のMIS型トランジスタ11と、前記フリップフロップの反転出力端子C_と前記接地線との間に接続された第2のMIS型トランジスタ12と、前記第1のMIS型トランジスタおよび第2のMIS型トランジスタのゲートに接続された書込ワード線WLWとを備えた不揮発性メモリ回路であって、前記フリップフロップの前記非反転出力端子と前記接地線との間に接続された第1のフォトダイオード41と、前記フリップフロップの前記反転出力端子と前記接地線との間に接続された第2のフォトダイオード42とを有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】本発明は、データの再書き込みが不可能な不揮発性半導体記憶装置において、誤動作により回路を構成する素子が破壊されるのを防止できるようにする。

【解決手段】たとえば、読み出し動作時に、書き込み動作指示信号WEが異常入力されたとする。すると、書き込み動作制御組み合わせ回路20は、VDD(たとえば、1.5V)なる書き込み制御信号SLを出力し、書き込みゲート13を活性化させる。一方、上記書き込み動作指示信号WEの異常入力が、読み出し動作制御順序回路30の非同期リセット端子(reset)に入力されると、読み出し動作制御順序回路30は、直ちに、イコライズ信号EQL、参照電位制御信号REFE、および、差動アンプ制御信号SAEを非活性状態とし、読み出し動作を停止する。

(もっと読む)

アドレスデコーダおよびその検査装置

【課題】オープン系の故障に起因した多重選択の不具合を簡易に検出し得るアドレスデコーダおよびその検査装置を提供する。

【解決手段】アドレスデコーダ10では、MOSトランジスタN11〜N14のそれぞれについてMOSトランジスタN11〜N14のドレイン側またはソース側の少なくとも一方でアースEとデコード出力端子Poとの間に抵抗R10〜R13を介在させ、またこのデコード出力端子Poを抵抗R21を介して電源電圧Vddに接続し、さらにデコード出力端子Poを非反転入力に接続するとともにMOSトランジスタN11〜N14がすべてオン状態にあるときの抵抗R10〜R13による並列合成抵抗と抵抗R21とによる電源電圧Vddの分圧よりも高い電位がこの非反転入力に入力されたことを検出可能なコンパレータCp10を備える。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にする。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリに供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまたは書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにすることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込みにおいて、消費電流を一定にできる。

(もっと読む)

半導体集積回路

【課題】ノイズ耐圧を向上させる。

【解決手段】レイアウト的に内部で長く細く、かつ電源ラインやGNDラインに近接している一番センシティブなノイズ検知ラインS010の電圧をシステムクロックS001で取り込む。レイアウト固定ロジック012を搭載し、ノイズ検知ラインS010の電圧がノイズ等により、変化した場合のみ、レイアウト固定ロジック012から第1検知データS102が“L”出力される。第1検知データS102によりメモリ020の回路動作を変化させることで、ノイズ耐圧向上が可能となる。

(もっと読む)

半導体装置

【課題】製造時間を短縮できる半導体装置を提供する。

【解決手段】まず、ステップS1において、127ビット長の元データ(ビット列)[126:0]が入力される。次に、ステップS2へ進み、ステップS1で入力されたビット列[126:0]のうち”1”であるビットが半分より多い(すなわち64個以上)であるかどうかを判定する。そして、64個以上である場合にはステップS3へ進む。次に、ステップS3において、ビット列[126:0]を反転させるとともに、反転ビットであるビット[127]=1とする。そして、ステップS5へ進む。次に、ステップS5において、ビット列[126:0]およびビット[127]にそれぞれ対応するヒューズをLTする。

(もっと読む)

ナンドフラッシュメモリ素子のチャネルブースティング電圧の測定方法

【課題】ナンドフラッシュメモリ素子のプログラムディスターバンス特性を評価するためのチャネルブースティング電圧の測定方法を提供する。

【解決手段】チャネルブースティング電圧の特定方法は、パスディスターバンスのしきい値電圧測定段階(S201〜S209)、プログラムディスターバンスのしきい値電圧測定段階(S211〜S219)及びチャネルブースティング電圧測定段階(S221及びS223)を含み、具体的には、消去状態の選択されたセルの第1のしきい値電圧を測定する段階と、消去状態の非選択されたセルの第2のしきい値電圧を測定する段階と、プログラム動作時に印加されるパスバイアス時の第2のしきい値電圧を検出し、第1のしきい値電圧が測定される時に印加された第1のパスバイアスのレベルを検出する段階、及び検出された第1のパスバイアスのレベルを用いてチャネルブースティング電圧を測定する段階を含む。

(もっと読む)

半導体試験方法及び装置

【課題】フラッシュメモリなどの半導体メモリについて、データの書込/消去が正常にできた場合の回数を測定できるようにする。

【解決手段】データの書込/消去が正常にできた場合の回数又はできなかった場合の回数を測定し、それをメモリなどに記憶しておき、試験終了後にその回数を解析することによって、被試験半導体デバイスが規定よりも大幅に少ない回数書込/消去の可能な(すなわち書込/消去を高速に行うことができる)高性能のデバイス、又は規定の回数ぎりぎりで書込/消去の可能な通常性能のデバイスであるというようなグレード分類を行う。

(もっと読む)

51 - 60 / 94

[ Back to top ]